# MILLER COMMUNICATIONS

STUDY, SPECIFICATION AND FABRICATION OF SIGNAL PROCESSING SYSTEM FOR TRANSPONDED EMERGENCY LOCATOR TRANSMITTER SIGNALS

(PHASE I)

FINAL REPORT

The work reported here was performed by Miller Communications Systems Limited for Communications Research Centre of the Department of Communications (Contract Officer M.D. Lambert) under DSS Contract No. OST76-00044

December 1976

Industry Canada Library - Queen

AOUT 1 6 2012

Industrie Canada Bibliothèque - Queen

Lambert

Se'd for in D. D.

DD 4618306 DL 4618319

# TABLE OF CONTENTS

|          |       | ·                                                                |     | PAGE    |

|----------|-------|------------------------------------------------------------------|-----|---------|

| EXEC     | UTIVE | SUMMARY                                                          |     | i-vi    |

| I.       | RECE  | IVER SYSTEM DEFINITION                                           |     |         |

|          | r.1   | Introduction                                                     | ,   | I - 1   |

|          | T. 2  | System Requirements                                              |     | I - 3   |

|          | I.3   | Constraints on Search Process                                    |     | I-6     |

|          | I.4   | Constraints on Measurement Process                               |     | I-10    |

|          | I.5   | Effects of ELT Modulation                                        |     | I - 1.7 |

|          |       | I.5.1 Uplink doppler                                             |     | I-17    |

|          |       | I.5.2 Chirp Modulation                                           |     | I-19    |

|          |       | I.5.3 Pulsed ELT's                                               |     | I-22    |

|          |       | I.5,4 Incidental FM                                              |     | I - 23  |

|          | I.6   | Interference Effects of ELT Carriers Beyond 100 Hz<br>Separation |     | I-27    |

|          | I.7   | Control of Receiver Processing                                   | •   | I-28    |

|          |       | I.7.1 Identification and Tracking                                |     | I-28    |

|          |       | I.7.2 Signal Acquisition and Measurement Strategy                |     | I-29    |

|          |       | I.7.3 Software Elements                                          |     | I - 33  |

|          | I.8   | Recommendations                                                  |     | I - 35  |

|          | I.9   | References                                                       |     | I-36    |

| T 01     | GM MI | WEGIG AND ANAINGEG OF DEGREES ONORTH                             | . • | •       |

| II.      |       | HESIS AND ANALYSIS OF RECEIVER SYSTEM                            |     | T T 1   |

|          |       | Introduction                                                     |     | II-1    |

|          | 11.4  | Phase Lock Loop Analysis                                         | ·   | II-2    |

|          |       | II.2.1 Systems Constraints                                       |     | II-3    |

|          |       | II.2.2 The Process of Lock Acquisition                           |     | II-7    |

|          |       | II.2.3 Lock Detection                                            |     | II-12   |

|          |       | II.2.4 Signal Acquisition and Tracking                           |     | II-19   |

|          |       | 1) Step Timing                                                   |     | II-19   |

|          |       | 2) Noise Constraints                                             |     | II-21   |

| •        |       | 3) Unlocked Conditions                                           |     | II-22   |

|          |       | 4) Adjacent ELT Carriers                                         |     | II-25   |

|          |       | 5) Acquisition of New ELT's                                      |     | II-30   |

| <b>^</b> |       | 6) Missed Measurements                                           |     | II-33   |

|          |       | 7) Loss of Lock  9) Effects of Signal Medulation                 |     | II-35   |

|          |       | 8) Effects of Signal Modulation                                  |     | II-37   |

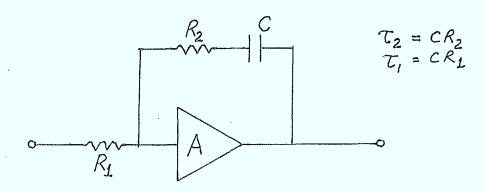

|     | 3      | II,2,5 Third Order PLL's                             | II = 39 |

|-----|--------|------------------------------------------------------|---------|

| Li  | ]      | II,2,6 Design Considerations for Second Order Loops  | II-42   |

|     |        | 1) Filter Type                                       | II - 42 |

|     |        | 2) Filter Parameters                                 | II-47   |

|     |        | 3) Filter Switching                                  | II49    |

|     | I      | II.2.7 Stability of Heterodyne Loop                  | II-50   |

|     | I      | T.2.8 Measurement by FM Demodulation                 | II-53   |

|     | I      | II.2.9 All Digital PLL                               | II-55   |

|     | II.3 F | Receiver Configurations and Performance Evaluation   | II-59   |

|     | I      | II.3.1 Summary of Results to Date                    | II-59   |

|     | ,      | II.3.1.1 Receiver Types A and B                      | II-59   |

| •   |        | II.3.1.2 Searching and Detecting                     | II-62   |

|     |        | II.3.1.3 Measurement and Tracking                    | II-66   |

|     |        | II.3.1.4 Recommended Type AB Receiver                | II-81   |

|     | Ī      | I.3.2 Microprocessor Control                         | II-85   |

|     | II.4 R | References                                           | II-93   |

|     | •      |                                                      |         |

| III | ENGINE | ERING AND ECONOMIC EVALUATION OF CANDIDATE RECEIVERS |         |

| (f) | III,1  | Introduction                                         | III-1   |

|     | III.2  | Receiver Configuration                               | III-1   |

|     | III.3  | Detailed Assessment of Receiver Elements             | III-2   |

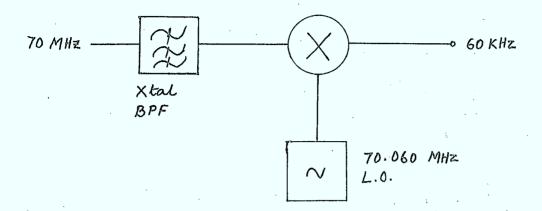

|     |        | III.3.1 Choice of Frequency Plan                     | III-2   |

|     | III.4  | The Down Converter                                   | III-6   |

|     | •      | III.4.1 Make or Buy                                  | III-6   |

|     |        | III.4.2 Design Tradeoffs                             | III-6   |

|     |        | a) Single Down Conversion                            | III-6   |

|     |        | b) Double Down Conversion                            | III - 8 |

|     |        | III.4.3 Conclusions                                  | III-9   |

|     | III.5  | The Stepper Receiver                                 | III-10  |

|     |        | III.5.1 The Synthesizer                              | III-10  |

|     |        | III.5.1.1 Make or Buy                                | III-10  |

|     |        | III,5,2 The Narrow Band IF Filter                    | III-13  |

|     |        | III.5,2,1 Make or Buy                                | III-13  |

|     |        | III.5.3 Phase Locked Loop                            | III-13  |

. .

< ·

|   |          | III,5,3,1 Make or Buy                        | •  | III-13   |

|---|----------|----------------------------------------------|----|----------|

|   |          | III,5,3,2 Technical Tradeoffs                |    | 111-14   |

|   |          | i) IC Phase Locked Loops                     |    | III-14   |

|   |          | ii) Phase Detector                           |    | III - 14 |

|   |          | iii) VCO                                     |    | III-15   |

|   |          | iv) Loop Filter                              |    | III-16   |

|   |          | v) Lock Detector                             |    | 111-16   |

|   |          | TTT.5.3.3 Capital Cost                       | •  | III-17   |

|   | ,        | TTT.5.3.4 Engineering Costs                  |    | III-17   |

| I | III.6 T  | The Sweeper Receiver                         |    | III-18   |

|   | 1        | III.6.1 Make or Buy                          |    | III-18   |

|   | 1        | III.6.2 Technical Tradeoffs                  |    | II.I-18  |

|   | I        | III.6.3 Capital Costs                        |    | III-19   |

|   | Ι        | III.6.4 Engineering Costs                    |    | III-19   |

| I | II.7 C   | Conclusions on Stepper vs Sweeper            |    | III - 20 |

| 1 | T 8.II   | The Frequency Counter                        |    | III-21   |

|   | 1        | III.8.1 Make or Buy                          |    | III-21   |

|   | I        | III.8.2 Technical Tradeoffs                  |    | III-23   |

|   | I        | III.8.3 Conclusions                          |    | III-23   |

| Ī | II.9 Ţ   | Type 'A' vs Type 'B' Receiver                |    | III-25   |

|   | I        | III.9.1 General                              |    | III-25   |

|   | I        | III.9.2 The Sweeper Receiver                 |    | III-25   |

|   | I        | III.9.3 Stepper Receiver                     |    | III-26   |

|   | · I      | III.9.4 Conclusions                          |    | III-27   |

| I | II.10 C  | Overall Conclusions                          |    | III-28   |

| Ε | EFINITI  | ION OF PROPOSED RECEIVER                     |    |          |

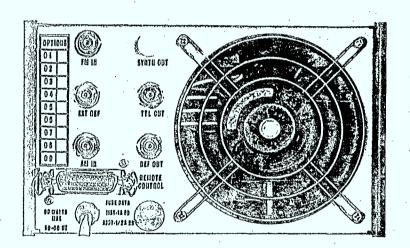

| I | V.1 Rec  | ceiver System Description                    |    | IV-1     |

|   | IV.      | .1.1 Receiver System Hardware                |    | IV-1     |

|   | IV.      | .1.2 Receiver Operation                      |    | IV-3     |

|   |          | In Type A                                    |    | IV-3     |

|   |          | In Type B                                    |    | IV-4     |

|   | IV.      | .1.3 Computer Software and Computer Interfac | es | IV-5     |

| I | V.2 Rec  | ceiver Subsystems                            |    | IV = 7.  |

| Ι | V.3 Rec  | ceiver Performance                           |    | IV-12    |

| T | Tr A Dot | ta Stanad in Computar for Transmission to Pa |    | TW-16    |

IV

# APPENDIX A - DESIGN OF PLL'S FOR SIGNAL ACQUISITION

|       | $\cdot$                                         | PAGE    |

|-------|-------------------------------------------------|---------|

| A.1   | Introduction                                    | A-1     |

| A.2   | Phase Detection                                 | . A - 3 |

| A.3   | PLL Operation                                   | A - 4   |

|       | A.3.1 Signal Acquisition                        | A - 4   |

|       | A.3.2 Signal Tracking                           | . A-8   |

|       | A.3.2.1 Output Signal                           | A - 8   |

|       | A.3.2.2 Tracking a Frequency Ramp               | A - 8   |

|       | A.3.2.3 Cycle Skipping                          | A - 9   |

|       | A.3.3 Effect of Signal Fades                    | A - 9   |

|       | A.3.4 Effect of Carrier Phase Noise             | A - 10  |

|       | A.3.5 Changing the Loop Bandwidth               | A-11    |

|       | A.3.6 Effect of Sweep Voltage on Loop Operation | A-11    |

| A . 4 | Coherent Lock Detection                         | A-12    |

| A.5   | PLL Design                                      | A-14    |

| -     | A.5.1 Configuration                             | A-14    |

|       | A.5.2 The Phase Detector                        | A-16    |

|       | A.5.3 The Loop Filter and Sweep Circuitry       | A-16    |

|       | A.5.4 Changing the Loop Natural Frequency       | A-17    |

|       | A.5.5 Phase Shift for the Coherent Detector     | A-18    |

|       | A.5.6 Limiters                                  | A-19    |

|       | A.5.7 Input Frequency Range                     | A - 20  |

|       | A.5.8 Choice of VCO Type                        | A-21    |

| A 6   | References                                      | Δ-22    |

# APPENDIX B - DIGITAL SIGNAL PROCESSING TECHNIQUES

| B.1 | The Discrete Fourier Transform (DFT)              | B - 1 | Ĺ   |

|-----|---------------------------------------------------|-------|-----|

| B.2 | DFT on Staggered Blocks                           | B - 5 | 5   |

| B.3 | Low Pass Digital Filters with Decimation          | B - 3 | 10  |

| B.4 | Digital Phase Lock Loops with Decimation          | B - 1 | 15  |

| B.5 | Quantization Effects in FFT's and Digital Filters | В-3   | 17  |

|     | B.5.1 Effects in Digital Filters                  | B - 2 | 21  |

| ŕ   | B.5.2 Effects in FFT's                            | B - 2 | 2 2 |

| B.6 | References                                        | B - 2 | 27  |

# LIST OF FIGURES

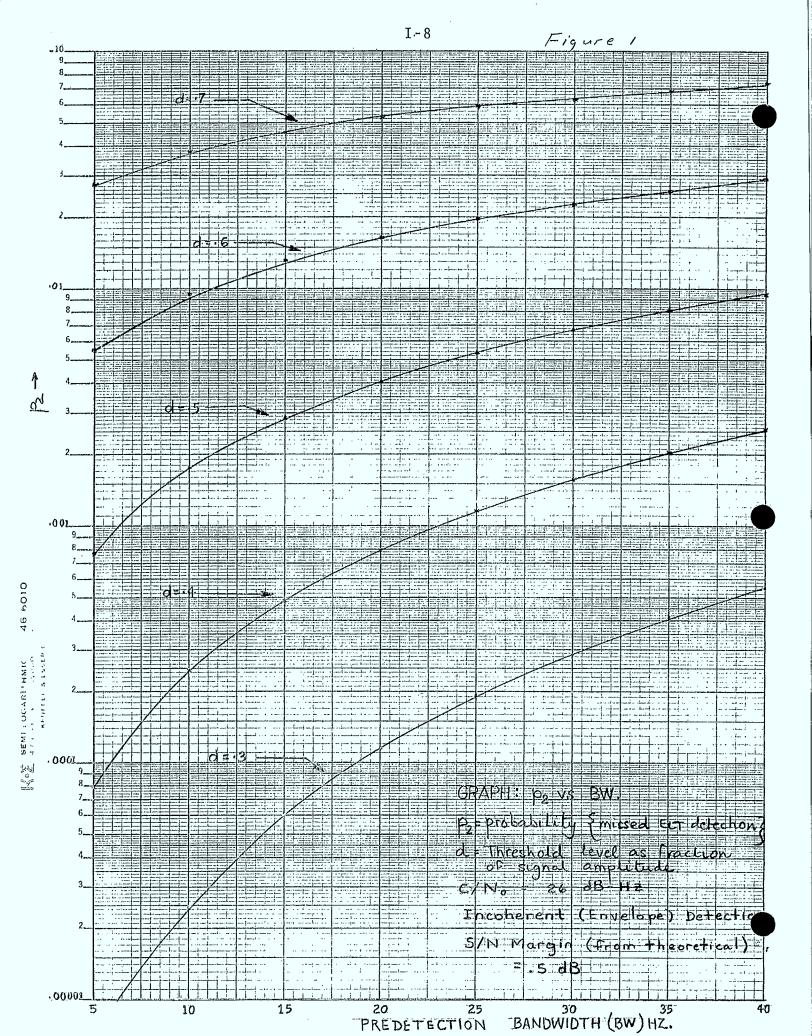

|   | FIGURE | 1  | ;        | Missed ELT Incoherent Detection Probability vs<br>Noise Bandwidth                                                                 | I ~ 8        |

|---|--------|----|----------|-----------------------------------------------------------------------------------------------------------------------------------|--------------|

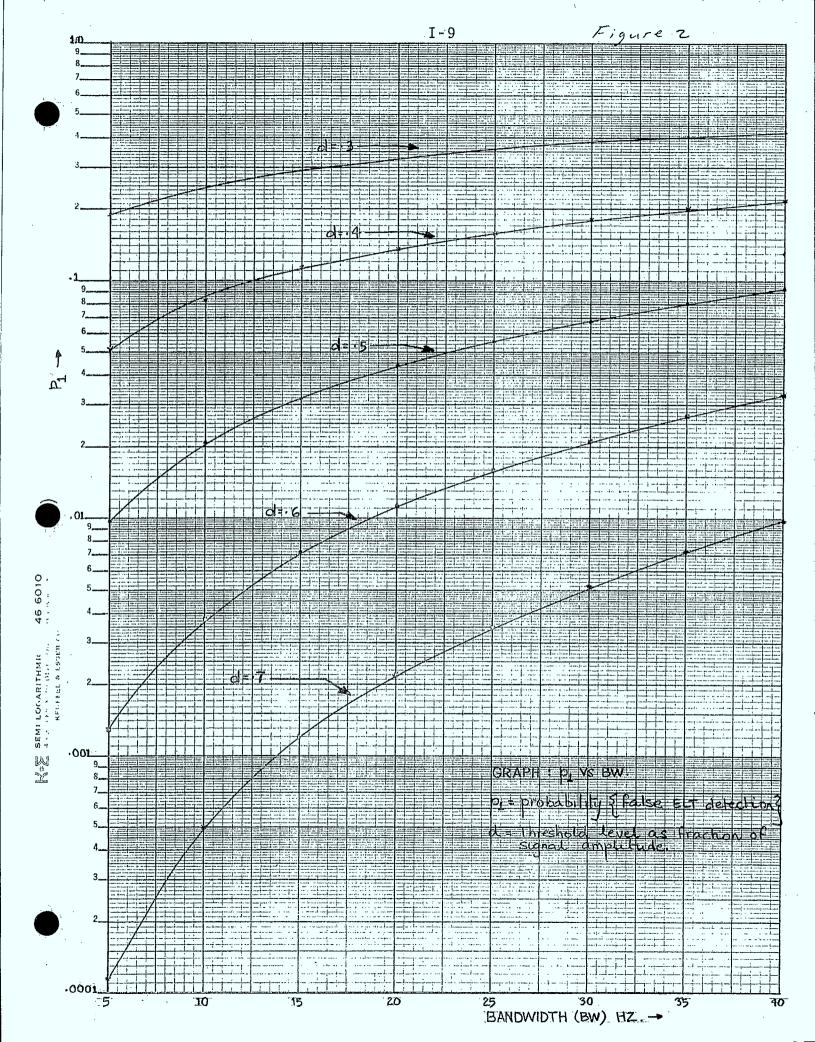

|   | FIGURE | 2  | :        | False ELT Incoherent Detection Probability vs Noise Bandwidth                                                                     | I <b>-</b> 9 |

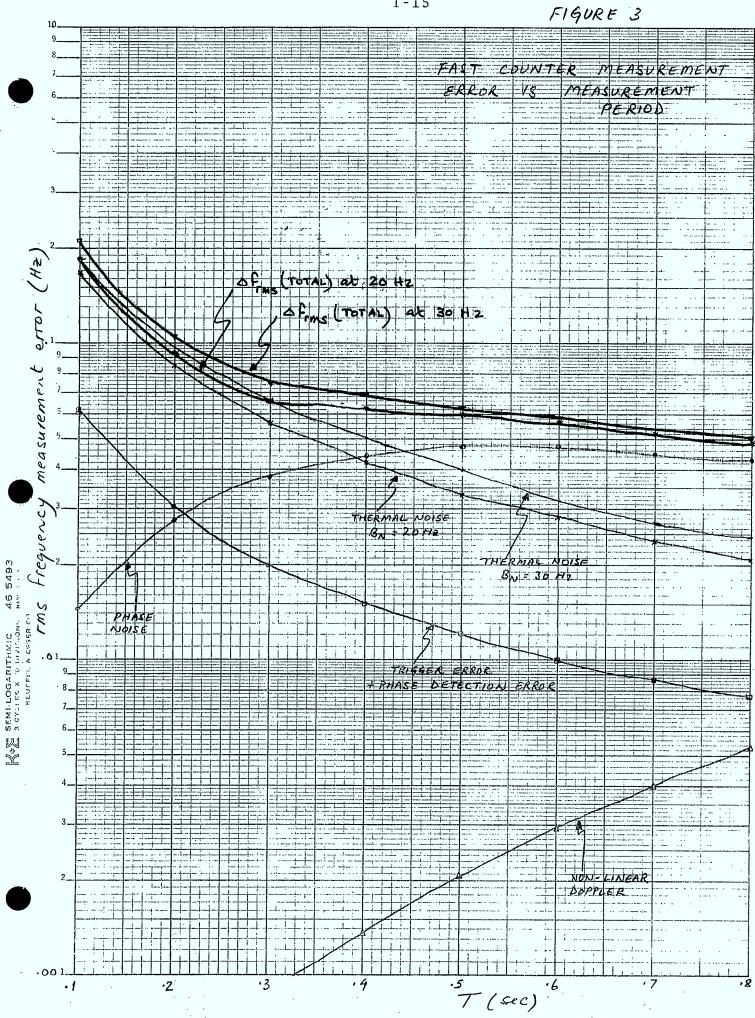

|   | FIGURE | 3  | :        | Fast Counter Measurement Error vs Measurement<br>Period                                                                           | T-15         |

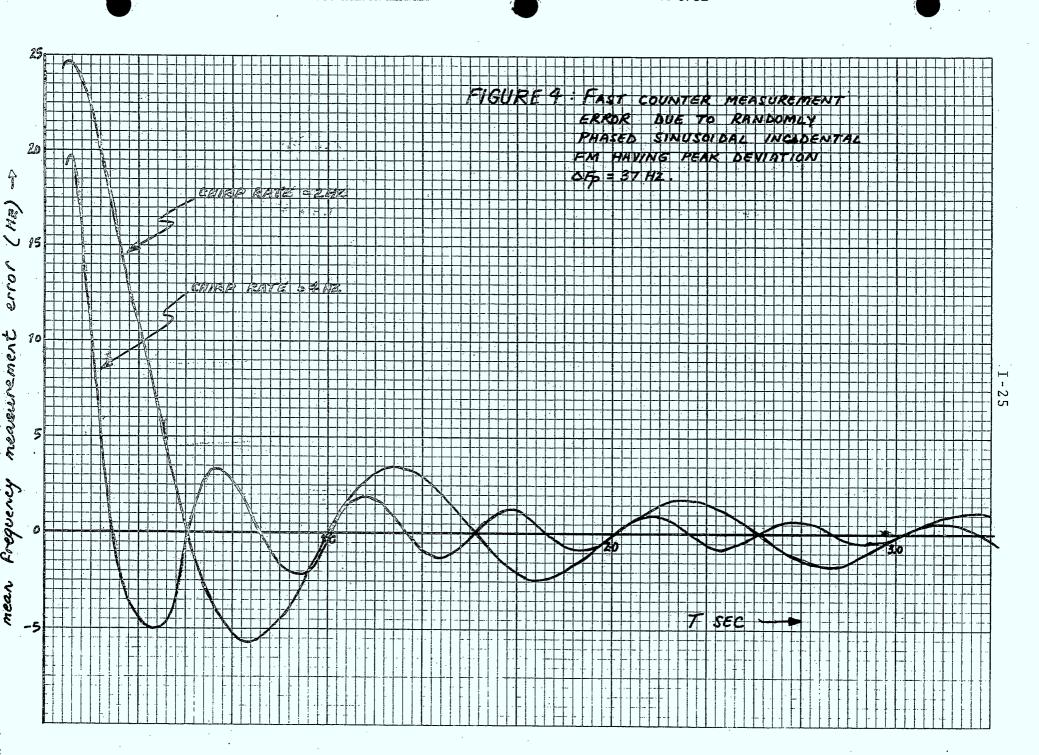

|   | FIGURE | 4  | :        | Fast Counter Measurement Error Due to Randomly Phased Sinusoidal Incidental FM having peak Deviation $\Delta f_p = 37 \text{ Hz}$ | T - 25       |

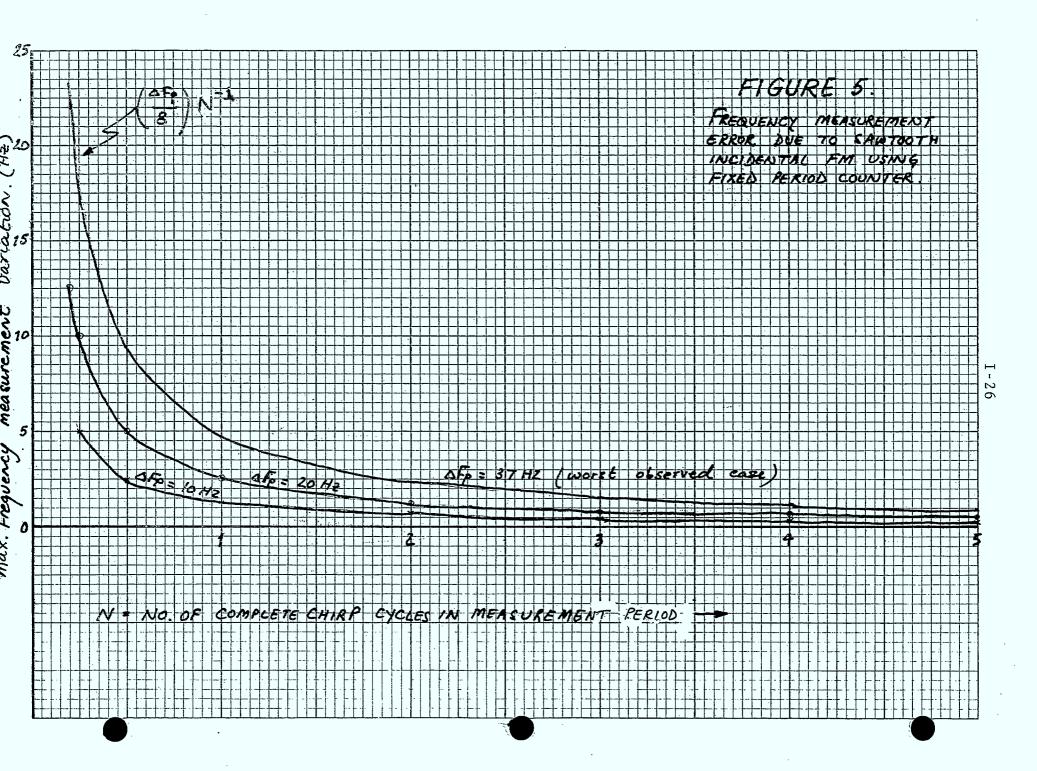

|   | FIGURE | 5  | :        | Frequency Measurement Error Due to Sawtooth<br>Incidental FM Using Fixed Period Counter                                           | I~26         |

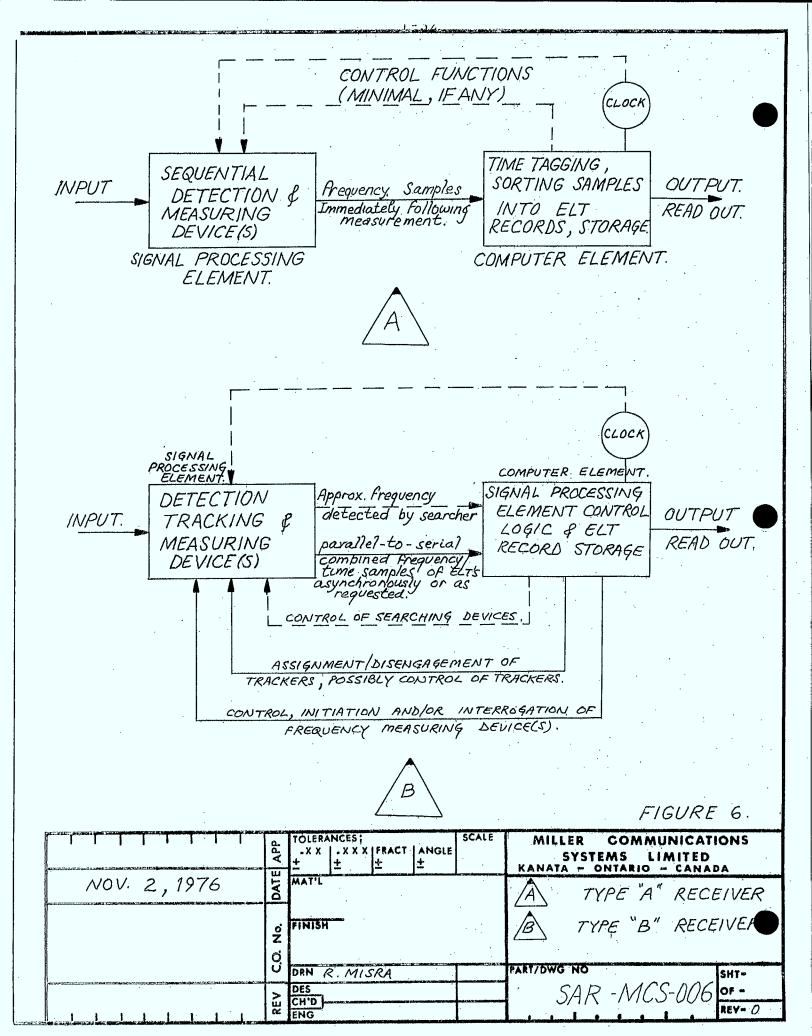

| ) | FIGURE | 6  | <b>:</b> | Type A and Type B Receiver Conceptual Block Diagrams                                                                              | T-32         |

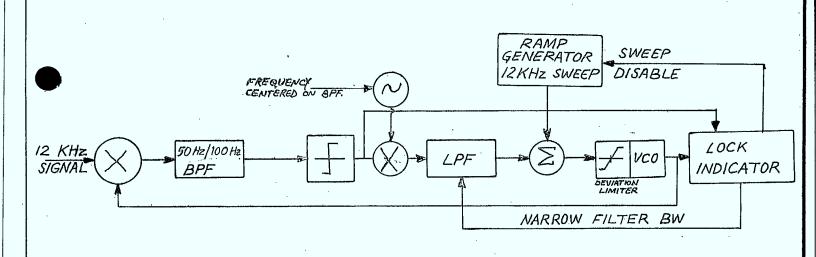

|   | FIGURE | 7  | :        | Swept and Stepped Search/Detect Circuits                                                                                          | II-63        |

|   | FIGURE | 8  | ;        | Analog and Hybrid Track/Frequency Measurement Circuits                                                                            | II-64        |

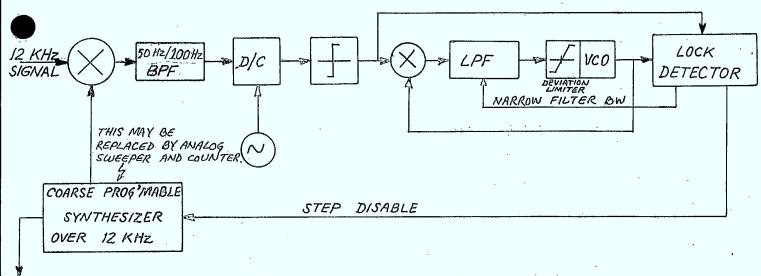

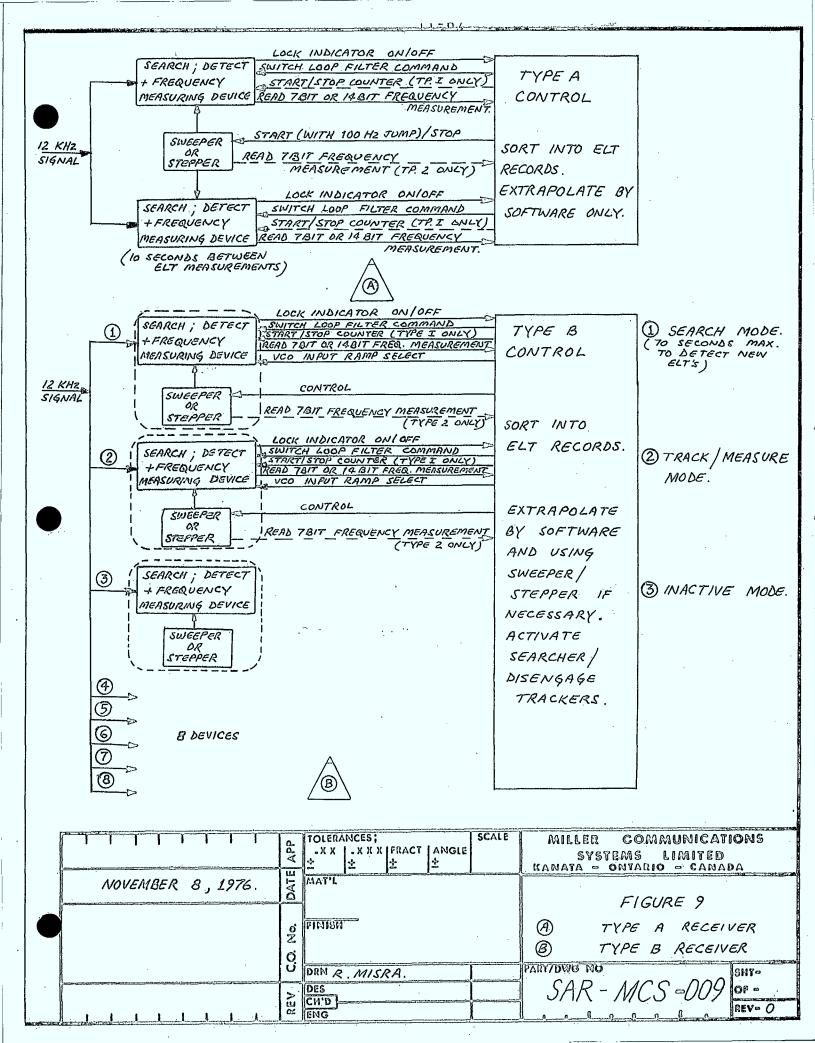

|   | FIGURE | 9  | :        | Type A and Type B Receiver Functional Block Diagrams                                                                              | II-67        |

|   | FIGURE | 10 | <b>:</b> | Type AB Receiver                                                                                                                  | II-68        |

|   | FIGURE | 11 | :        | PDP-11/03 Input Output Data Format (DRV-11)                                                                                       | II-88        |

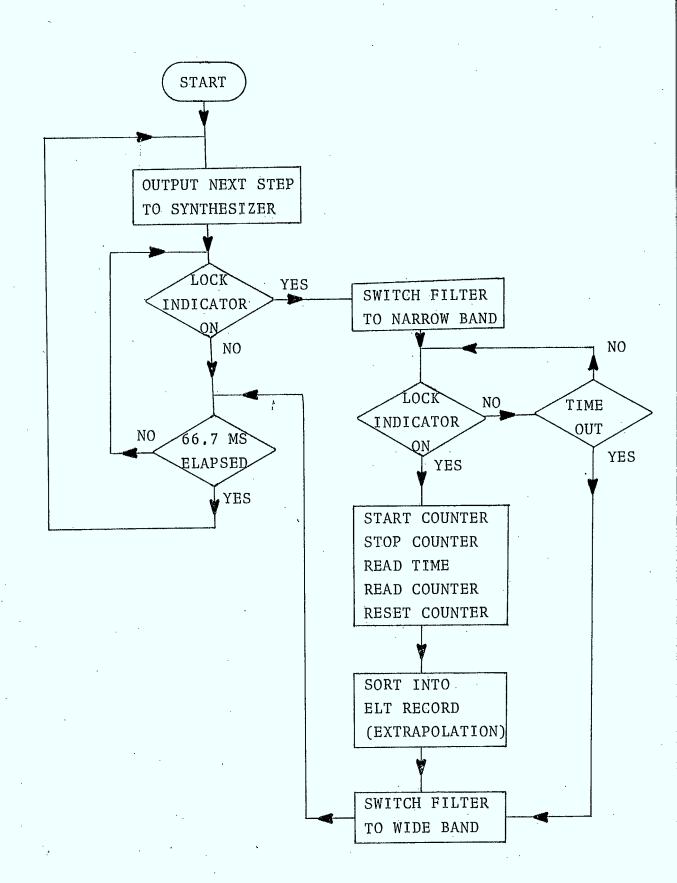

|   | FIGURE | 12 | :        | Flow Chart for Type A Software                                                                                                    | II-89        |

|   | FIGURE | 13 | ;        | Typical Logical Sequence for Type A Operation                                                                                     | II-90        |

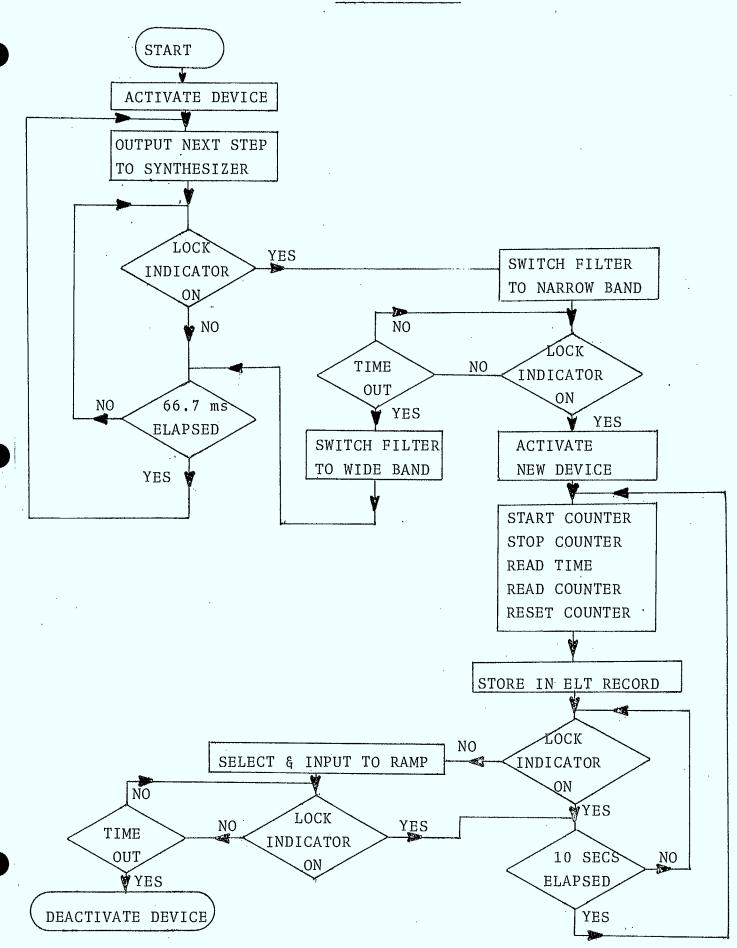

| FIGURE 14: | Flow Chart Type B Software                    | II ~ 91 |

|------------|-----------------------------------------------|---------|

| FIGURE 15: | Typical Logical Sequence for Type B Operation | II-92   |

# LIST OF TABLES

| TABLE 1: | Candidate PLL Receiver Operating Modes                                         | I-60  |

|----------|--------------------------------------------------------------------------------|-------|

| TABLE 2: | Specification of Search/Detect/Measuring Device                                | IV-9  |

| TABLE 3: | Anticipated Receiver Performance                                               | IV-13 |

| TABLE 4: | Degrading Effects of Carrier Pulsing and Incidental FM on Receiver Performance | IV-15 |

| TABLE 5: | ELT Data Stored in Computer for Transmission to Base                           | IV-16 |

#### EXECUTIVE SUMMARY

This report is the result of a comprehensive study of the requirements and alternative solutions for a signal processing system to identify and measure the frequency of up to eight ELT signals transponded through a Search and Rescue satellite. All conditions of the Statement of Work with regard to the Study Phase have been met, including:

- careful definition of the system requirements and constraints

- survey and evaluation of possible operational techniques, including analog, digital and hybrid alternatives

- development and detailed study of several promising candidate

receiver types with all analysis required to determine key system

parameters and estimate performance

- careful consideration of engineering and economic factors associated with the implementation of the receiver

- definition of a recommended receiver system to be designed and built in Phases 2 and 3.

The report is divided into four parts with two supporting Appendices as follows:

- I RECEIVER SYSTEM DEFINITION

- II SYNTHESIS AND ANALYSIS OF RECEIVER SYSTEM

- III ENGINEERING ECONOMIC EVALUATION OF CANDIDATE RECEIVERS

- IV DEFINITION OF PROPOSED RECEIVER

APPENDIX A - DESIGN OF PLL'S FOR SIGNAL ACQUISITION

APPENDIX B - DIGITAL SIGNAL PROCESSING TECHNIQUES

Part I carefully remexamines all receiver performance specifications and the characteristics of the ELT signals themselves in order to bound the range of reasonable solutions and in fact verify that a solution is possible. Part I concludes that two basic receiver systems are feasible and merit in-depth investigation. The first, labelled Type A, employs one or more devices scanning the band and stopping only to measure the frequency of carriers detected. Good measurements can be sorted by software into ELT records unambiguously using known bounds on the first and second derivative of the ELT doppler characteristic. The second receiver configuration, labelled Type B, employs eight devices to track and measure each ELT detected. This approach requires more hardware and is clearly more complex from the control standpoint, but offers a greater ability to obtain measurements under more severe noise or interference conditions following initial detection. In neither case, however, does the receiver attempt to verify that the sinusoid

being measured is in fact an ELT.

Given the requirements of and constraints on the receiver system presented in Part T, Part TI identifies and evaluates alternate schemes of realizing the functionally distinct Type A and Type B receivers. Performance, cost, operational flexibility, and technical risk are all taken into consideration in assessing alternate receiver designs.

Much of Part II is devoted to analysis of the detection and measurement processes, key elements of any Type A or Type B receiver.

The phase locked loop (PLL) is the preferred device for both detecting and acquiring an ELT prior to measurement, and it is desired to

- 1. maximise the sweep rate in the search mode while maintaining low mis-detection and false alarm probabilities

- 2. minimize the acquisition time while ensuring the loop provides sufficient noise filtering to accurately measure frequency

- 3. ensure the PLL can track an ELT at the maximum doppler rate with the greatest possible noise and interference rejection

Part II determines that a second order PLL with loop bandwidth switching upon ELT detection can be designed to meet the requirements, and that two such devices operating in parallel in a Type A mode should be able to measure the frequencies of up to 8 ELT's at 10

second intervals.

The rms error in the measured frequency is estimated under nominal conditions, and the degrading effects of interfering carriers and sidebands, carrier pulsing, incidental FM, and phase noise are examined. Incidental FM generated in some ELT transmitters seriously degrades performance. PLL intervention is required to "track" pulsed ELT's and moderate degradation, statistical in nature, can be expected with pulsed ELT's unless elaborate detection and measurement techniques - not recommended in an initial receiver implementation are employed.

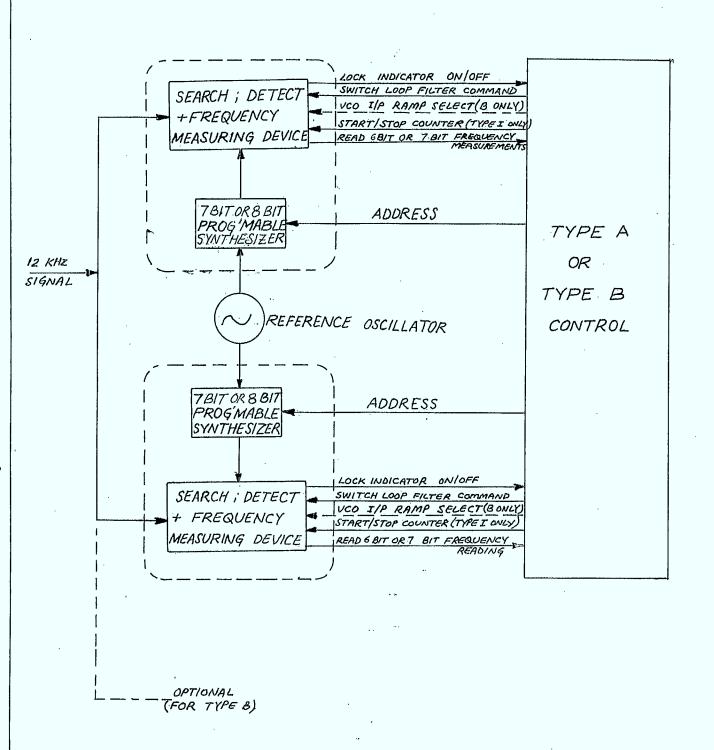

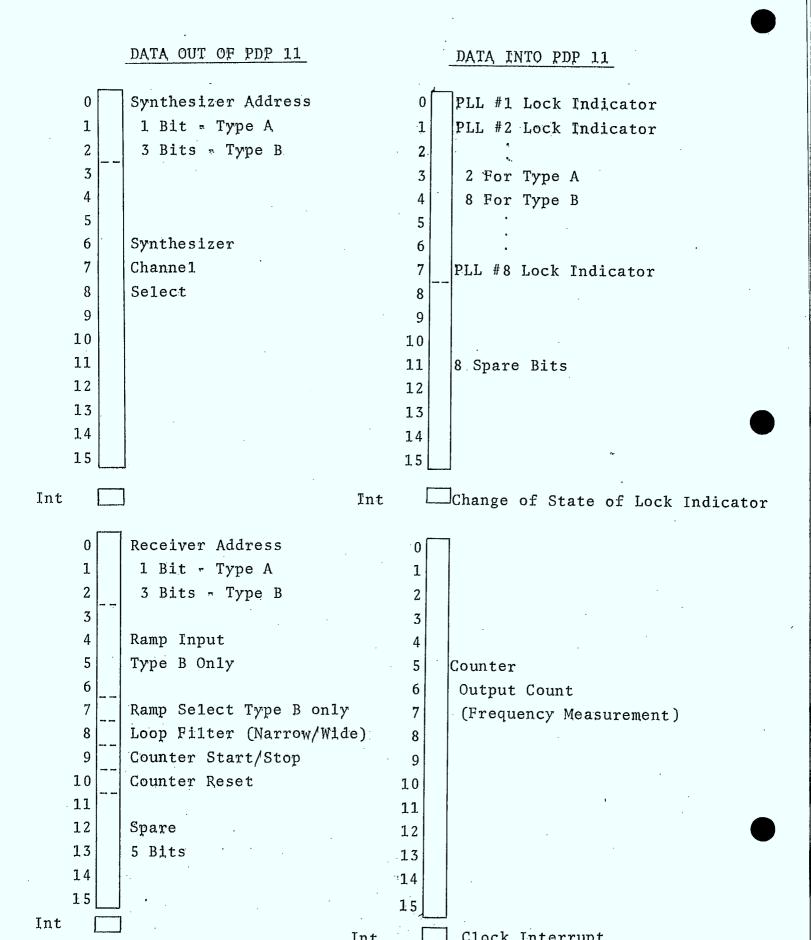

Having examined in detail the fundamental signal processing elements of the receiver - detection, tracking and frequency measurement - Part II considers alternative overall receiver configurations. These are identified and the advantages and disadvantages of each stated. Section II.3.1.4 strongly recommends on the basis of simplicity and flexibility a receiver which employs two identical, independently controlled, frequency stepping "test instruments" capable of searching for, detecting, and measuring ELT's, interfaced with a PDP-11 microprocessor. Such a receiver can be operated in either a Type A or limited Type B mode with appropriate microprocessor software, and expansion to a full capability Type B receiver is accomplished by adding six more devices. (The Type B program and control interface can be designed to accommodate this addition). The input/output for each test instrument is rather simple, consisting of the incoming

noise filtered signal at appropriate centre frequency, an outgoing frequency measurement, and four logical control variables, namely:

- i lock indicator status

- ii stepper (synthesizer) frequency

- iii PLL loop filter bandwidth (2 states)

- iv counter start/stop command .

The critical timing parameters (sweep rate, allowed acquisition time, and measurement period), which can only be finalized experimentally, are under complete control of the computer and can easily be varied.

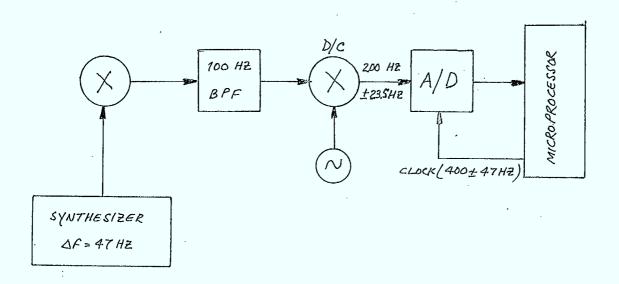

Since the signal-to-noise ratio required to achieve satisfactory performance trades off with the allowable sweep speed, and since neither can be quantified exactly at this time, it is also recommended that the instrument be able to operate with either 47 Hz steps/50 Hz predetection bandwidth or 94 Hz steps/100 Hz pre-detection bandwidth. This requires only that two sets of band pass and PLL loop filters be designed and built.

While priority will be given to developing a working Type A receiver, it is clear that extending its capability to the Type B mode consists only of developing the appropriate real time program. This task, however, should not be underestimated.

Part III of the report considers the candidate receivers from the standpoints of ease of implementation and hardware cost. A breakdown into major subsystems is given, design tradeoffs are identified and quantified, and potential problem areas investigated. The results of Part III reinforces the recommendations of Part II, and concludes that the Type AB receiver is realizable within the time frame and budget constraints of this contract.

Part IV gives a concise specification of the Type AB receiver, and summarizes its expected performance under a variety of input conditions. This section will serve as the approved baseline as we enter the detailed design and implementation phases.

Appendices A and B are the results of background studies commissioned early in Phase I to get a handle on Phase Locked Loop operation and the availability and performance of digital processing hardware which might find application in the Sarsat receiver.

Lists of references which proved useful over the course of the study are also included on a chapter by chapter basis.

#### I. RECEIVER SYSTEM DEFINITION

#### I.1 Introduction

As part of its program to investigate the application of a low orbiting satellite to assist in locating downed aircraft, the Canadian Government's Department of Communications has awarded a contract to Miller Communications to study and develop a receiver system capable of detecting and measuring to an accuracy of 1 Hz the Doppler frequencies of up to eight Emergency Locator Transmitter (ELT) signals nominally sharing the same 12 kHz frequency band. The work is to be carried out in three phases:

- (i) study to survey and evaluate possible operational techniques for ELT access recognition and signal reduction

- (ii) performance specification and detailed design for the receiver system

- (iii) breadboard design and fabrication of an approved developmental model

The problem of multiple access by ELT's can be broken into two parts. First, there is a requirement to continuously examine the downlink transmission from the SARSAT satellite to monitor the occurrence of ELT carriers. Secondly, when an ELT is found, its

carrier frequency must be measured and logged at regular intervals to a time-frequency accuracy of better than  $\pm 100$  msec,  $\pm 1$  Hz, at an operating  $C/N_o$  of 26 dB-Hz. It has been both theoretically and experimentally shown that this permits the position of the downed aircraft to be determined within several miles. Several types of candidate receivers have been proposed for examination, employing one or more of the following candidate analog and digital elements:

- swept filter or phase lock loop (PLL) detector(s)

- tracking narrow band PLL(s)

- frequency counter(s) and synthesizer(s)

- digital hardware processing elements such as Fast Fourier Transform (FFT), digital PLL(s), digital filter(s) and interpolators, etc.

- microprocessor or minicomputer used for real time software processing and data input/output.

An output record of frequency vs time is required at the completion of each satellite pass. This record must be in machine readable form for immediate automatic processing and/or transmission to a remote computer facility for final position determination of each ELT.

#### I.2 System Requirements

- I.2 The system requirement calls for the following basic functions:

- 1. Search

- 2. Detect

- 3. Measure

- 4. Identify and track

- 5. Store

Only functions 1 and 3 require appreciable time; 2, 4, and 5 are essentially instantaneous, although 4 and 5 may require computation time.

Information pertinent to the design and performance analysis of the system is:

- 1. Up to 8 ELT signals must be simultaneously handled. These exist in a 12 kHz band at an input IF frequency of 70 MHz.

- Carrier frequency must be measured to a relative accuracy of

1 Hz rms and time tagged to an absolute accuracy of 100 msec.

- 4. This dual measurement must be stored for later retransmission in machine readable form.

- 5. Each signal has a doppler shift range of  $\pm 2.75$  kHz.

- 6. Signals need not be resolved when within 100 Hz of each other.

- 7. Minimum peak doppler rate is 5 Hz/sec, the maximum is 14 Hz/sec, and the doppler rate can approach zero.

- 8. If tracking is lost, search must continue for 30 to 60 seconds.

- 9. On the average, 10 seconds between frequency readings is called for, but these need not be synchronous.

- 10. The maximum length of a satellite pass is 1200 seconds.

- 11. The Carrier-to-Noise density ratio will exceed  $C/N_0 = 26 \text{ dB-Hz}$ .

- 12. ELT modulation is of the "chirp" variety, either sinusoidal or square wave with duty cycles between 1/3 and 1/2, and with up to 100% modulation. The sweep width is 700 Hz in a band from 300 to 1600 Hz, and the rate is between 2 and 4 times per second.

As well, the signal may be continuous, or pulsed with a minimum "on" period of 2 complete sweeps and an off/on ratio of up to 2, limited to 4 sweeps. Thus the signal may be "on" for a minimum of 0.5 seconds and "off" for a maximum of 2 seconds.

- 13. Carrier uncertainty is about +3.5 kHz and there is the possibility of incidental FM modulation accompanying the chirp.

This modulation appears to be linear with an observed maximum

peak-to-peak deviation of 80 Hz. Phase noise  $\pm 15$  Hz from the carrier has an observed 3 dB bandwidth of 4 Hz and an rms deviation of  $5^{\circ}$ .

These requirements and signal specifications will imply fundamental limitations on ELT receiver performance. For example, if the  $\text{C/N}_{\text{O}}$  of an ELT signal is such as to require a frequency measurement period of 1 second, then it would not be possible to measure a pulsed ELT signal with an "on" period of 0.5 seconds.

Various alternatives are available in terms of the functional devices used, their implementation, and the overall strategy inter-relating the several system functions. Devices available to implement the system include:

- a. filter banks,

- b. swept (or stepped) filters,

- c. phase locked loops,

- d. counters,

- e. digital and computational units,

and analog, hybrid or digital alternatives are available for the construction of these sub-systems. The sequencing, or interrelating, of the five primary system functions gives rise to numerous possibilities. One is the sequence "scan and detect ELT's across the whole band, measure, store" once every 10 seconds; although this would mean, for example, that the scanning device

would not be interrogated during the measurement period, and so this is intrinsicly inefficient. More effective methods would be "search in a swept or stepped mode, detect, measure, resume search", or "search in a swept or stepped mode, detect, assign measuring device, continue search while measuring". A single, or several search and measuring devices could be used in each case, and so the alternatives are numerous, particularly as each function has several candidate devices as possibilities.

As a consequence of the multiplicity of candidate systems, the fundamental constraints on the processes to be implemented were determined. This resulted in the elimination of a number of alternatives, and set the stage for a more detailed consideration of the more promising approaches.

## I.3 Constraints on the Search Process

Initially it is assumed that the ELT signals are sinusoids; further limitations due to the particular properties of these signals will be introduced later.

The search process consists of identifying a possible ELT signal on an energy or amplitude basis in a background of ambient noise. The relevant specifications affecting this task are:

1. ELT signals separated by more than 100 Hz must be separately measured.

2.  $C/N_0 = 26 \text{ dB} \cdot \text{Hz}$ .

While the bank of filters or swept filter approaches are different in detail, and while this difference would be taken into account in more detailed analysis, the same first order analysis suffices for both,

Minimum filter bandwidth cannot exceed 100 Hz and this would yield a SNR of 6 dB in the band giving marginal detection performance. Alternatively, a 30 Hz bandwidth would yield an 11 dB SNR and ease the detection of adjacent signals of different strengths. For incoherent (i.e. envelope) detection with a decision threshold of 0.6 relative to a typical signal, false alarm and miss probabilities would both equal 0.02 compared to 0.18 for the 100 Hz case (see Figures 1 and 2). Coherent detection would provide 3 dB improvement in effective signal strength.

To simultaneously cover the 12 kHz band would require 400 filters, or 800 to avoid a further 3 dB loss for signals located mid-way between filters. Alternatively, a 512 point FFT could be employed. As noted, continuous monitoring of 100 Hz or less contiguous bands across the full 12 kHz is unnecessary and would be costly no matter how implemented. (see FFT processor costs at end of Appendix B).

The time required to detect the presence of a signal however could be taken to be the inverse of the pre-detection filter bandwidth, or about 33 msec. for the 30 Hz filter. Alternatively, assume a white noise background and an averaging time T; then at the input

to the decision device

$$SNR = \frac{C}{N_O} T$$

assuming a 3 dB loss due to incoherent detection. A detection probability of 0.98 would be achieved in about 20 msec, thus allowing measurements to be spaced at 25 Hz if the whole 12 kHz band were covered in 10 seconds. If, to be safer, 50 msec. or 1.5 of a time constant were allowed per 30 Hz of bandwidth, two devices would be needed in simultaneous operation to sweep the band.

A phase locked loop performs, in effect, coherent detection, and initial estimates, based on published experimental data, indicate that a single PLL with a 20 Hz loop bandwidth could be swept across the band in 10 seconds with about a 95% detection probability.

It would appear, then, that a single PLL could suffice for detection.

## I.4 Constraints on the Measurement Process

The measurement of frequency can be achieved by narrow band filtering and energy detection, or by filtering followed by cycle counting.

Relevant basic specifications are:

1.

$$C/N_0 = 26 \text{ dB-Hz}$$

2. Measurement accuracy = 1 Hz

Assuming initial detection in a 30 Hz band defines the measurement range, final resolution could be accomplished by a bank of some 60 one Hertz filters, each requiring about 1 second to respond, or equivalently by a 64 point FFT with an initial response time of at least 1 second. (As the doppler rate can be as high as 14 Hz/sec, these alternatives will be discarded at once.)

The direct approach by counting devices is to count cycles over a fixed period T, and then the frequency is

$$f = N$$

Two sinusoids of frequency f and f+ $\Delta$  differ in phase by  $2\pi\Delta T$  after T seconds and these two signals will register the same count until this phase exceeds  $2\pi$ . Thus T must be 0.41 seconds in order to assure an rms frequency error of 1 Hertz.

A more sophisticated technique is to measure the time required for a specified number of cycles, N, to occur. Then, the frequency is

$$f = N \over T$$

and a noiseless sine wave is measured unambiguously. In practice, this will not be the case.

Signal distortion, resulting from carrier phase noise (statistical), incidental FM (periodic) and the doppler modulation itself, introduces the following rms frequency measurement errors:

- 1.  $(\Delta f_{\rm rms})_{\rm phase\ noise} = (2\pi T)^{-1} \sqrt{2} \Delta p_{\rm rms} \ (1-\exp(-(TB_{\rm p})^2))$  where  $\Delta p_{\rm rms}$  and  $B_{\rm p}$  are the rms deviation and 3 dB bandwidths respectively of phase noise components falling within the  $\pm B_{\rm N}/2$  pre-detection filter bandwidth. The 1-exp(.) factor here results from phase error correlation at start and stop counter trigger points, and tends to 1 as T >>  $B_{\rm p}^{-1}$ .

- 2.  $(\Delta f_{rms})_{FM} = (2\pi T)^{-1} \frac{\sqrt{2}\Delta F_s}{f_s}$  sin  $(\pi f_s T)$  assuming the measure-

ment starting time is randomly phased with respect to the chirp.  $\Delta F_s$  and  $2 \le f_s \le 4$  Hz are the peak deviation of the incidental FM (here assumed sinusoidal) and chirp rate respectively. Note that selecting T to equal an integral number of chirp cycles theoretically removes the degrading effect of incidental FM; however,  $f_s$  is a variable not immediately known to the receiver.

3.  $(\Delta f_{rms})_{non-linear\ doppler} = \sqrt{E \left\{ \frac{d^2 f(t_0)}{dt^2} \right\}} \left( \frac{T^2}{24} \right)$  where f(t) is the doppler frequency at time t and E(.) denotes an ensemble average over all doppler characteristics.

The rms phase error at the pre-detection filter output due to thermal noise is given by  $\left(2\frac{S}{N}\right)^{-1/2}$  for  $\frac{S}{N} >> 1$  where  $S/N = 26 - 10 \log (B_N)$  dB. The corresponding rms frequency measurement is then

The final source of error is inherent to the measuring device itself. Evaluation of the HP model 5345A fast counter has revealed the following types of measurement error for an ideal sine wave input:

- error uniformly distributed on + 1 nsec at both start and stop triggering points (due to minimum of 2 nsec time base interval)

- 2. detection phase errors uniformly and independently distributed on  $\pm$  .3% of a cycle at both start and stop trigger points.

- 3. relative time base error determined by 20 minute stability of time base generator reference oscillator.

Rms values for the resulting frequency measurement errors are as follows:

$$(\Delta f_{rms})_{trigger\ error} = 1.16\ X\ 10^{-9}\ T^{-1}f_{c}$$

$$(\Delta f_{rms})_{phase detection error} = .006T^{-1}$$

$$\Delta f_{\text{time base error}} = S f_{c}$$

where  $\mathbf{f}_{\mathbf{c}}$  is the incoming IF frequency and S is 20 minute reference oscillator stability.

Since the sources of errors described are statistically independent, the resulting rms error is simply the r.s.s. (root sum squared) of the individual components.

Assuming the following parameter values

```

\Delta p_{rms} = 4.8° (1 to 15 Hz from the carrier typical of Garret ELT Spectra surveyed)

B_p = 2 Hz

a(t_0) = .2 Hz/sec<sup>2</sup> (worst case)

B_N = 20 Hz, 30 Hz

f_C = 100 kHz (worst case)

S = 1 X 10<sup>-9</sup>

```

Figure 3 plots the individual and net rms frequency measurement errors vs measurement period, neglecting incidental FM. All except the non-linear doppler and phase noise contributions decrease linearly with T, phase noise is controlling for T > 0.5 seconds, and time base error is negligible.

The preceding analysis presumes a sophisticated counter which measures the time, T, required for a set number of cycles, N, but the much simpler fixed period counter introduces the previously discussed ambiguity in frequency. This is equal to the inverse of the measurement period, but, if the frequency of the signal can be multiplied

from f to nf, and then measured by a fixed counter, the ambiguity is reduced by the factor n. It is, of course, necessary to consider accompanying signal-to-noise ratio effects.

If a PLL utilizes a counter in the feedback loop such that the input/output frequency ratio is n, then the loop locks with an output frequency which is n times that of the input. However, the standard deviation in the output phase error is also increased by the factor n, but this should not cause real difficulty. For example, the previous analysis shows that if n=4 and the measurement period is 0.25 seconds, then the rms frequency error (neglecting incidental FM) is 0.4 Hz for a 30 Hz pre-detection bandwidth.

Another approach is to twice square and filter the signal with the result that (Davenport and Root, p. 262)

$$\frac{\text{SNR out}}{\text{SNR in}} \approx \frac{1}{16} (1 + 2.5/\text{SNR}_{in} + 2/\text{SNR}_{in}^2 + .5/\text{SNR}_{in}^3)^{-1}$$

While measurement error due to phase distortions is necessarily quadrupuled whether a PLL or power law device is used, the effect of thermal noise is quite different. In the PLL case, the net rms phase error is multiplied by four, corresponding to an SNR degradation of approximately 6 dB over a wide range of input SNR's. The two cascaded square-law devices, on the other hand, degrades the SNR by at least 12 dB, and exhibits a sharp threshold effect.

In all, a fixed period counter, with PLL frequency multiplication if needed, may well be sufficient for the measurement of the ELT carrier frequency.

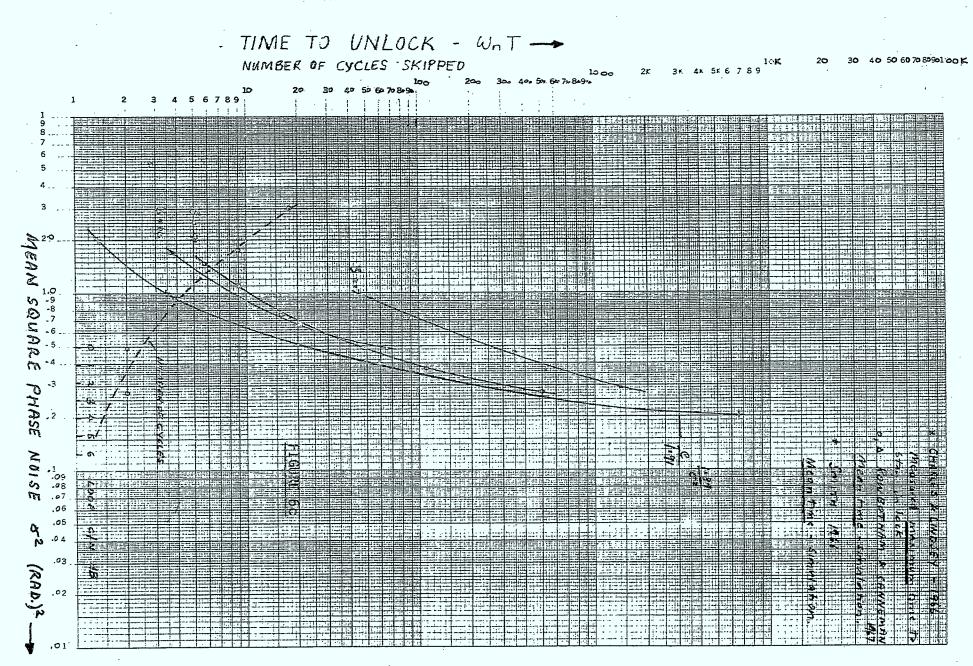

The PLL required for the searching function has characteristics reasonably similar to that needed for pre-filtering the signal before the frequency measurement. An SNR in the loop of 3 dB would be expected (with a 100 radians/sec  $\omega_n$  or 100 Hertz noise bandwidth), and a resulting mean square phase noise of 0.25 radians squared. This would not be troublesome if the measurement period were much less than 60 msec; nor would it be troublesome if the period were long, say several seconds. The mean time between cycle slips would be 6 seconds, the number of cycles slipped would average 1.5, and the frequency measurement specification would be met. Alternatively, to shorten the frequency measurement period to less than a second, the PLL bandwidth could be changed following ELT detection, or another loop could be utilized.

# I.5 Effects of ELT Modulation

## I.5.1 Up-Link Doppler

As the tracking error at the maximum doppler rate of 14 Hz/sec for a PLL with a 16 Hertz loop bandwidth would be 0.5 degrees, and this varies inversely as the square of the bandwidth, doppler does not set difficult design criteria on any phase locked loops used in the system. However, as mentioned, the doppler rate does preclude use of a filter bank to measure frequency within 1 hertz, simply because

the frequency will have traversed at least 14 Hz in the time required for the measurement.

Since carrier frequency is changing with time, and since an appreciable time is required for the measurement, there is a question of just when the "instantaneous frequency" of the carrier is measured. To resolve this question, take the signal being measured to be

A

$$sin \phi(t)$$

and the measurement period to be from t = 0 to t = T. Represent

$$\phi(t) = \phi_0 + \phi_1 t + \phi_2 t^2 + \phi_3 t^3 + \dots$$

so that the instantaneous frequency expanded in a Taylor series about t = 0 is

$$f(t) = \frac{1}{2\pi} \frac{d\phi}{dt} (t) = \frac{1}{2\pi} [\phi_1 + 2\phi_2 t + 3\phi_3 t^2 + \dots]$$

$$= [f_0 + f_1 t + f_2 t^2 + \dots]$$

where  $f_i = \frac{1}{i!} \frac{df^i(0)}{dt^i}$

In the measurement period T, the number of phase resolutions will be

$$\frac{1}{2\pi} [\phi_1 T + \phi_2 T^2 + \phi_3 T^3 + \dots]$$

and this divided by T will be the measured frequency

$$\hat{f} = f_0 + \frac{f_1}{2} T + \frac{f_2}{3} T^2 + \dots$$

The difference between the measured frequency and the instantaneous frequency at  $t = \frac{T}{2}$  is then

$$\hat{f} - f(T/2) = f_2 \frac{T^2}{12} + \dots$$

Should the change of frequency be linear i.e.  $f_i = 0$  for  $i \ge 2$ , the measured frequency is that at  $t = \frac{T}{2}$ , and compensation for the measurement period is simple. Otherwise more complex correction is necessary.

Preliminary study of typical ELT data suggests a maximum doppler second derivative of about 0.2 Hz/sec<sup>2</sup> which gives corrections:

| Measurement Time | Maximum<br>Frequency Correction |  |  |

|------------------|---------------------------------|--|--|

| (sec)            | (Hertz)                         |  |  |

| 10               | 4                               |  |  |

| 1                | 0.04                            |  |  |

| 0.1              | 0.0004                          |  |  |

This indicates that if the measurement time is of the order of 1 second or less, the linear correction is sufficient.

## I.5.2 Chirp Modulation

As indicated in the Request for Proposal, ELT signals have from 33% to 45% of their power in the modulation first sidebands, and up to 22.5% and 4.5% respectively in the second and third sidebands. The first sideband power is distributed reasonably uniformly over 700 Hz ranges beginning at least ± 300 Hz from the carrier, and so detection and measurement of an ELT is not disturbed by its own sidebands. The carrier-to-spectral density of the sidebands for 100% sinusoidal, 100% rectangular - 33 1/3% duty cycle AM modulations and equal ELT carrier levels are indicated below

| Modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | C/I <sub>o</sub> (dB-Hz) |               |               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------|---------------|

| maniferent of a state | 1'st harmonic            | 2'nd harmonic | 3'rd harmonic |

| 100% sinusoidal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 34,5                     | X             | Х             |

| 100% rectangular, 50% duty cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 32.4                     | X             | 55,6          |

| 100% rectangular,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 30,2                     | <b>39</b> ,2  | 48,0          |

The maximum spectral density of a sideband is 4.2 dB below the ambient noise, and so on an average power basis the modulation will not greatly interfere with ELT detection. Viewed in an alternate fashion, the instantaneous frequency of a first sideband is changing at least at the rate of 1400 Hz/sec. Thus a sideband signal spends some 21 msec or 4.2% of its time within the bandwidth of a 30 Hz filter with a time constant of 33 msec. This is sufficiently long to cause a response, but this response would peak roughly 9 dB below carrier level (equal ELT's assumed), be present for about 50 msec (10% of time) and degrade the false alarm probability to only about .10 for an incoherent detection threshold of .6 x signal amplitude. This could be reduced substantially by use of a more sophisticated detection device.

The following table gives the probability that one or more first sidebands will fall within +15 Hz of a wanted ELT assuming independent

and uniform distributions of ELT frequencies across the 12 kHz band. Note that the probability of more than one interfering sideband falling on an ELT is normally very small.

Number of Probability of first sideband interference

ELT's Present sweeping within 15 Hz of an ELT carrier

|   | 1 interferer | 2 interferers | 3 interferers* |

|---|--------------|---------------|----------------|

|   |              |               |                |

| 1 | 0            | 0             | 0              |

| 2 | .117         | 0             | 0              |

| 3 | , 229        | ,0049         | . 0            |

| 4 | .336         | .0146         | ,0004          |

| 5 | .548         | .0353         | .0016          |

The probability that an ELT is subject to sideband interference, at any instant of time is obtained by multiplying these numbers by .1, which is the fraction of time interfering power due to a sideband sweeping back and forth across an ELT is actually present at the output of the pre-detection filter. On the other hand, the numbers in the table are clearly optimistic due to the assumption of a uniform probability distribution of ELT's across the 12 kHz band.

<sup>\*</sup> In this case the likelihood of direct interference between two of the sideband producing ELT's is also high.

Another possible difficulty occurs if the sideband of one ELT signal makes the measurement of another signal more difficult. However, if the amplitude of this interference is less than that of the signal being measured, and if the interference sweeps the entire pre-detection bandwidth an integral number of times during the measurement period, the net effect on a fixed period counter with an ideal pre-filter would be zero as the lengthening and shortening of the periods between zero crossings would cancel. Only if the sweep began or ended within the measurement band would there be a net effect, and this would occur with a probability.

$$P = 2 \left(\frac{30}{700}\right) = 0.086$$

for a 30 Hz pre-filter. The level of the interference at the filter output has previously been calculated to be at least 9 dB below the carrier level or only 2 dB above the noise. Consequently, this event even when it does occur, will not cause appreciable error if the wanted and interfering ELT signals are of comparable amplitude.

#### I.5.3 Pulsed ELT's

Further potential difficulty arises if the ELT signal is pulsed. Such a signal could be "on" for as little as 0.5 seconds and "off" at least 2.0 seconds. The existence of such signals sets a premium on the time available for measurement. Were the measurement period more than a second, many signals could be lost due to inadequate opportunity for measurement. If a measurement period of 0.25 seconds is chosen, the probability that a 0.5 second "on" ELT can be measured during the "on" interval in which it is detected is

not more than 0.5. For various "on" times Ton, this probability varies as follows:

| Ton       | Prob, of incomplete    |

|-----------|------------------------|

| (seconds) | measurement            |

|           | i                      |

| 0.5       | <u>≤</u> ,0 <b>.</b> 5 |

| 1.0       | ≤ 0,25                 |

| 2.0       | ≤ 0.13                 |

| 3.0       | <u>&lt;</u> 0.08       |

There may be no simple way of overcoming this, and so it is to be expected that pulsed ELT signals will be measured and tracked less effectively than continuous signals. Certainly it will be necessary to continuously confirm signal presence during frequency measurement.

#### I.5.4 Incidental FM

The carrier may also be subject to incidental FM modulation which will be assumed to be periodic at the modulation sweep rate. Short interval frequency measurements would be ambiguous over the range  $(-\Delta F, \Delta F)$  where  $\Delta F$  is the peak incidental FM deviation; successive randomly phased frequency measurements would therefore be subject to this range of relative error. If the incidental FM is approximately linear and can be tracked without distortion by the measuring device pre-filter, the frequency measured would be the average over the measurement interval. Taking that interval to be

where N is an integer,  $\alpha {<} 1,$  and .25  $\leq$   $\tau$   $\leq$  .5 is the sweep period, the variation in measured frequency is

$$\frac{\alpha(1-\alpha)}{2N}$$

$\Delta F$

which has a maximum of  $\Delta F_{\star}$  . To hold this within one Hertz requires  $\overline{8N}$

$$N > \Delta F \over 8$$

As pulsed ELT's with 2 sweeps "on" would be limited to N=1, it would be necessary that

$$\Delta F < 8 Hz$$

,

otherwise the specification could not be met without elaborate, and perhaps impractical schemes, e.gs. chirp synchronous measurement, estimation and post-measurement compensation etc. Study of a specific ELT signal indicated a  $\Delta F$  of about 37 Hz, and the inescapable conclusion is that very degraded system performance will be inevitable with some ELT's.

Figures 4 and 5 plot the frequency error due to sinusoidal and linear incidental FM when time base measuring and cycle counting in a fixed period counters respectively are used. Note that given its initial  $2\pi$  measurement ambiguity, the simple (fixed period) counter

is somewhat less sensitive than the time base measuring counter to additional degradation due to signal distortion.

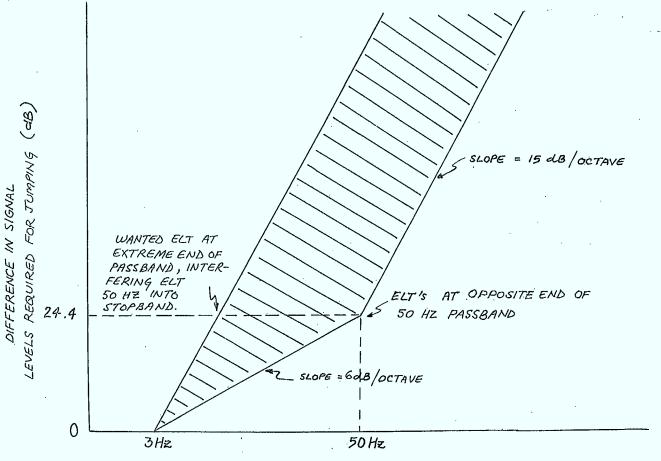

## I.6 Interference Effects of ELT Carriers Beyond 100 Hz Separation

This occurance can be modelled worst case by considering the effect of an interfering sinusoid on a single period T measurement where the estimate of frequency is

$$f = \frac{1}{T}$$

Here a phase change caused by an additive sinusoidal interferer  $\Delta f$  Hz from the wanted sinusoid is

$$\phi < 2\pi \frac{\Delta f}{f} \left(\frac{S}{I}\right)^{1/2}$$

where S/I is the signal-to-interference power ratio at the output of the pre-detection filter. A phase change  $\phi$  corresponds to a period change of  $\frac{\varphi}{2\pi f}$  and a frequency change of  $\frac{\varphi}{2\pi T}$ , so the specification is met if

$$\frac{S}{T} > (\Delta f)^2$$

If the wanted and unfiltered interfering ELT's have equal amplitudes and the pre-detection filter has a normalized amplitude characteric  $\alpha$  ( $\Delta f$ ), then we need

$$\alpha \ (\Delta f) < \frac{1}{\Lambda f}$$

and for  $\Delta f > 100$  Hz this is met by a three pole filter with a bandwidth of 30 Hz.

Thus, even the most disturbance sensitive frequency measurement technique does not require extraordinary pre-filters. For the 1 second counting method, a single pole filter suffices.

### I.7 Control of Receiver Processing

In order to detect the occurence of ELT's, perform the required frequency measurements about every 10 seconds, and store the data in individual ELT logical fields, the following control processing is required.

## I.7.1 Identification and Tracking

This is a single process and there are two basic approaches:

- 1. continuously track the ELT signal with a phase locked loop

- 2. measure each signal as detected and identify by extrapolation from previous measurements.

In each case no ELT signal would be identified as such until tracked over 30 seconds, nor declared "ended" until lost for over 30 seconds.

In the continuously tracking system, the detection device would have to be commanded to ignore signals which were already being tracked. As lock will be broken when ELT signals are pulsed, or approach within 100 Hz, an extrapolation system will be required for this method just as for the other.

Extrapolation can be accomplished by making

$$\hat{f}_3 = 2f_2 - f_1$$

the estimate of the signal frequency at the next sampling instant. This assumes periodic sampling and <u>may</u> have to be slightly modified for natural sampling. A survey of ELT records suggest that the next measurement would be within 25 Hz of this estimate. Thus signals separated by 100 Hz would not be confused, even over a 30 second period. An appropriate algorithm will have to be defined to identify and track distinct ELT's (continuously tracking system only), and initiate and terminate ELT records.

# I.7.2 Signal Acquisition and Measurement Strategy

Previous analysis suggest that one or two detection filters be used to cover the band, rather than a bank of filters performing simultaneous detection. The filters could be in adjacent bands and stepped as a pair through the 12 kHz band in 10 seconds, separated by 6 kHz and swept (in 20 seconds) over the band, or each swept over a disjoint 6 kHz band in 10 seconds. In each case, all continuous

ELT signals present will be detected within 10 seconds with probability greater than 0.95. For a pulsed ELT with a two to one off/on ratio, the detection probability would be about 0.32 in 10 seconds, 0.54 in 20 seconds, 0.68 in 30 seconds 0.78 in 40 seconds, and so on, assuming that the pulsing and scanning were not synchronous. (If they were, the detection probability would remain at 0.32). In any situation, the missed detection probability can be improved by using more filters scanning at a lower sweep rate.

The simplest approach to acquisition and measurement is to have a number of devices capable of both these functions sweeping across the 12 kHz band. Were one of these devices to detect a signal, it would cease sweeping and measure the signal frequency. Once that was finished, sweeping would commence again. Were each device operating completely asynchronously, their distribution in time-frequency would be difficult to predict and undesirable distributions of measurements in time and frequency could occur. A simple solution for this problem is to stop all sweeping while any device is making a measurement. This would ensure the uniform spacing of the devices in frequency,

In fact, one such device could handle up to 8 ELT signals in 10 seconds by sweeping the band in 6 seconds and using up to 8 X 0.5 seconds for measurement. That assumes a PLL as the detection filter, a 0.50 second frequency measurement interval, and yields a detection probability of around 90%. Two or more devices would yield higher detection probabilities or longer measurement periods. This is a

viable approach and will be referred to as Option A. Note that the same device would be used for <u>both</u> signal detection and frequency measurement; that each device should sweep the 12 kHz band in 20 seconds, and be spaced at 6 kHz, if two were used; and that, if more than one is used, fixed bandwidth filters may be possible as an alternative to PLL's.

Other arrangements are available which would allow simultaneous search and measurement in such a system but at the cost of much additional complication and to no advantage. These alternatives will not be investigated further.

In the above approach, identification and tracking would be accomplished by extrapolation using frequency samples spaced about 10 seconds apart. A distinctly different alternative is to continuously track each detected ELT signal with a PLL. In this option, a signal detection device would be swept across the band (in 10, or perhaps more, seconds) and upon detection of a new ELT a PLL would be assigned to track that signal. Frequency measurements would be periodically obtained from the PLL output. Alternatively, if the PLL were used in both signal acquisition and tracking, a new PLL could be assigned to the search once the currently sweeping PLL had locked to an ELT signal. While this approach is intrinsically more complex than Option A, it may offer some performance advantages and so will be designated as Option B.

### I.7.3 Software Element

The two basic types of receivers can functionally be broken into distinct parts, as shown in Figure 6. In its simplest form, the software/storage element of the Type A receiver "passively" accepts in serial form successive measurements of frequency as they are completed. The correct time tag for each measurement can be easily derived from the computer clock using the relation

time tag = mid point of measurement interval

- ~ computer time on receipt of sample

- 1/2 measurement period constant delay (if any)

The software must sort incoming (time, frequency) samples into appropriate ELT records. Extrapolation from previous measurements and limits on the maximum doppler rate of change and second derivative can be used to define admissable regions of successive ELT measurements - overlapping decision regions can be bisected and samples falling out of admissable regions flagged as possible new ELT's. A suitable algorithm for initiating new and terminating old ELT records must be determined. After a satellite pass some apparently bad (time, frequency) samples may be retained, if desired, in a "mixed bag" data file.

Unlike the Type B case, control feedback from the software/storage element to the signal processing element is not essential to the Type A concept. Type A is therefore not only functionally simpler,

it permits largely parallel and independent development of the two constituent sub-systems.

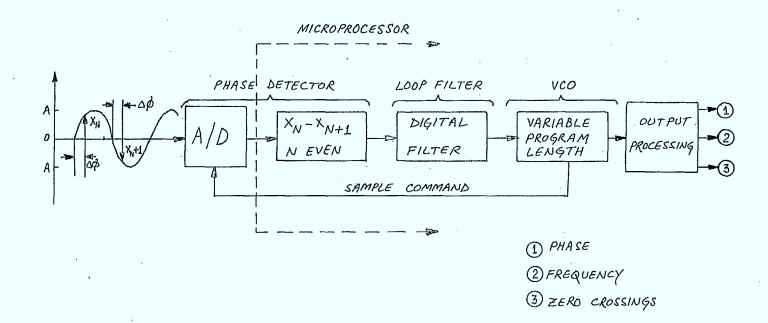

In the Type B receiver, the computer element will have to exert some control over the assigning, sweeping and disengagement of 8 PLL's, and the start/stop, assignment/disengagement, and interrogation of measuring device(s). If the measuring device(s) are not under computer control, e.g. free-running, a variable delay between the midpoint of a measurement period and the instant the frequency sample arrives at the computer may be present, in which case external time tagging is required. This is avoided if the computer commands measurement start/stop, which also permits the computer clock to be used as the time-base for a fixed period counter and, if desired, facilitates the switching and time-sharing of a common measuring device among several tracking devices.

For the Type A receiver, simple computer control of the sweep and measurement taking devices may prove advantageous if this does not add greatly to the overhead time. However, it is clear that much more signal processor/software element interaction will be essential to the Type B receiver than in the Type A case.

Realizable performance advantages of the Type B, if any, lie in one or more of the following categories:

- regular measurement of pulsed ELT's following initial detection.

- measurement and correct identification of 2 previously detected ELT's now separated by less than 100 Hz

- improved frequency measurement accuracy in non-stationary S/N environment by repeated or selective measurement taking.

### I.8 Recommendations

It is recommended that the systems designated as Option A and Option B be further investigated. This will first involve decisions regarding the various alternative approaches still open within the scope of the two systems which will result in at least two receiver structures to be further analysed. Detailed calculations of expected performance will be made, along with engineering and economic estimates of analog, hybrid and digital implementations.

### I.9 References

Phase-Lock and Frequency Feedback Systems, J. Klapper and J. Frankle, Academic Press, 1972.

Davenport and Root, "Random Signal & Noise" McGraw Hill 1958

- G.D. Bergland, "A Guided Tour of the Fast Fourier Transform," IEEE Spectrum, July 1969 pp 41-52

- J.P. Frazier and J. Page, PLL Frequency Acquisition Study" Trans. IRE, <u>SET-8</u>, pp 210-227, Sept. 1962

- S. Gupta "On Optimum Digital Phase-Locked Loops", IEEE Trans Com. Tech, Vol. com-16, April 1968, pp. 340-344.

- J.D. Schoeffler and R.H. Temple, "Minicomputers: Hardware, Software, and Applications, IEEE Press, 1972.

- F.M. Gardner, "Phase Lock Techniques" Wiley, New York 1966.

- "Electronic Counter 5345A" Hewlett-Packard Technical Data Sheet, March 75.

- "A. Blanchard "Phase Lock Loops, Application to Coherent Receiver Design", Wiley, 76

### II.1 Introduction

Given the requirements of and constraints on the receiver system presented in Part I, it is necessary to identify and evaluate alternate means of realizing the functionally distinct Type A and Type B receivers. Performance, Cost and risk factors will be taken into consideration in assessing alternate receiver designs.

It is required to establish the parameters and determine the performance of candidate receivers in a more exact fashion than that employed in Part I to bound the problem. Part II analyzes the constituent elements of either Type A or Type B receiver, and arrives at a total of ten possible basic approaches consisting of combinations of the following:

- Type A <u>or</u> Type B

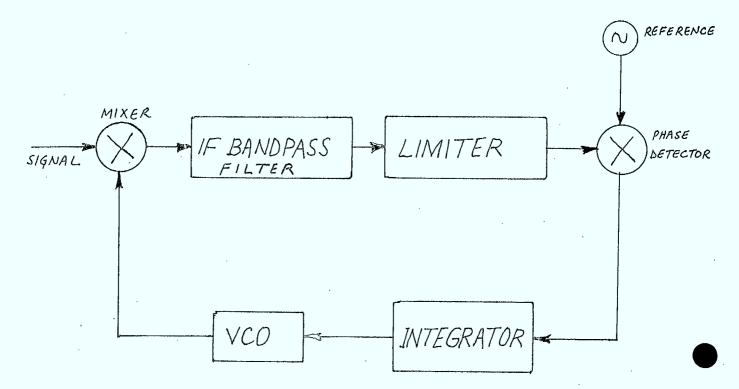

- search and frequency measurement performed by a PLL having a bandpass filter preceding the phase detector and continuously swept over 12 kHz, or by a stepped programable frequency synthesizer beating the signal into a bandpass filter followed by a PLL.

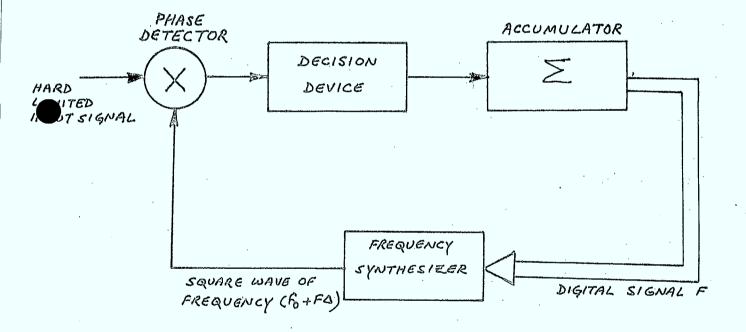

- frequency measurement of the signal detected by PLL performed using a fixed period counter at the VCO output, or by a digitally controlled fine step (< 1 Hz) synthesizer replacing the VCO, or by direct measurement of VCO input (with the stepped sweep method only).

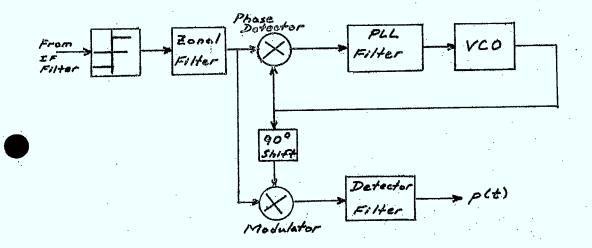

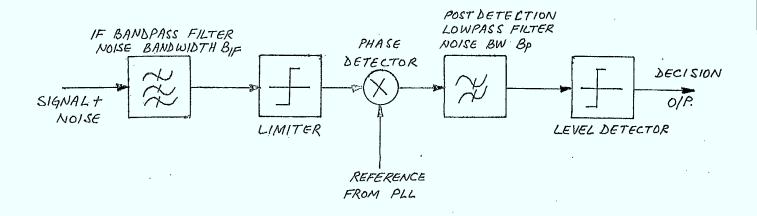

The functional devices involved will be suitably interfaced with and controlled by a PDP-11/03 microprocessor. All cases involve coherent detection of an ELT and reduction of the PLL loop filter bandwidth prior to frequency measurement.

Part III evaluates the candidate receivers from the practical design tradeoff, ease of implementation, capital cost and schedule standpoints. Part IV summarizes the results of the Study Phase, and recommends a single design approach.

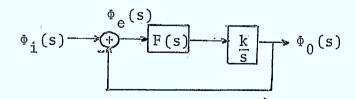

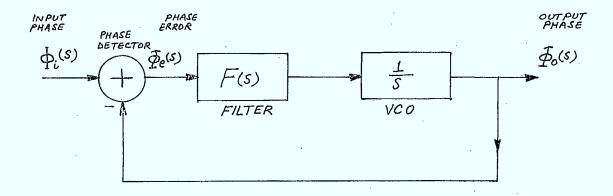

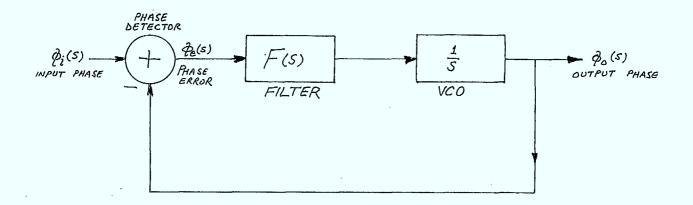

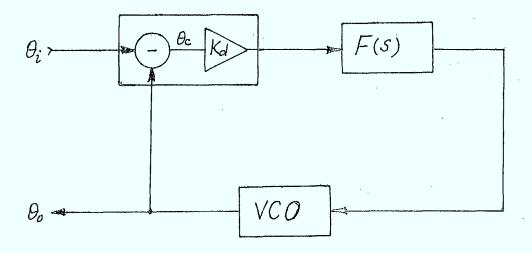

### II.2 Phase Lock Loop Analysis

More in-depth analysis of the detection and measurement processes, key elements of any Type A or Type B receiver is required. The combinations are as follows:

Detection - swept PLL (coherent)

swept filter (non-coherent)

Measurement - analog PLL with counter

- hybrid PLL without counter

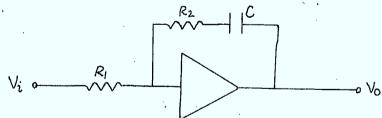

- analog PLL and measurement of VCO output

It is clear from Part I that the PLL offers both faster sweeping and a lower probability of failing to detect the signal than the swept filter, and therefore gives better performance as the detection device. In any event, system constraints dictate that a PLL must be used to filter the signal prior to measurement. A detailed study of the performance and tradeoffs associated with the design of Phase Locked Loops is therefore justified at this point.

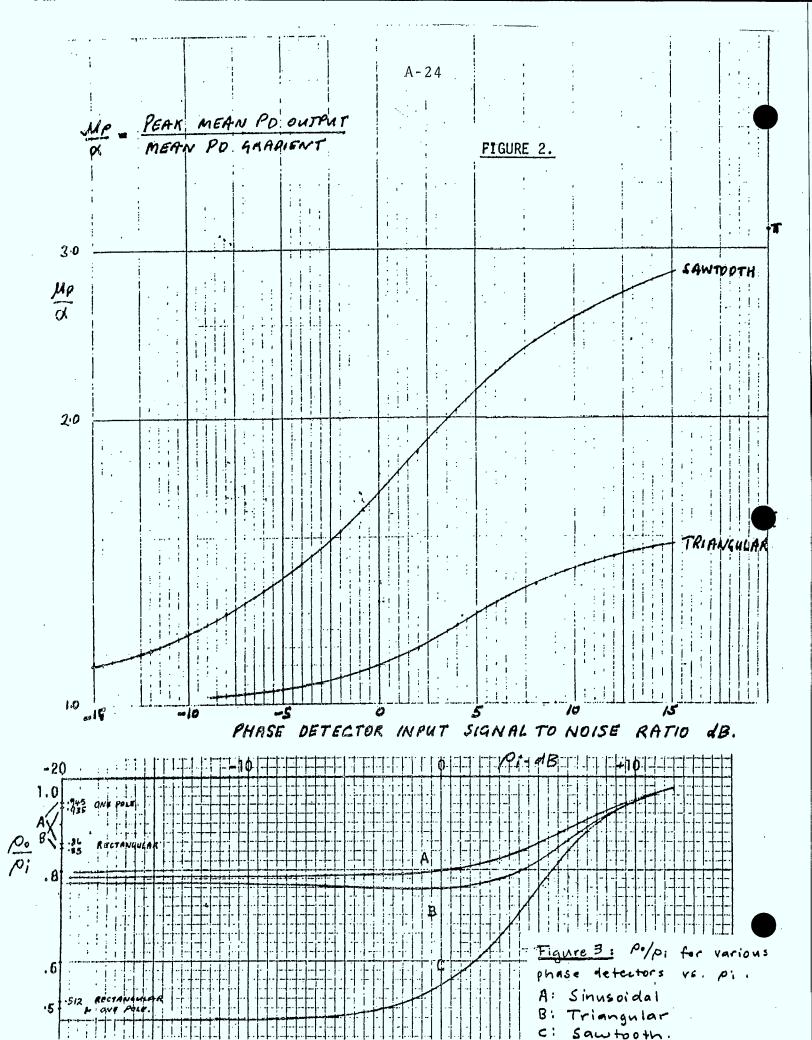

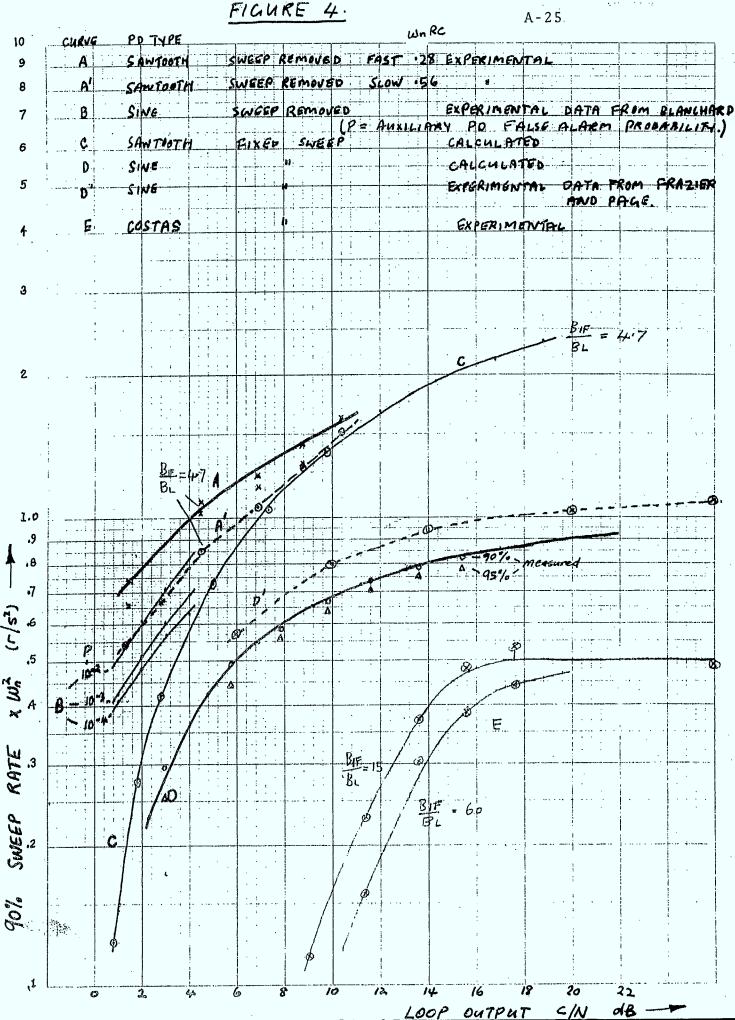

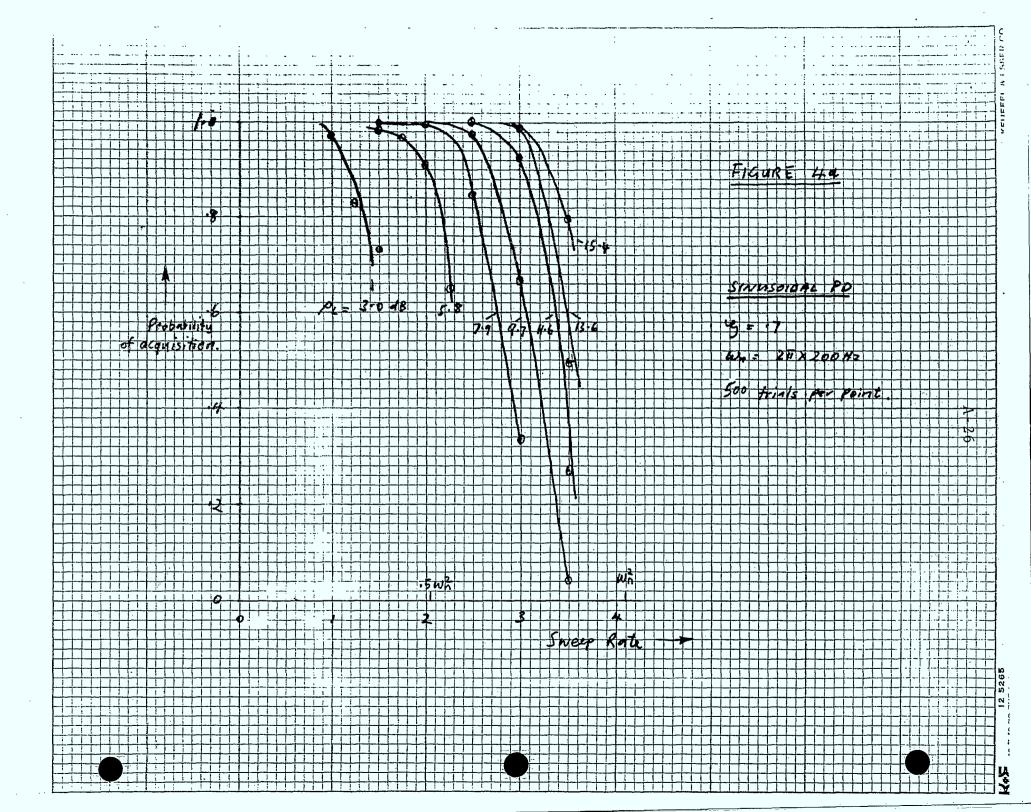

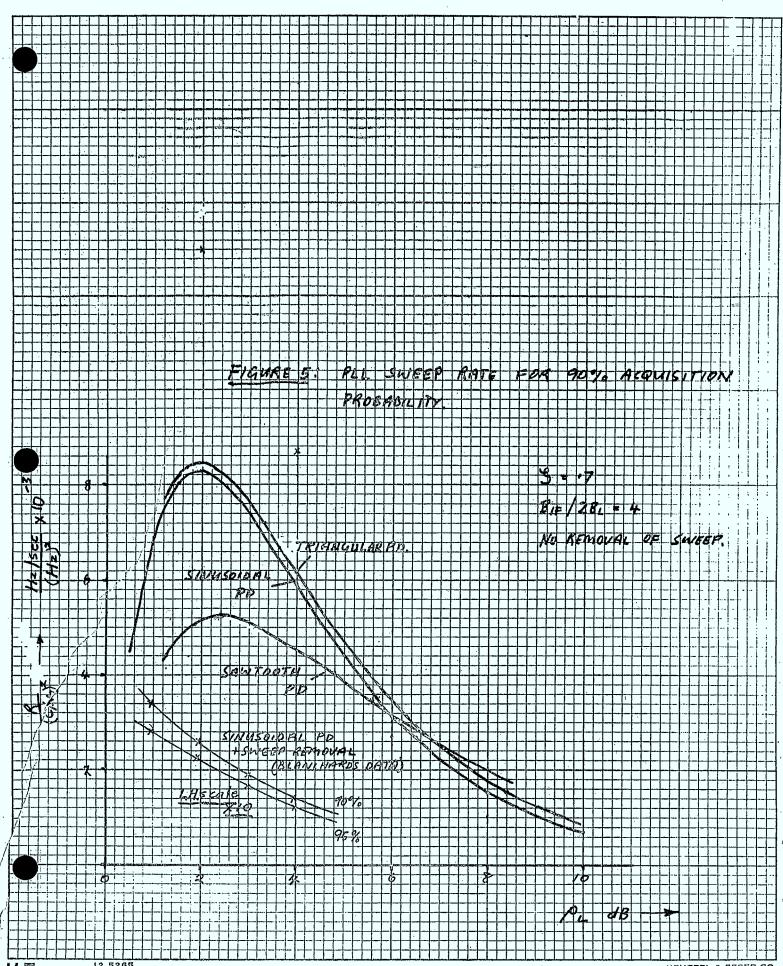

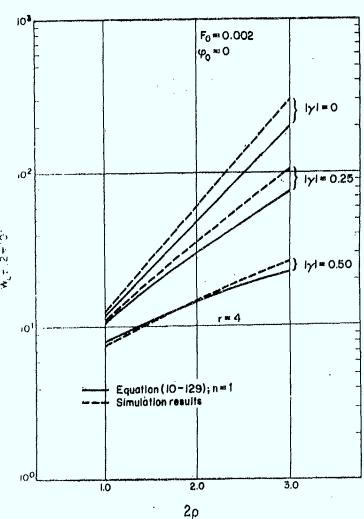

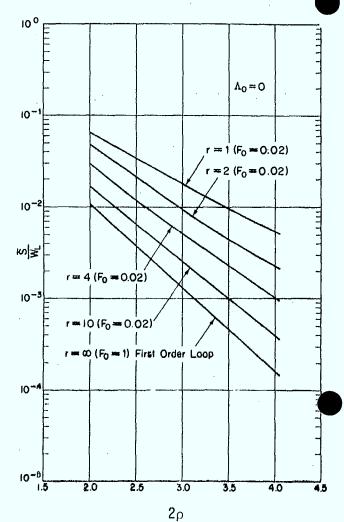

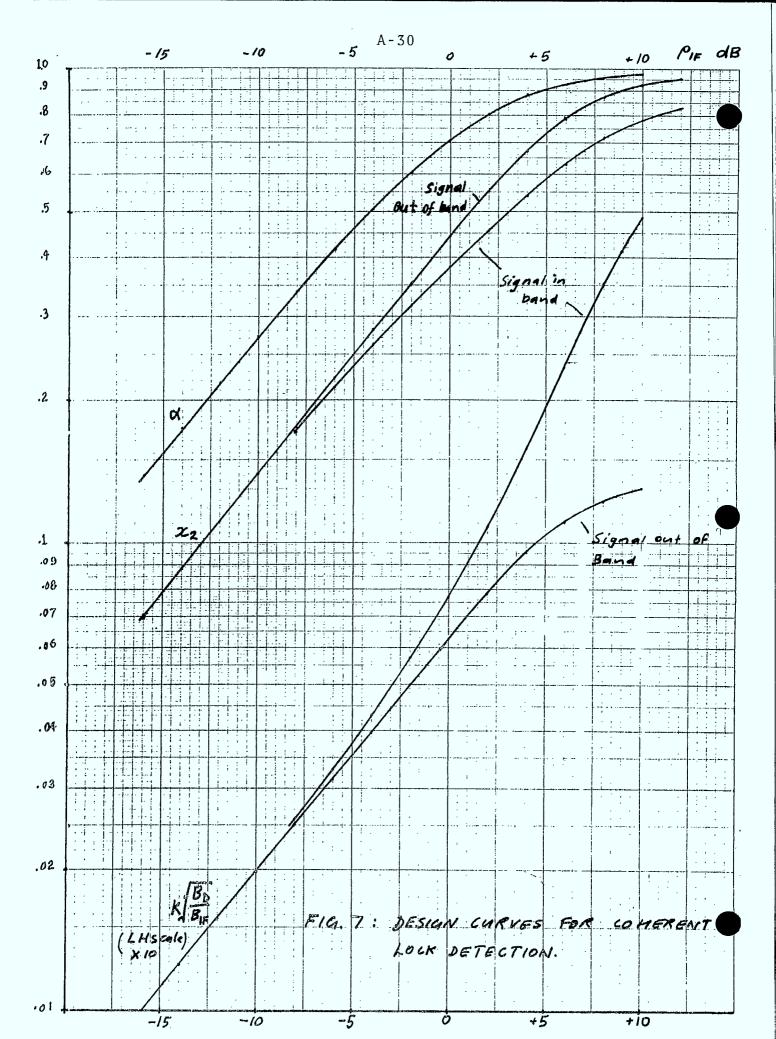

Appendix A to this report examines quantitatively the behaviour and application of PLL's in signal detection. Results from that appendix have been applied in the following discussion which addresses problems in detecting and locking to an ELT signal in an environment of background noise and other ELT signals.

## II.2.1 System Constraints

The carrier power-to-noise spectral density ratio is at least 26 dB-Hz and this value will be used in estimating (in a worst case sense) the performance of the system.

The noise is taken to be uniformly distributed over the band which is 12 kHz in width. The signal-to-noise ratio of the carrier in a band of  $\Omega$  Hz is then

SNR =  $26 - 10 \log \Omega dB$

which yields

| Filter Noise |       |

|--------------|-------|

| Bandwidth    | SNR   |

| $_{ m Hz}$   | dB    |

| 12,000       | -14,8 |

| 1,000        | - 4.0 |

| 100          | + 6.0 |

| 50           | 9,0   |

| 30           | 11.2  |

| 10           | 16,0  |

| 5            | 19.0  |

| 1            | 26.0  |

In order that the characteristics of the PLL not depend on the amplitude of the ELT signal, it would be desirable that the bandwidth of the "IF filter" preceding the PLL be no more than 200 Hz which would yield an output SNR of +3 dB.

Were a single detection device to be used to cover the 12 kHz band in 10 seconds, an ELT signal would be in the bandwidth of a 200 Hz IF filter 167 milliseconds, and the filter would have a "response time" of 5 milliseconds. Thus, there would be ample time for the filter to respond. Were a 100 Hz filter used, the time would be 84 msec. and 10 msec. respectively and again there would be no problem with response time.

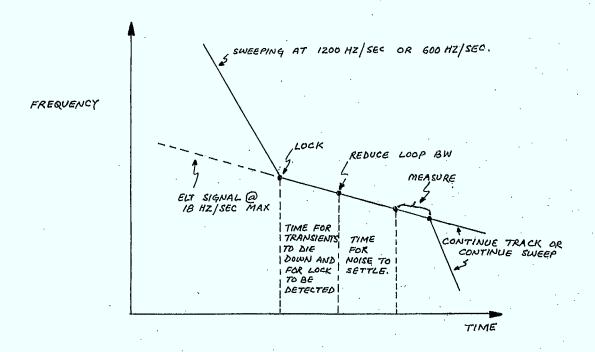

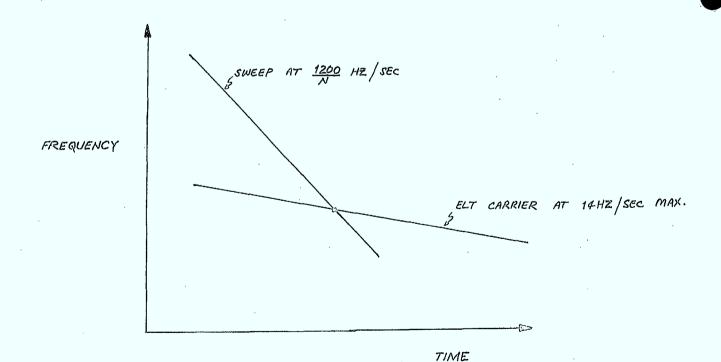

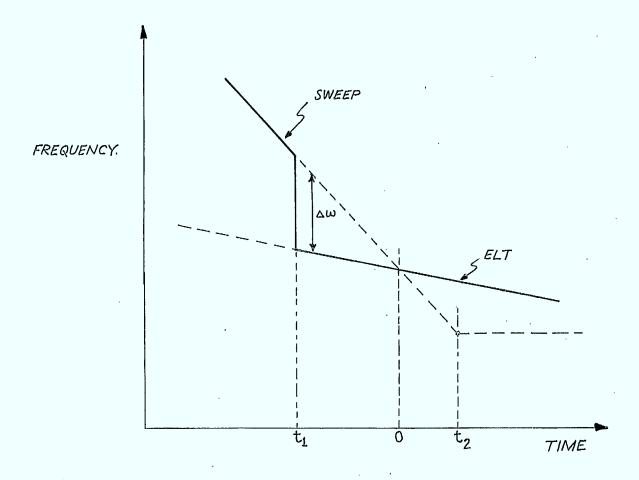

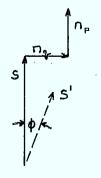

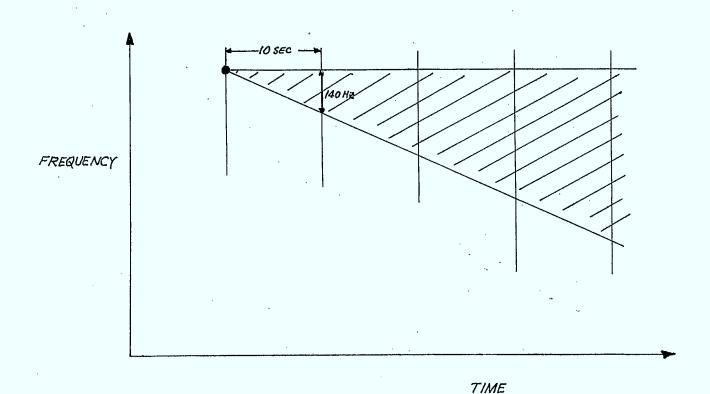

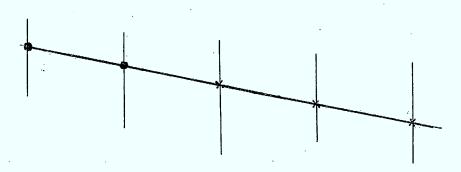

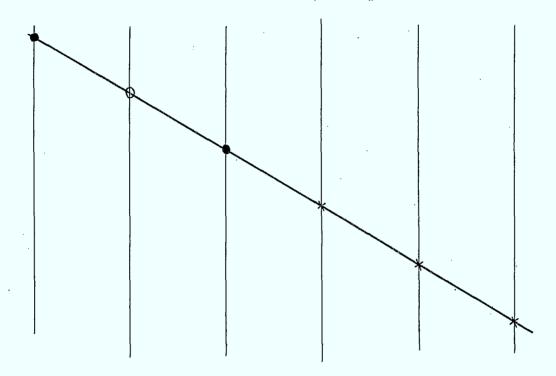

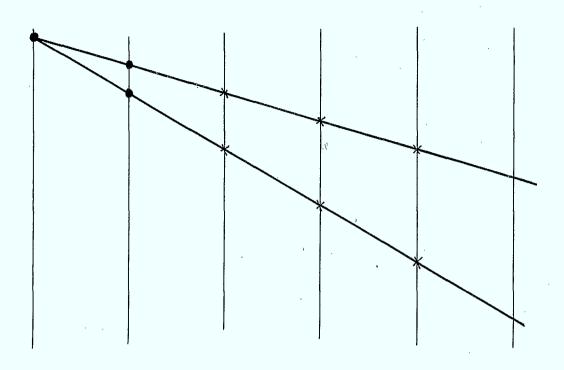

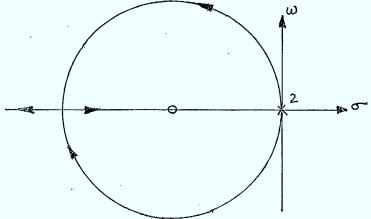

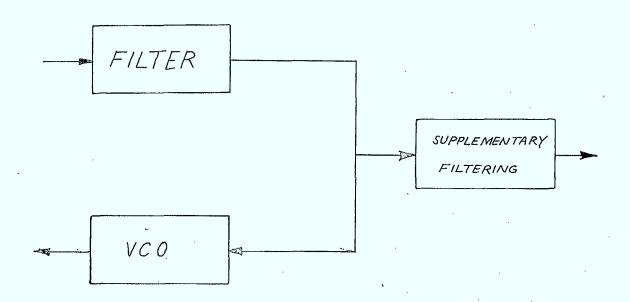

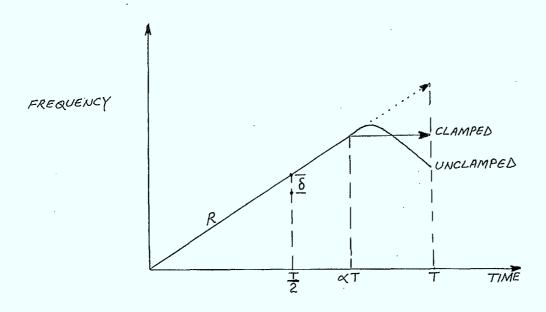

Several alternative methods for acquisition, tracking and measurement are possible, but in general the sequence of operations in time-frequency would be as shown in the following diagram:

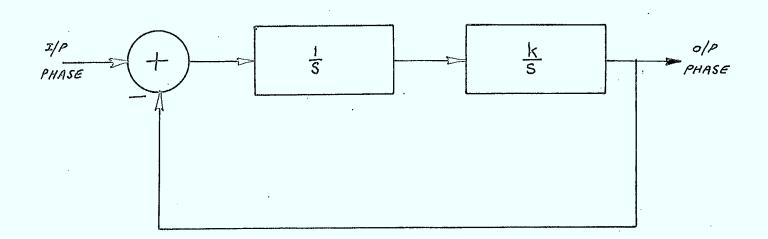

and a critical requirement on the PLL is its capability to track the doppler. The steady state tracking error for the second order loop best able to track a frequency ramp is

$$\emptyset_e = \frac{R}{\omega_n^2}$$

where  $\emptyset_e$  is in radians, R is the doppler rate in radians/sec, and  $\omega_n$  is the loop natural frequency in radians/sec. This yields errors:

| Loop Natural<br>Frequency | Tracking Error |

|---------------------------|----------------|

| Hertz                     | Degrees        |

| 100                       | 0.013          |

| 16                        | 0.50           |

| 5                         | 5.1            |

| 1                         | 128            |

| .1                        | 12,800         |

for the maximum doppler rate of 14 Hz/sec. Clearly the minimum natural frequency is a few Hertz, which limits the maximum SNR from the loop.

To estimate this maximum, the noise in the loop will be reviewed again. For comparable results it will be assumed that the natural frequency  $\omega_n$  in radians/second is numerically equal to the PLL noise bandwidth in Hertz, and this yields the following loop SNR's:

| Natura1 | Frequency | SNR  |

|---------|-----------|------|

| Her     | tz        | dB   |

| 16      |           | 6.0  |

| 5       |           | 11.0 |

| 1       |           | 18.0 |

| 0 .     | , 3       | 23.3 |

| 0.      | . 1       | 28.0 |

It would appear that an SNR in excess of 10 dB, but less than 18 dB, is to be expected.

The question of acquisition time also requires more detailed consideration. If lock is identified by synchronous detection, then the time constant of the detection system will determine how quickly lock can be determined. The minimum time is influenced by the signal to noise ratio, but the tracking rate and the settling time are also relevant, as the previous diagram shows.

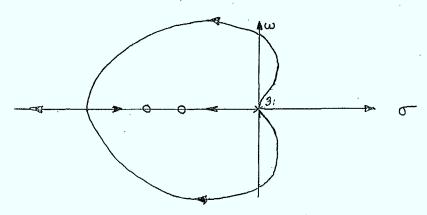

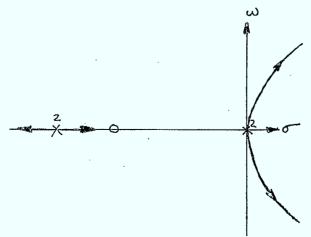

### II.2.2 The Process of Lock Acquisition

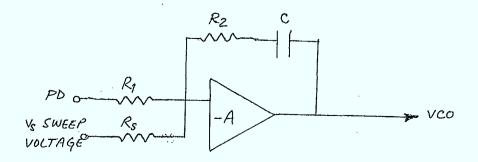

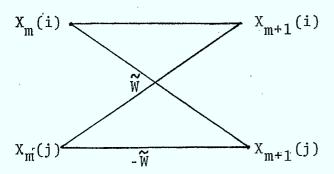

Two major approaches for acquiring lock are available. In the sweeping method, the incoming signal is mixed with a reference sinusoid whose frequency is linearly swept, continuously or in fine steps, across the 12 kHz range. The stepping approach calls for the frequency of the reference to be moved across that same range in coarse steps which are, however, not so large that "instantaneous" lock is precluded. In both cases, when lock is detected the stepping or sweeping process is halted.