P

91 C655 C6663 1982

The Intelligent Use of Technology

> REVIEW OF MULTIPROCESSOR SYSTEMS AND THEIR SPACECRAFT APPLICATIONS

# REVIEW OF MULTIPROCESSOR SYSTEMS

AND THEIR SPACECRAFT APPLICATIONS

Industry Canada Library Queen JUL 201998 Industrie Canada Bibliothèque Queen

l l

Report No. INT-82-14 March 1982

A

Approved

Authors: Mr. J.G. Ouimet Dr. C. Laferriere Dr. S.A. Mahmoud Mr. T.F. Martin

Approved by: Dr. S.A. Mahmoud

Department of Communications

Government Gouvernement

du Canada

of Canada

DOC CONTRACTOR REPORT

DOC-CR-SP-82-044

DEPARTMENT OF COMMUNICATIONS - OTTAWA - CANADA

SPACE PROGRAM

TITLE: Review Of Multiprocessor Systems And Their

Spacecraft Applications

AUTHOR(S): J. Ouimet

C. Laferriere

S.A. Mahmoud

T. Martin

ISSUED BY CONTRACTOR AS REPORT NO: INT-82-14

PREPARED BY: Intellitech Canada Ltd.

352 MacLaren St. Ottawa, Ontario K2P OM6

DEPARTMENT OF SUPPLY AND SERVICES CONTRACT NO: 3ER.36100-1-0273

SN: OER81-03151

DOC SCIENTIFIC AUTHORITY: R.A. Millar

CLASSIFICATION: Unclassified

This report presents the views of the author(s). Publication of this report does not constitute DOC approval of the reports findings or conclusions. This report is available outside the department by special arrangement.

Preface

This work was performed for the Department of Communications, Communication Research Centre, under DSS Contract No. OER81-03151, entitled "Computer-Aided Engineering Tools for Spacecraft Multi-Microprocessor Design", from September 15, 1981 to March 31, 1982. This report is one of the following four contract deliverables:

1. Executive Summary

2. Report #1 - Review of Multiprocessor Systems and their Spacecraft Applications.

3. Report #2 - A Survey of Computer-Aided Engineering (CAE) Tools for

the Design and Simulation of Multiprocessor Systems.

4. Report #3 - The Definition and Specification of an Integrated Set

of CAE Tools for Spacecraft Multiprocessor System Design.

## Acknowledgement

The study team gratefully acknowledges the technical guidance of Mr. R.A. Millar of the Communications Research Centre. His knowledge and experience in the field of computer simulation of spacecraft systems have contributed to the quality of the work and provided a constant source of encouragement to the study team.

As well, the study team wishes to thank Mr. J.M. Savoie of C.R.C. for many fruitful discussions and critical reviews.

# TABLE OF CONTENTS

| · .   | :       |      |       |         |           |          |                   |                                       | •               |               |               | Page No. |

|-------|---------|------|-------|---------|-----------|----------|-------------------|---------------------------------------|-----------------|---------------|---------------|----------|

|       |         | ÷    | 1.    | TNTR    | ODUCTION  |          |                   |                                       |                 |               |               | . l      |

|       |         |      |       |         |           |          |                   | · · · · · · · · · · · · · · · · · · · |                 | •••••         |               | · · ·    |

|       |         | · .  |       | -       |           | •        |                   |                                       |                 |               |               |          |

|       |         |      | 2.    | ARCH    | ITECTURAL | CONFIGU  | RATIONS (         | OF MULTI                              | MICROPRO        | CESSOR        | s             | •• 3     |

| • •   | •       |      |       | 2.1     | Introduc  | tion     |                   |                                       |                 |               |               | 3        |

|       |         | •    |       | 2.2     |           |          | f Distrit         |                                       |                 |               |               |          |

|       |         | ·. · |       | 2.3     |           |          | of Distri         |                                       |                 |               |               |          |

|       |         |      |       | 2.4     |           |          | istribute         |                                       |                 |               |               |          |

| . *   | · · ·   |      |       | 2.5     | Conclusi  | ons      |                   |                                       |                 | • • • • • •   |               | • • 14   |

|       | •       |      |       | •       | <u>`</u>  |          |                   | · .                                   |                 |               |               |          |

|       | · ·     |      | _     | · · · · |           |          |                   |                                       | · .             |               |               |          |

|       |         |      | 3.    | SURV    | EY OF DIS | TRIBUTED | OPERATIN          | NG SYSTE                              | M TECHNI        | QUES .        | ••••          | •• 15    |

|       | •       |      |       | 3.1     | Introduc  | tion     |                   |                                       |                 |               |               | 15       |

| · · · | ·       | •    |       | 3.2     |           |          |                   |                                       |                 |               |               |          |

|       |         |      | • • • | 3.3     |           |          | rce Manag         |                                       |                 |               |               |          |

|       | •       | ÷.,  |       | 3.4     | Real-tim  | e Interr | upts              |                                       |                 |               |               |          |

| · .   | • .     |      |       | 3.5     |           |          | ••••              |                                       |                 |               |               |          |

| •     |         |      |       | 3.6     | Applicab  | ility to | Special           | Purpose                               | Compute         | ers           |               | •• 28    |

| •     | •       |      |       |         | •         |          |                   |                                       | -               | · · ·         | · · ·         |          |

|       |         |      |       | CIID    | EY OF CUR |          | ͲͳϦϿϴϹͲϾϤ         |                                       |                 | ·             |               | 30       |

| •     | · · ·   |      | 4•    | SUKV    | EI OF CUK | AGNI MUL | TTEROOD25         | SOK FROJ.                             | CUD •••         | · • • • • •.• |               | •• 30    |

|       |         |      | · ·   | 4.1     | General   | Descript | ion               |                                       | • • • • • • • • |               |               | 30       |

|       |         |      | •     | 4.2     |           |          | ysis of 1         |                                       |                 |               |               |          |

|       |         |      |       | •       | ÷         |          |                   |                                       |                 |               | • • •         | · .      |

|       |         |      |       |         |           |          | •                 |                                       |                 |               | · · · ·       | •        |

|       |         |      | 5.    | THE     | SPACECRAF | T APPLIC | ATION ENV         | IRONMEN'                              | <b>r</b>        | · • • • • • • | • • • • • • • | •• 47    |

| •     |         |      | •     | 5.1     | Tatadaa   | tion     |                   |                                       |                 |               |               | 17       |

|       |         |      |       | 5.2     |           |          | rements           |                                       |                 |               |               |          |

|       |         | •    |       | 5.3     |           |          | ters              |                                       |                 |               |               |          |

|       |         | · ·  |       | 5.4     |           |          | ft Syster         |                                       |                 |               |               |          |

| •     |         |      |       | 5.5     | Automati  |          |                   |                                       |                 |               |               |          |

|       |         |      |       |         | *         |          |                   |                                       |                 |               |               |          |

|       |         |      | 6     | CIIMM   |           |          |                   |                                       |                 | •             | ,             | 67       |

| `     |         |      | 0.    | SOLW    | IARY      |          | • • • • • • • • • | • • • • • • • •                       | • • • • • • • • | • • • • • •   | ••••          | •• 07    |

|       |         |      |       |         |           |          | · .               |                                       |                 |               | ÷.            |          |

|       |         |      | REF   | ERENC   | ES        |          |                   |                                       |                 |               |               | •• 68    |

| · .   |         |      |       |         |           |          |                   |                                       |                 |               |               |          |

| •     | •       |      |       |         |           |          |                   |                                       |                 | •             |               | •        |

| •     | н.<br>1 | · ·  |       |         |           |          | :                 |                                       | •               |               | · · ·         |          |

| • .   |         |      |       |         |           |          |                   |                                       |                 |               |               |          |

|       | :       | 3    |       |         |           |          |                   |                                       |                 |               | · . · · ·     |          |

|       |         |      | · .   | •       |           |          | · ·               | •                                     |                 |               |               |          |

|       |         |      |       |         | •         |          |                   |                                       |                 |               |               |          |

|       |         |      |       |         | •         |          |                   |                                       |                 |               |               |          |

| · · · |         | .`   | . *   | ·       |           |          |                   | • .                                   |                 | ۰.            |               |          |

|       |         |      |       |         |           |          |                   | •                                     |                 |               |               |          |

#### 1. INTRODUCTION

Interest in multiprocessor and distributed intelligence computer systems has increased dramatically in recent years. This interest has been fostered by the availability of microprocessors with even increasing performance/price ratios and the expected emergence of monolithic systems with still high capabilities in the near future.

A significant advantage of distributed systems is their potential capability for providing very high reliability through redundancies and dynamic reconfiguration. Since reliability is of prime concern in the design of spacecraft systems, distributed systems have received lot of attention from spacecraft computer systems designers. The aim of this report is to review the technology of distributed systems and to establish their applicability to the spacecraft environment.

Section 2 of the report presents different alternative architectures for multimicroprocessors. These achitectures differ in the degree and method of coupling processors and memories, their complexity and ability in isolating faulty components. The survey of the full spectrum of architectures was conducted irrespective of the number of processors involved in the architecture. Both architectures commonly used today, and those in theoretical or design development stages, are presented.

Section 3 surveys briefly the techniques of designing and implementing Executive Software for multimicroprocessors. The emphasis is placed on the general functions of the executive and the approaches followed for scheduling tasks and resources and for handling intertask communications and external interfaces.

.1

Section 4 surveys five research activities reported in the literature which culminated in the development of five experimental prototype multimicroprocessors for avionics and spacecraft applications. These are: the Cm\* system (Carnegie Mellon University), FTMP (Draper Laboratory), SIFT (Stanford Research Institute), UDS (Jet Propulsion Laboratory) and the french Matra system.

Section 5 is an introduction to the field of spacecraft computing technology. The aim of the section is to establish a baseline description of the environment with attempting to be an exhaustive discussion of the subject. The section first reviews the processing requirements of spacecrafts, outlines the processors used, then exemplifies the subject through the use of the example spacecrafts and finally presents some apparent trends in the development of these computers.

### 2. ARCHITECTURES FOR DISTRIBUTED SYSTEMS

### 2.1 Introduction

Significant advances in the development of powerful and reliable computer systems have been based largely on the use of multiple processors. A system which consists of several processors can be implemented in many variations. Normally these variations fall within one of the following broad classifications:

- a. Multiprocessors: Defined as a computer employing two or more processing units under integrated control. The multiprocessor has the capability for the direct sharing of memory and I/O devices by all processors under control of a single operating system.

- b. Multiple Computer-Network: These systems are composed of a number of heterogeneous computers loosely coupled, sometimes only by communications links. Each processor operates independently under control of its own operating system, sharing data with other systems as required.

- c. Multiple Computer-Distributed: These systems fall somewhere between multiprocessors and networks. Jensen defines them as "... a multiplicity of processors that are physically and logically interconnected to form a single system in which overall executive control is exercised through the co-operation of decentralized system elements". [JENS78]

These definitions should not be viewed as the basis for absolute classification; it is possible to find examples of systems that do not fit exactly into a single definition and hence combine features from more than one definition. The real purpose of these definitions is to provide a framework for structuring the following discussions on architectures. Before proceeding further, it is necessary to point out that a review of all the different architectures in the three categories would require an effort beyond the scope of this work. The review conducted here in concerned primarily with multiprocessor architectures that are used in spacecraft applications. Since many multimicroprocessors and most multiprocessor systems designed for spacecraft applications fit within the 'distributed system' group, we will limit our discussions to this category.

This section will first present a classification structure (taxonomy) used to define the environment of distributed systems. It will then examine some architectures that have been implemented. Because of its special nature, the issue of fault-tolerance in architectures will be examined more closely.

#### 2.2 Classification of Distributed Systems

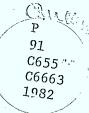

There have been a number of taxonomies proposed to classify distributed systems. An evaluation of these various classification schemes [JENS76] has concluded that the Andersen/Jensen taxonomy [ANDE75] is probably the most complete. It is based upon the decomposition of systems into three primary elements:

- a) a Processing Element (PE) which is a hardware unit in which processes can execute;

- b) a Path which is the medium on which messages are transferred without alteration; and

- c) a Switch which intervenes between the sender and receiver of a message by modifying the message (eg. changing its destination

address) and/or by routing to one of a number of alternative paths.

To implement a distributed system, a designer must select various interconnection parameters. A tree structure can be used to represent these alternatives as shown in Figure 2.1. This tree is divided into four decisional levels. These levels are:

- a) Link Level: A designer may select to use direct links between all <u>PE's or may choose to use a switch, thereby implementing an</u> Indirect link architecture. As discussed above, the switch will perform address translation (eg. from a logical address to a physical one) or perform a routing function.

- b) Routing Level: For Indirect architectures, the designer may select to centralize the switching/routing function to one entity or decentralize to a number of entities.

- c) Path Level: At this level, message transfer paths can be shared or dedicated. A shared path is one to which more than two PE's are connected.

- d) <u>Architecture Level</u>: The final level of the tree are the nodes which represent specific architectures.

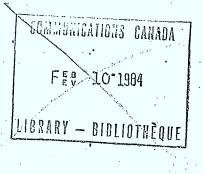

Figure 2.2 gives a number of examples of various architectures possible. The name of each example is preceeded by a three-character classification where the first letter indicates whether the link is . direct (D) or indirect (I), whether routing is non-existent (.), centralized (C) or decentralized (D) and whether paths are dedicated

(D) or shared (S).

#### 2.3 Implementations of Distributed Architectures

Most of the earlier implementations of multi-processor systems were done for large machines (IBM 360 and 370 families; Burroughs 5000 and 6000 families, CDC 6000, etc.) in order to improve their throughput. Most of these machines included a shared memory and used one of the following interconnection mechanisms between the processors, memory and I/O processors:

a) common bus (Figure 2.2d)

b) crossbar switch

c) multi-port memory (Figure 2.2c)

Enslow [ENSL77] surveys these architectures and the existing implementations (in 1977). He also analyzes the interconnection mechanisms and gives a list of advantages/disadvantages for each (see Table 2.1). Although these multi-processor systems do not meet the definition of Distributed Systems because of the extremely tight coupling between the components, much of the analytical work done for those systems still remains valid.

More recent work in distributed systems has been directed primarily towards three architectures: bus, circuit switches and indirect. The use of single and multiple buses has been extensive, particularly for fault-tolerant systems (see Sections 2.4 and 4). Some theoretical foundations for bus structures have also appeared [KINN78], [HAMA80]. A number of indirect networks (Indirect Decentralized Dedicated) have also been proposed; these include

binary-trees [HORO81], [HARR79]; X-trees [DESP79]; hypercubes [WITT81]; cluster structures [WU81], etc. Considerable research is also now taking place in the area of switching where efforts have been underway for some time to replace the crossbar switches with switches having all its advantages but none of its disadvantages. In particular, some of the switches which have been proposed could eventually be fully implemented in VLSI. Some of these types of switches are known as delta [DIAS81], omega, banyan [FRAN81], etc.

[FENG79].

|                                                                       | · · · · · · · · · · · · · · · · · · ·                                      |                                                                             |  |  |  |

|-----------------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|--|--|

| Common Bus                                                            | Crossbar Switch                                                            | Multi-port Memory                                                           |  |  |  |

|                                                                       |                                                                            |                                                                             |  |  |  |

|                                                                       |                                                                            |                                                                             |  |  |  |

| Lowest overall cost                                                   | Functional units remain single and cheap                                   | Requires most expen-<br>sive memory units                                   |  |  |  |

|                                                                       |                                                                            |                                                                             |  |  |  |

| Least complex                                                         | Most complex inter-<br>connection                                          | Complex interconnection                                                     |  |  |  |

| Easy to add or remove                                                 | Expansion simple to implement                                              | Extremely difficult to<br>expand since design is<br>normally size-dependent |  |  |  |

|                                                                       |                                                                            |                                                                             |  |  |  |

| Limited bus throughput                                                | Highest total transfer rate capability                                     | Potential for high<br>transfer rate                                         |  |  |  |

|                                                                       |                                                                            |                                                                             |  |  |  |

| Failure at bus is a<br>catastrophic system<br>failure                 | Switch partitioning alters<br>inherent redundancy and<br>reconfigurability |                                                                             |  |  |  |

| A single unit can de-<br>grade the performance<br>of the whole system | Easy to remove malfunc-<br>tioning units                                   |                                                                             |  |  |  |

|                                                                       |                                                                            |                                                                             |  |  |  |

| Lowest system efficiency<br>of three types                            | Potential for highest syste<br>efficiency                                  | m                                                                           |  |  |  |

|                                                                       |                                                                            |                                                                             |  |  |  |

|                                                                       |                                                                            |                                                                             |  |  |  |

|                                                                       |                                                                            |                                                                             |  |  |  |

MULTI-PROCESSOR ORGANIZATION

#### 2.4 Fault Tolerant Distributed Architectures

Some applications, real-time systems in particular, require a high degree of reliability. The computer system is expected to withstand individual component failures while continuing the processing function. These 'Fault Tolerant' (FT) computer systems have specially tailored architectures designed to provide this feature.

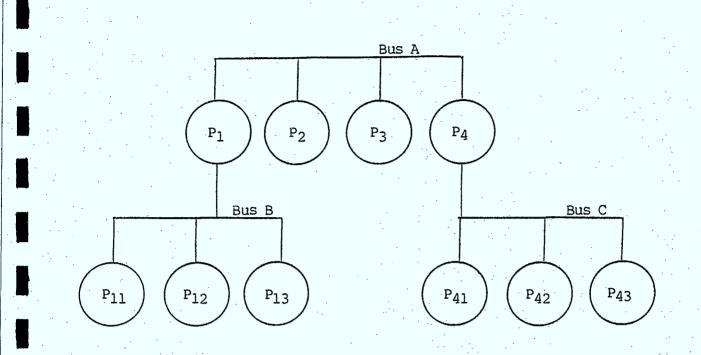

The Global (or common) Bus architecture has been widely used in the design of many FT systems. Some of the better known systems under development (FTMP, SIFT, UDS) use the bus concept. There is some speculation that the global bus will remain the basic architecture for aerospace computers [CARB77], though probably with the addition of multiple level of buses [CROS77]; Figure 2.3 is an example of a duallevel bus system.

As shown in Table 2.1, the common bus concept has a number of inherent disadvantages. In particular, fault tolerance is not an implicit quality of buses; in order to provide FT, designers must replicate the buses and design complex bus interface mechanisms to provide the many-CPU to many-buses connections required and to prevent any one CPU from disabling a bus. Additionally, bus architectures are very prone to bottlenecks. This has not been a problem so far since the amount of data passed between processors has always been relatively small. However, as processors are added and as dataintensive functions (eg. real-time image processing) come on board, bus architectures may reach limit points.

Notes: - If  $P_2$  can address  $P_{13}$ , this is an IDS architecture.

- If  $P_2$  does not know  $P_{11-13}$  exist but rather talks to  $P_1$  as if it was the final processor, then this is the equivalent of three D.S architectures.

# FIGURE 2.3 - DUAL-BUS LEVEL ARCHITECTURE

Because of these problems, many attempts have been made at implementing other types of architectures in  $\mathbf{FT}$ systems. Architectures implemented are, with examples:

a) Bus(D.S) - FTMP, SIFT, UDS: (see Section 4) - SARGOS: the computer system of the ground stations was designed for high reliability. SARGOS is a system to be used to identify and locate distress beacons by satellite. [DESW81] the Experimental Polyprocessor System - EPOS: designed circa 1979 at Toshiba in Japan uses multiple independent common buses. [MAEK79] - C.vmp:

b) Cluster Networks (IDS Bus window)

- Matra System, Cm\*: (see Section 4)

- MuTEAM: a multimicroprocessor system now in development in Italy, designed for embedded realtime applications using loosely coupled clusters of bus connected microprocessors. [GIOF81]

c) Ring (D.DLoop)

- DDLCN:

а fault-tolerant reconfigurable network using dual loops and tri-state control logic interface developed circa 1979 at the Ohio State University. [WOLF79]

d) Complete Interconnect (D.D)

e) Irregular Structure (IDD)

a reliable and survivable real-time system - RHEA: designed in France in 1976, it uses a twolevel structure composed of an irregular network controlling groups of local star structures. [POWE78]

f) Circuit Switched (IDD Regular)

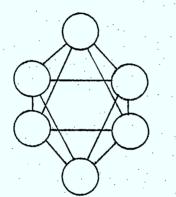

Other IDD Regular architectures such as Tree structures [LIU80], [KWAN81] and partially meshed Rings have also been studied. This last architecture (Figure 2.4), in particular, has been analyzed in detail by Pradhan [PRAD81a], [PRAD81b], [PRAD81c] and others [GRIN80] and found to present a very high degree of fault-tolerance and faultdiagnosability as well as having good distributed systems properties (low complexity, extensability, partitionability, etc.)

FIGURE 2.4 - A PARTIALLY MESHED RING

### 2.5 Conclusions

From this review of Distributed Architectures, a few concluding remarks can be drawn:

- a. The 'common bus' is still the most widely used implementation architecture, especially for FT systems.

- b. Multiple bus levels (bus window) and loop architectures are at the design and test stage.

- c. Radically new architectures (meshed rings, tree, etc.) are now being theoretically studied and show promise for long-term implementations.

## 3.1 Introduction

A distributed system is an amalgamation of individual computing entities with the aim of forming a combined single computer system. Activities take place in the individual entities concurrently and overall co-ordination is the responsibility of a decentralized executive. This definition of distributed computer system is that of [JENS78].

The decentralized executive is what binds together the collection of processing entities. This binding can be done in different ways, ranging from very tight coupling to very loose co-ordination. It should be emphasized that the executive itself is a control algorithm. As such, it can be implemented in hardware, in software, or as is more likely, in a mixture of both.

Hardwired executives (ie. executives whose algorithms are implemented in hardware) can be found in systems such as array processors or multiprocessor systems where the processors are tightly coupled to the executive through a common bus. At the opposite end of the spectrum, systems such as distributed databases can be found running on a loosely coupled network of computers. In a distributed database, the database management systems makes the distributed nature of the system totally transparent to the users. The database management system is a purely software entity and works in conjunction

with some communications facilities to provide the required coordination. So far, the executive has been characterized by:

- 1. An algorithm (or set of algorithms) implementing a policy (eg. loose or tight control scheme), and by

- 2. An implementation such as hardware, software or a combination of both.

The software part of the implementation of the executive is called the operating system (O/S). The purpose of this section is to highlight the software methods used in providing an executive for distributed systems. This will be done in the context of a general purpose distributed operating system, in order to cover most of the mechanisms involved.

From a user point of view, the purpose of an operating system is to manage efficiently the computer resources under its control. More specifically, the O/S is involved in the following:

1. Management of Computing Resources

Managing computing resources involves scheduling and synchronization of processes. A process in an instantiation of a program. The latter is a series of instructions residing in core or in a core image file on disk while the former is the action of executing the instructions. A process in characterized by its Process Control Block (PCB) which contains the program counter, the stack pointer, the program status word, some registers, etc. In a typical computing entity, many processes may be competing for access to the processor, that is, actively running as opposed to

waiting to run. The O/S will oversee the running of the processes and will ensure that each is given a fair share of the processor.

Processes which execute concurrently may want to co-operate among themselves. To this end, interprocess synchronization facilities should be provided by the O/S. It should also be realized that, because synchronization involves blocking and unblocking of processes, it shares the use of some conceptual mechanisms with the O/S scheduling facilities.

Also of importance is how the O/S will handle real time interrupts which are demands for service originating from devices. This area is relevant to control system such as on-board processors for spacecraft.

2. Management of Physical Resources

Management of physical resources is mostly concerned with the allocation (or granting) of hardware devices to processes. Several items are covered under the heading hardware devices; such items can be: more memory space for a process, access to fast floating point processor, control over a disk drive, or a printer, etc.

The result of the management activities of the O/S is a set of services. As explained before, those services constitute the sofware part of the executive of a distributed system. The remainder of this section will elaborate on each type of service with appropriate reference to relevant experimental systems.

In any system supporting concurrent execution (real or contrived) of processes, facilities have to exist to enable processes to cooperate among themselves in the execution of certain functions (eg. managing communication devices, storage devices, etc.). This is the purpose of synchronization. As a system service, synchronization strongly reflects the type of control structure embodied by the hardware. For example, synchronization through semaphores can be provided in a tightly coupled system with shared memory, whereas a message-based synchronization scheme is more suited to a loosely coupled environment.

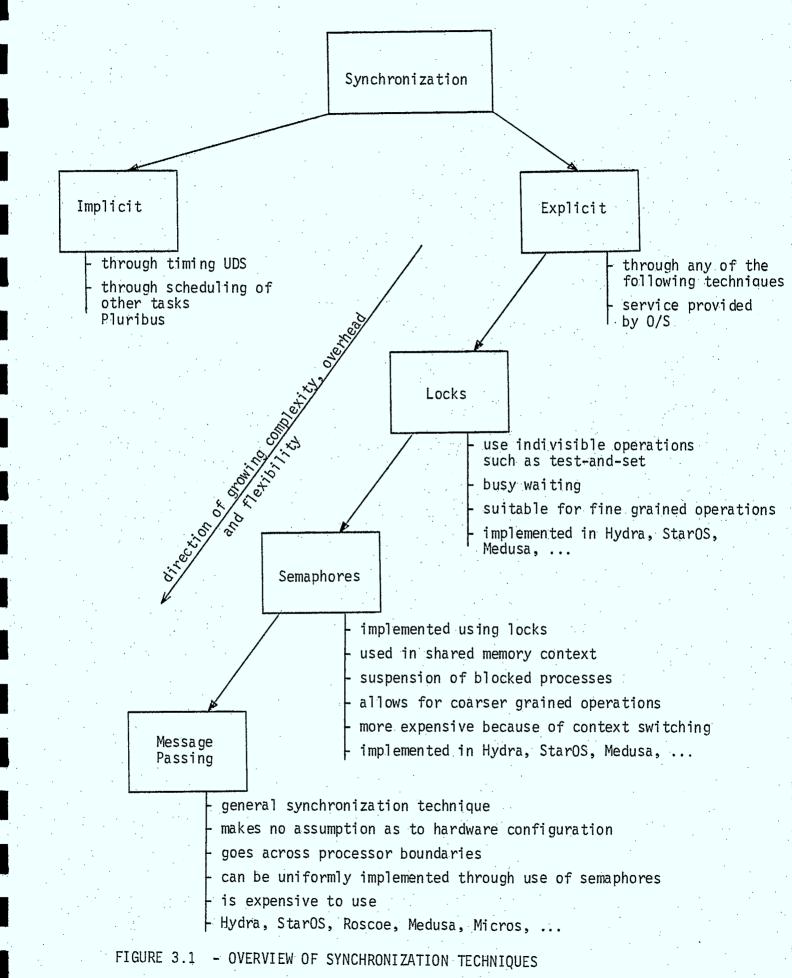

Synchronization can be broadly classified into two types:

# 1. Implicit Synchronization

As the name implies, the O/S does not provide synchronization since it is either provided by the environment or by another O/S service. An example of synchronization being provided by the environment is a system [RENN78a] in which all activities are deemed to be synchronous. In fact, time provides synchronization. In some other sysems [KATS78] [ORNS75], synchronization is implicitly provided to a "strip" (a strip is a short, noninterruptible process), through scheduling of another strip.

### 2. Explicit Synchronization

In this case, synchronization is truly a system service implemented in software by various techniques. The performance of these techniques will depend upon factors such as: hardware configuration, granularity of the activities of processes using the synchronization service, frequency of utilization, etc. [JONE80].

When dealing with explicit synchronization techniques, it should be remembered that lower level techniques are always necessary at a processing entity; synchronization across processing entity boundaries may necessitate a different type of mechanism which will be implemented using the former techniques. Explicit synchronization techniques will then be listed by order of sophistication.

a) Locks

The implementation of locks relies on the availability of an indivisible operation (eg. test-and-set) at a given processing entity. Locks are typically used for co-resident processes having fine granularity of activities and those processes will usually implement a policy of "Busy Waiting", that is, will constantly check the value of the lock until they acquire it. Two observations can be made in connection with locks:

- i) A "Busy Waiting" policy implies that a blocked process will keep the use of the processor. Other processes will not be permitted to run, even though no constructive work is done by the blocked process.

- ii) While a process is blocked on a lock, the resources it is currently holding are not available to others. Releasing those resources, however, is not necessarily the best policy since the process would eventually have to re-acquire them at a later time.

### b) Semaphores

Based upon locks, a more constructive approach can be taken in which the blocked processes are suspended and put in a special queue. A semaphore is the implementation of that policy and is represented by a mechanism such as a lock and an associated queue. Semaphores release the processing element from a blocked process and give other processes a chance to run. However, the policy involves context switching from one process to another. Obviously, if the cost of context switching is higher than that of blocking for a given process then blocking is preferable; in other situations the reverse may be true. Furthermore, the resources claimed by a suspended process are still being inaccesible to others.

### c) Message Passing

Message passing is a synchronization technique in which the sending and receiving of messages (not necessarily their contents) define blocking and re-start for a process. Local to a given processing entity, this technique can be implemented by using semaphores which in turn are implemented partly with locks. The synchronization object is the mailbox which allows processes to wait (ie. suspend themselves) for the arrival of a message and to send a message to another mailbox (ie. signal another process). Clearly, synchronization through message passing is very well suited to a distributed environment since:

i) it goes across processor boundaries,

ii) it is not bound to any physical set-up, but

iii) it is understandably very much slower than semaphores.

The flexibility of message passing synchronization made it the choice as a basic synchronization technique for many experimental distributed operating systems such as [WULF74], [WULF75], [LEVI75], [COHE75], [JONE79], [OUST80], [SOLO79], [WITT80]. It has to be mentioned, however, that in these systems, the O/S maintains a consistent interface for all the processes. In actual fact, two processes synchronizing each other through message passing may be using a single semaphore if they are resident in the same processor or may be exchanging messages (on a bus, through shared memory or through a parallel serial interface) if the processes are at different or processors. From the point of view of uniformity, offering one type of service and making its implementation transparent to the users seems a good policy, inasmuch as the O/S has the necessary flexibility.

A summary of synchronization techniques is shown in Figure 3.1, together with the systems using them. At this point, a brief description of some of those systems is in order.

- 1. The Unified Data System (UDS) [RENN78a], [RENN80] is not an operating system as such, but a multiprocessor organization in which all operations are synchronous. It is on that basis that it is included in this section. Further description is to be found in Section 4.

- 2. Pluribus (circa 1975) [KATS78], [ORNS75] is a computer system composed of three types of elements, called busses: processorbusses, memory-busses and I/O busses. Those busses can be con-

figured to form a multiple processor system. Some special features are important to the hardware structure:

- a) all activities are on the form of short, non-interruptible processes called strips.

- b) synchronization among strips is through the scheduling of other strip(s).

- c) scheduling, for both real-time interrupts and software initiated requests, is through insertion of the identity of the desired strip(s) into a hardware queue called a Pseudo-Interrupt Device (PID).

Pluribus and UDS are examples of systems where a sizable portion of the distributed executive is implemented by hardware structures.

3. Hydra [WULF74], [WULF75], [LEVI75], [COHE75] is the operating system developed for the C.mmp [WULF72]. This multiple computer system was developed at Carnegie-Mellon University and is composed of a number of DEC PDP-11/40 with separate memory modules. Memories and processors are interconnected by means of a 16x16 crosspoint switch so that all of the available memory is accessible by any one of the processors. The C.mmp (circa 1970) is the earliest of such developments at Carnegie-Mellon and precedes the Cm\* both in age and in concepts.

Hydra, the operating system of C.mmp was given the responsibility of managing the latter's resources. Consequently, Hydra provides facilities for managing the total memory space, for synchronizing

2.2

and scheduling processes, and for allocating hardware resources. Support of the concepts of capabilities and objects is provided by Hydra in an effort to increase security and data confinement.

- 4. StarOS [JONE79] and Medusa [OUST80] are operating systems designed for the Cm\* (circa 1975) multiprocessor system. (Cm\* is described in detail in Section 4.) StarOS was the first O/S developed for the Cm\*. Medusa was developed later, based upon the experience gained with StarO/S. Both StarO/S and Medusa are close to Hydra in terms of general philosophy of operations. The services they provide are, in general, similar to Hydra's, except where hardware differences between C.mmp and Cm\* either require extra facilities or make some services redundant.

- 5. Other multiple processor operating systems are in existence, such as Roscoe [SOL079] for the Rochester Intelligent Gateway and Micros [WITT80] for Micronet. The services they provide are very similar to those of StarOS or Medusa.

# 3.3 Scheduling and Resource Management

The problems of scheduling the execution of processes and of allocating the existing resources efficiently are both concerned with the performance of a multiprocessor system. On a more general level, the task of management takes on two aspects: static and dynamic.

1. Static management is mostly concerned with how to distribute the code and data structures of O/S utilities and other processes among the various memory modules in the system. It can be seen readily that static management is extremely dependent upon the hardware configuration worked with. In highly specialized systems or in systems with only global memory (eg. [WULF72]), all processors (or group of processors dedicated to the same functions), have copies of all O/S utilities and other processes. In more general systems (eg. [FULL78]) memories are arranged in a mix of local and global partitions. The cost (speed and contention) of accessing local memory is much less than that of accessing global memory, indicating that the distribution policy and by extension the configuration itself, will play an important role in determining the performance (speed, throughput, response time) of the system.

There also exist other systems (eg. [WITT80] in which all memories are local to some processors. In those systems, as opposed to special purpose systems, processes with non-resident code have to be executed elsewhere and are started through a remote procedure call (eg. using message passing constructs).

Static management is therefore concerned with the allocation of O/S utilities and other processes into the various types of memories with the aims of: a) keeping as much free space as possible for each processor, and b) maximizing the speed of execution of O/S processes and others. These aims were, as mentioned previously, dependent upon the local/global memory arrangement and how much of each type was provided.

2. Dynamic management is concerned with the scheduling of processes and the management of resources.

a) Scheduling of processes can be accomplished implicitly in systems (eg. [RENN78a]) where time is used to schedule synchronous processes. This approach is conceptually simple but only applies to a narrow range of applications and is also inflexible. Explicit scheduling can be accomplished by queue(s) of ready to run processes (called ready to run queue). Scheduling can then be implemented as a single or multiple ready to run queue. One possible arrangement is to have independent ready to run queues at each processor with static priorities assigned to queues and dynamic priorities assigned to processes.

In tightly coupled systems, scheduling involves a context switch to the O/S and then a second context switch to the chosen process. In the case of a remote call in a loosely coupled system, messages will have to be exchanged and extra context switching at the recipient processor will have to be done. The resulting overhead indicates that scheduling should be tailored to the need of the application so as to minimize unnecessary context switching and to avoid inter-processor calls as much as possible.

b) Resource management is responsible for the dynamic allocation of resources (eg. devices, buffers, etc.) to processes. The overall performance of the system is very sensitive to bad decisions made by the resource allocation module. In most special purpose systems, however, the management policy is de-

termined statically at design time. This policy would likely accept excess capacity in terms of resources and computing power in order to minimize contention.

Another concern of the resource management module is that of deadlock. In special purpose very rigid systems, possibilities of deadlock can be totally eliminated whereas in more flexible ones distributed deadlock detection has to be used. Deadlock detection is an added overhead that can prove expensive in terms of actual processing time used, of memory space for the data structures and of lost capacity resulting from blocked or preempted processes.

# 3.4 Real-time Interrupts

The handling of real-time interrupts from devices requesting service is an important concern in an environment such as a spacecraft. Interrupts introduce a non-deterministic element in the execution of software. This makes the validation and debugging of the software an arduous task.

Interrupts have been masked out entirely in systems such as UDS [RENN78a] in which continuous polling of devices is used instead. This approach, albeit less responsive, makes it conceptually easy to assess the correctness of the software. Similarly in Pluribus, interrupts have limited effects on the system; all an interrupt service routine can do is to arrange for the scheduling of a "strip".

Other systems which are more general in nature accept demand interrupts but try to contain their effects and isolate their data structures by limiting the scope of the interrupt service routines.

## 3.5 Reliability

In the design of hardware components, physical distribution is the important criterion whereas in the design of the executive, logical distribution takes precedence [JONE80]. In the execution of a function, it is evident that if software processes are dependent upon one another to achieve success, failure of one of them will incapacitate the rest. Logical distribution requires that such dependency should not exist or at least should be kept to a minimum. Reliability can also be enhanced by having several instances of a particular process (at various processors) and by having them operate in a fashion analogous to back-up processors in hardware. It is also interesting to note that there is a trade-off between hardware and software reliability in the sense that software algorithms can be designed to enhance the overall system reliability.

### 3.6 Applicability to Special Purpose Processors

Special purpose processors, whether of the uni- or multiprocessor type, will have well defined functions to perform. In the case of multiple processor systems, the precise definition of their functions will allow for simpler designs and for some degree of optimization.

The software mechanisms presented hitherto addressed co-ordination problems of a general nature, hence their complexity. Special purpose systems will deal with a fixed population of processes whose needs will be known a priori. It should be pointed out that the basic requirements for synchronization and scheduling will still apply to

these systems.

# 4. SURVEY OF CURRENT MULTIPROPROCESSOR PROJECTS FOR SPACECRAFT AND AIRCRAFT CONTROL

This section examines the design philosophy and general architectural concepts of five different multimicroprocessor systems that have been reported recently in various publications. Section 4.1 examines the general software and hardware features and the basic design methodology of these systems. A comparative study of their architecture is then presented in Section 4.2.

### 4.1 General Description

A survey of recent publications in the field of spacecraft and avionics multimicroprocessors revealed substantial research effort, concentrated mainly in building prototype systems and examining their use to realize certain properties. Such properties include software verifiability, fault tolerance, survivability under hostile conditions, self-checking capabilities, etc. Most prominent among these projects are the following four systems:

(1) Cm\*

(2) FTMP

(3) SIFT

(4) UDS

(5) Matra System

A brief description of the above systems follows. The details of these systems can be found in the list of references at the end of this section.

#### (1) <u>Cm\* [SIEW78],[JONE77],[SWAN77]</u>

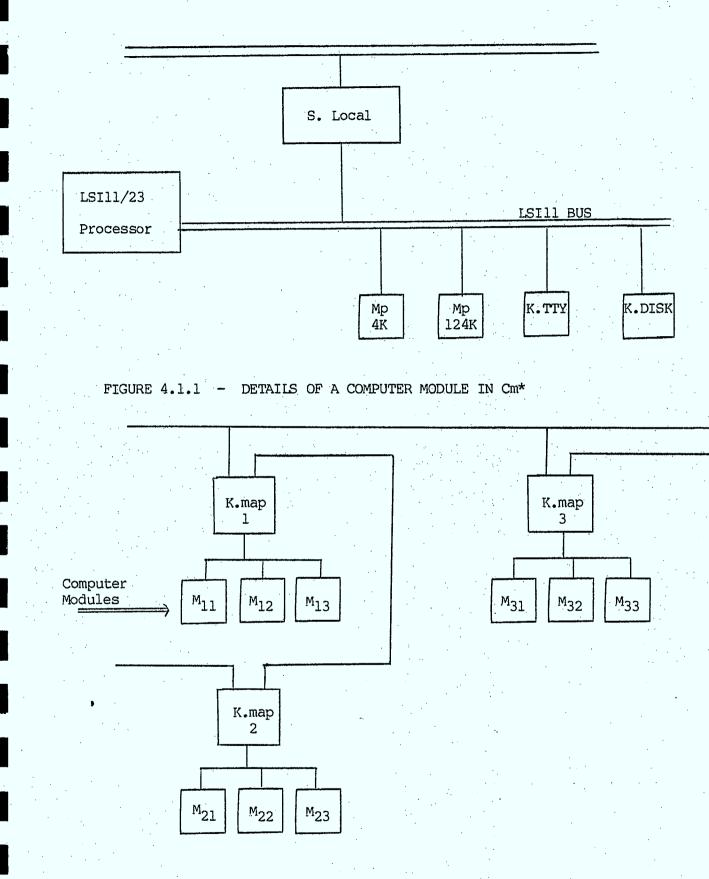

The Cm\* multimicroprocessor system was designed and implemented at Carnegie-Mellon University. The system is based on interconnecting a set of LSI11/23 processors in a configuration which permits extensibility, address mapping and software pruning of faulty components.

The Cm\* structure consists of a set of computer modules grouped into clusters. The clusters are connected by a mapping controller which is a programmable high performance processor. Thus each controller is shared by several computer modules connected to it by a common bus via simple interfaces (referred to by S.local).

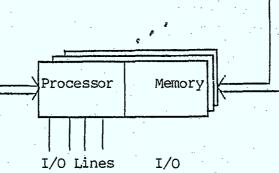

Figure 4.1.1 gives the details of each computer module. Figure 4.1.2 illustrates a simple three cluster network. The mapping controller is termed K.map, while each computer module is marked by M.

Cm\* has a 2<sup>28</sup> byte segmented virtual address space. The addressing structure provides considerable support for operating system primitives such as control switching and interprocess message transmission. Each processor in Cm\* uses the top page in its address space (page 15) for direct program interaction with K.map. However, each of the 16 pages of the processor provides a

window into the system-wide  $2^{28}$  byte virtual address space and can be independently bound to different segments in the virtual address space.

A significant feature of the Cm\* system is that all communication is performed by packet switching, except at the local memory bus level, where conventional circuit switching is used. These buses are allocated only for the period required to transfer data. The data is latched at each interface, rather than establishing a continuous circuit from the source to the destination. This approach is taken in order to increase bus utilization and avoid bus allocation deadlocks.

FIGURE 4.1.2 - A SIMPLE Cm\* THREE-CLUSTER NETWORK

#### (2) FTMP [HOPK76b], [HOPK78]

The FTMP (Fault-Tolerant Multiprocessor) is a computer architecture that has been studied, simulated and emulated at the Draper Laboratory (Cambridge, MA). The target of the project is to achieve an overall failure rate less than  $10^{-9}$  failures per hour, provided that maintenance is available within no more than ten hours per dispatch.

The FTMP structure is composed of an arbitrary number of processor modules with local memories and an arbitrary number of memory modules, interconnected by redundant serial buses. Modules are associated into groups of three to perform triply redundant functions. All data is distributed synchronously and in triplicate, and every module contains a voting element to mask bus disagreements. All modules contain special circuits to create logical and physical boundaries to halt the propagation of faults from one module to another. The essential features of the FTMP system are summarized in the following.

#### Redundant Organization

All activities in FTMP are conducted by triads of modules and triads of buses. A module triad is formed by associating any three like modules with one another. Thus any module can serve as a spare for any triad. A three member subset of N bus lines is chosen on a quasistatic basis to serve as a bus triad. These three lines are connected to a voter in each module, thus constituting a TMR element. The three active bus lines carry three independently generated versions of the data, each version

coming from a different member of the triad that is transmitting the data.

#### Functional Resource Allocation

The programmer of the FTMP system sees this multiprocessor as a machine for executing job steps. The procedure for each job step is written in a suitable language and resides in common memory. Each job step is typically scheduled to occur at a given time or following a given event. The relevant dispatch data for each scheduled job is kept in a queue, where it is frequently examined to see if the job step is eligible to be run or invoked. The frequent examination is conducted by processors that have completed their earlier assignments, and are available to undertake new ones. Thus job allocation is dynamic and adjustable according to memory load distribution and module failures.

#### Synchronization

FTMP employs tight synchronization using a common time reference that supports hardware voting, allows instantaneous validation of internal data, configuration control and in some cases interface data. The problem of maintaining a continuous timing reference is solved by a fault-tolerant redundant clocking arrangement using voltage-controlled crystal oscillators.

In addition to the above features, the FTMP system contains several fault detection and isolation mechanisms. The voting process which exists at the triad level is the primary tool for detecting any faulty behaviour during the operation of the system [HOPK75b], [HOPK78].

#### (3) <u>SIFT [WENS78], [WENS72]</u>

SIFT (Software Implemented Fault Tolerance) is an ultrareliable computer for critical aircraft control application. The prototype system was developed and tested at SRI. This includes error detection and correction, diagnosis, reconfiguration and the isolation of a faulty unit.

The structure of the SIFT hardware is shown in Figure 4.1.3. Computing is carried out by the main processors. Each processor's results are stored in the main memory associated with the processor. The I/O processors have much smaller computational and memory capacities than the main processors as they connect to the input and output units of the system (eg. actuators and sensors of the aircraft). Each processor and memory form a processing module. Each module is connected to a multiple bus system.

The SIFT system executes a set of tasks, each of which consists of a sequence of iterations. The input data to each iteration of a task is the output data produced by the previous iteration of some collection of tasks. The input and output of the entire system is accomplished by tasks executed in the I/O processors. Reliability is accomplished by having a number of processors executing redundantly the same iteration of a task; the output of this iteration is placed in the memory of the processor. A processor which uses the output of this iteration determines its value by examining the output of each processor executing it and taking a majority decision. Errors are discovered in cases of disagreement and are used by the executive to discover faulty

units and reconfigure the system. The processors in SIFT are loosely synchronized (eg. to within 50 microseconds) since we only need to ensure that the different processors allocated to a task are executing the same iteration.

Fault isolation in SIFT is accomplished by several mechanisms. Each unit is autonomous with its own control. This makes it possible to ignore improper control signals and to time-out signals that never arrive. Protection against corruption of data is provided by the way in which units can communicate. A processing module can read data from any processing module's memory, but it can write only into its own memory. Finally, each processor receives multiple copies of the data; each copy is obtained from a different memory over a different bus, and the processor uses majority voting to obtain a correct version of the data.

Formal models for scheduling strategies, software verification and reliability prediction were developed for SIFT in order to guarantee a correct operation within acceptable performance limits [WENS78], [WENS72].

Controllers Processor

Bus

Processing Modules

Memory

FIGURE 4.1.3 - STRUCTURE OF THE SIFT SYSTEM

Multi-buses

#### (4) UDS [RENN78b], [RENN80]

The UDS architecture consists of a set of microcomputer modules connected by a redundant set of intercommunications buses. Two types of modules exist: terminal modules (TM) and high level modules (HLM). The TM interfaces with other modules in two ways: 1) it receives a single Real-Time Interrupt (RTI) which is common to all modules and which is used for timing and synchronization, and 2) each TM is interfaced to all intercommunications buses. DMA techniques are used to enter and extract data from the TM. A TM cannot initiate bus communications. An external HLM enters commands, data and timing information into the memory of the TM.

HLM's are responsible for coordinating the processing which is carried out in the remote TM's, for control of intercommunications over the bus systems, and for high-level processing such as data compression and decision making.

The UDS design is oriented towards moving "hard core" items whose failure can cause catastrophic system failure. For example, the buses are made independent to avoid any common failure mechanisms. Independent clocks are used within each module; the clocks are synchronized by the common RTI. As well, the UDS architecture prevents the TM's from propagating their errors to the HLM's since the TM's are not allowed to issue communication calls to the common bus system. Details of the UDS architecture and the software executive are available in [8] and [9].

The design of the UDS emphasizes testability and simplicity, even at the expense of the computer power and memory utilization.

These aspects are manifested in the following architectural features:

<u>Computer Utilization</u>: Low speed and memory utilization enables the designer to concentrate on the correctness of his code rather than its efficiency.

Error Confinement: Most TM's will be performing dedicated low level functions and are not permitted to modify the memory of other modules.

<u>Minimization of Interrupts</u>: Demand interrupts are avoided whenever possible. This may limit I/O response to milliseconds rather than microseconds. However, it leads to more predictable operation, is more easily modified, and allows for software selfdefence.

<u>Control Hierarchy</u>: As explained previously, the HLM's control the TM's. The programs in the TM's are self-synchronized to process the data when they arrive and place results in their memories for subsequent extraction by the high-level computer.

Other simplification features in the UDS architecture include synchronous communications, timing hierarchy and I/O timing granularity to simplify software modifications.

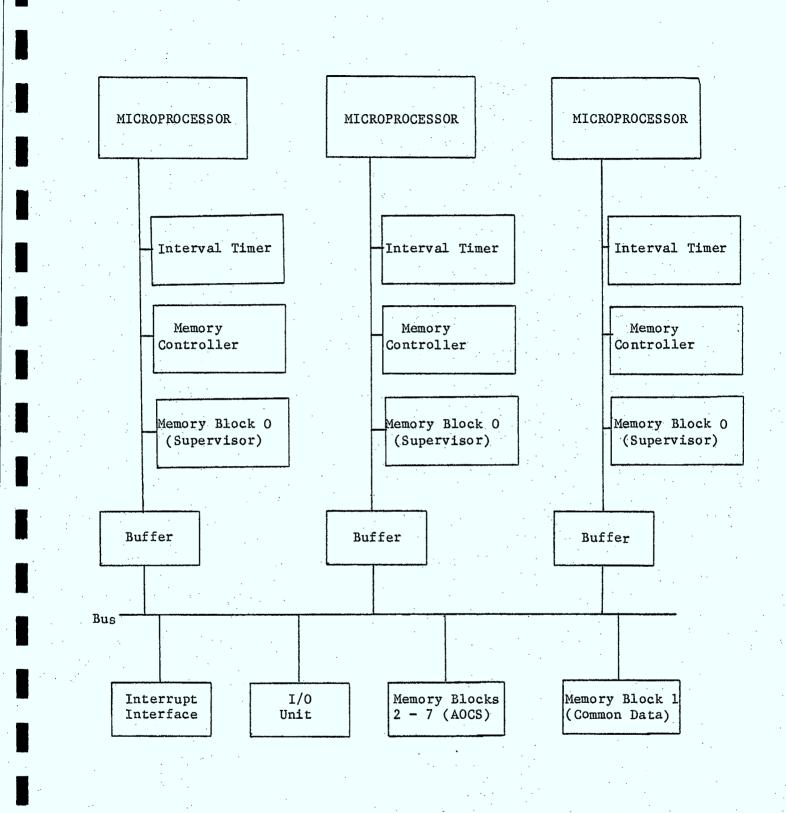

### (5) Matra System [SOUB77]

The Matra organization, in France, has developped a multimicroprocessor system designed to automate the signal and data processing functions at Attitude and Orbit Control Subsystems

(AOCS). The system consists of three microprocessors (INTERSIL 6100) using a common bus, some local memory for the processor supervisor programs and global memory for the common data areas and for the AOCS programs (Figure 4.1.4).

Each processor is controlled by its supervisor program. When idle, a processor will read the common supervisor table to determine which pending task has the highest priority. The processor will then that task. The task may generate the activator of other tasks, through the common supervisor table. External interrupts and Real Time Clock Interval pulses can also activate tasks. The Real Time Clocks are used for local processor monitoring and overall process synchronization.

Fault detection is implemented using:

- a. local watch-dog with each processor (software)

- b. processing function watch-dogs (sofware)

- c. monitoring and reconfiguration capability of local Interval times

- d. self-test programs.

The system is capable of surviving failures through:

- a. halting and disengaging a failed processor

- b. reallocating memory module tables in case of a failure in memory blocks 2 to 7

- c. switching the redundant memory module implemented for block 1 (common data).

FIGURE 4.1.4 - MATRA MULTI-PROCESSOR BLOCK DIAGRAM

#### 4.2 Architectural Features of Three Systems

Out of the systems discussed in the previous section, three were designed for a high reliability environment: FTMP, SIFT and the JPL system. Although similar in concept, these systems represent a wide ranging set of implementations. A study of these features will therefore allow a better understanding of the design of upcoming spacecraft systems.

Table 4.2.1 is a condensed comparison of these three systems:

- a) <u>Memory</u>: The JPL and SIFT both have memory which is local to each processor while the FTMP uses mostly global memory (it has small local caches for improved performance). The way the memory is structured has two main influences: the mechanisms for passing information between tasks will be very different and the use of the buses by the FTMP will be much larger, leading to potentially earlier saturation.

- b) <u>Number of Bus Types</u>: Both the JPL and SIFT use only one type of bus while the FTMP uses two buses in an attempt to minimize the potential bus loading problem.

- c) <u>Bus Replication</u>: Buses in the FTMP and SIFT are quintuply replicated while the JPL triplicates its bus.

- d) <u>Bus Controllers</u>: The SIFT uses dedicated devices as Bus Controllers while the JPL lets a task in one of the general purpose

processors carry out the bus arbitration functions. The FTMP appears to use a decentralized bus control mechanism which resides in each device.

- e) <u>Module Types</u>: The FTMP uses three different sorts of module devices (memory, processor/cache and I/O access). The SIFT also uses three types of modules though they are somewhat different (bus control, processor/memory and I/O processor). The JPL attempts to limit its module types to one by designing an all-purpose buildingblock; although this is an interesting concept which simplifies implementation, it is also potentially restrictive.

- In FTMP, fault detection is done by having f) Fault Detection: hardware devices compare the output of three (fixed number) processors which carry out the same computations simultaneously; if not all processors agree, voting is used to determine which result is correct and which processor is faulty; this comparison/voting is performed for each instruction. In SIFT, a similar comparison/voting mechanism is used, however, it is implemented in software; it allows a variable number of processors to participate and it is carried out at fixed regular intervals, rather than for every instruction. In the JPL system, a hardware implemented verification mechanism is imbedded within each bus and is therefore transparent to other modules.

- g) <u>Processor Synchronization</u>: Although in all three systems cooperating tasks must be closely synchronized with respect to each other, the actual inter-processor synchronization is implemented differently in all three processors. In FTMP, since hardware

voting for each instruction is carried out, the processors within triads must be very tightly synchronized. In SIFT, synchronization is only required at the voting interval level while in JPL, since no voting takes place, processor synchronization is not required (of course, task synchronization still is).

| Fe            | System<br>ature                | FTMP                                     | SIFT                                                     | JPL                                   |

|---------------|--------------------------------|------------------------------------------|----------------------------------------------------------|---------------------------------------|

| a)            | Memory                         | Global; processors<br>a local cache memo |                                                          | Local                                 |

| b)            | Bus Types<br>Types             | Memory buses<br>Interface buses          | Global Bus                                               | Global Bus                            |

| c)            | Bus Replication                | 5                                        | 5                                                        | 3                                     |

| d)            | Bus Controller                 | No                                       | Yes                                                      | Imbedded                              |

| e)            | Module Types                   | Memory<br>Processor/cache<br>I/O Access  | Bus Control<br>Processor/Mem.<br>I/O Proc.               | Building<br>Block                     |

|               |                                |                                          | <u></u>                                                  |                                       |

| f)            | Fault Detection                | By Voting, in Hard<br>in triads          | ware, By Voting, in Sol<br>variable no. of<br>processors |                                       |

| g)            | Processor Syn-<br>chronization | Tight                                    | Loose, by interva                                        | al Not required                       |

| • <del></del> |                                | ······································   |                                                          | · · · · · · · · · · · · · · · · · · · |

#### 5. THE SPACECRAFT APPLICATION ENVIRONMENT

#### 5.1 Introduction

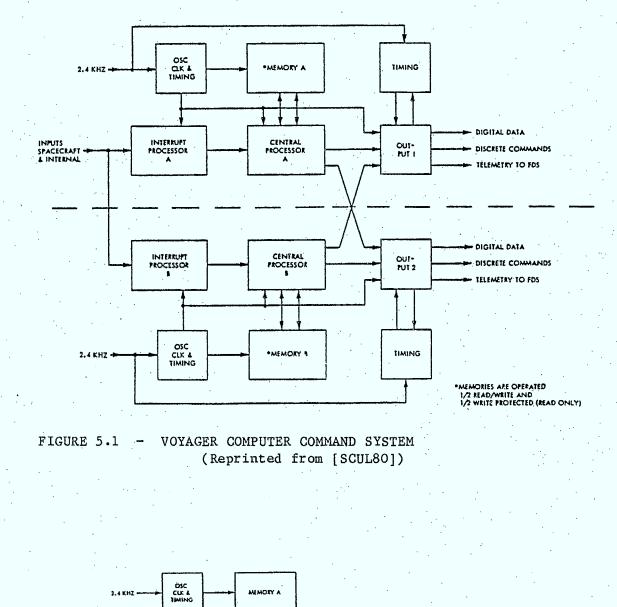

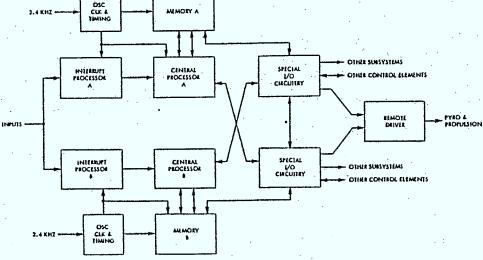

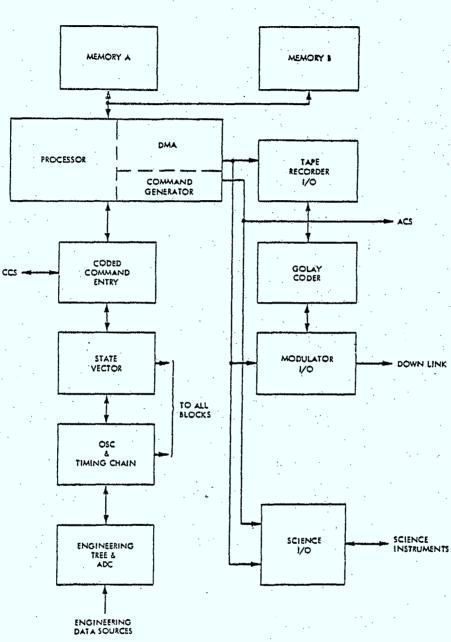

This section will introduce the computing environment of spacecraft applications. It is not intended as a comprehensive review of spacecraft systems but rather as a short introduction to the concepts, techniques and elements of spacecraft computers. The next four subsections will:

- a. present the processing requirements in terms of functions and of resources needed,

- b. describe some of the computers that have been or will be used in spacecrafts,

- c. illustrate the use of these processors through two example systems: Voyageur and Galileo,

- d. conclude by discussing the present trends of spacecraft processing including the NASA NEEDS program.

#### 5.2 Processing Requirements

Typically, the on-board computing functions include [HOLC80]:

- a. pyro/propulsion control,

- b. mechanical actuator control,

- c. radio control,

- d. data handling,

- e. command decoding,

- f. instrument control,

- g. attitude control,

- h. data compression.

Some functions, such as actuator or instrument control, involve issuance of predetermined command sequences, while functions such as attitude control involve complex calculations based upon readings from instruments (eg. star tractors and gyros). The developers of the Fault Tolerant Spacecraft Computer determined that attitude control and navigation were the primary functions requiring automation and that it was their processing requiremens that most affected the FTSC design; Table 5.1 summarizes the FTSC designers' conclusions regarding the on-orbit computation requirements [FANE77]. The support of the science instruments is another main area of computer utilization; the computers must be capable of reading all the data provided by the instruments and perform the necessary calculations to prepare the data for transmission. Table 5.2 gives the maximum data rate and the amount of memory space required for each of the instruments of the Galileo orbiter spacecraft.

| Task                     | Program and data<br>memory, words | Computation rate,<br>operations/sec |  |

|--------------------------|-----------------------------------|-------------------------------------|--|

| Attitude control and     | 2,343                             | 68,250                              |  |

| pointing                 |                                   |                                     |  |

| Telemetry                | 1,281                             | 13,692                              |  |

| Commanding               | 912                               | 19,500                              |  |

| Supervisor               | 2,909                             | 33,042                              |  |

| Subsystem management     | 876                               | 1,875                               |  |

| and recovery             |                                   |                                     |  |

| Subtotal                 | 8,321                             | 136,359                             |  |

| Payload processing       | 6,500                             | 60,000                              |  |

| Subtotal                 | 6,500                             | 60,000                              |  |

| Memory size without      | lok                               | • • •                               |  |

| payload processing       |                                   |                                     |  |

| Memory size with         | 16K                               | • • •                               |  |

| payload processing       |                                   |                                     |  |

| Maximum computation rate | • • •                             | 200,000                             |  |

|                          |                                   |                                     |  |

# TABLE 5.1 - ESTIMATED ON-BOARD PROCESSING REQUIREMENTS (Reprinted from [FANE77])

| Instrument                        | Maximum<br>Data Rate,<br>bits/s | <u>Memory Size</u><br>ROM | e, kbytes<br>RAM |

|-----------------------------------|---------------------------------|---------------------------|------------------|

| Solid state imaging (SSI)         | 768.                            | 3                         | 3.5              |

| Near infrared mapping             | , · ·                           | * .<br>*                  | ·                |

| spectrometer (NIMS)               | 11.52                           | 3                         | 1.75             |

| Photopolarimeter radiometer (PPR) | 0.18                            | 4                         | 0.25             |

| Ultraviolet spectrometer (UVS)    | 1.0                             | <b>-</b>                  | 0.75             |

| Energetic particle detector (EPD) | 0.92                            | 6                         | 3                |

| Plasma subsystem (PLS)            | 0.60                            | 8                         | 8                |

| Magnetometer (MAG)                | 0.24                            | 4                         | 4 .              |

| Dust detector subsystem (DDS)     | 0.024                           | 3                         | · 2              |

| Plasma wave subsystems (PWS)      | 645.                            |                           | 0.25             |

| (contains no microprocessor)      |                                 |                           |                  |

## TABLE 5.2 - GALILEO SCIENCE INSTRUMENT SUMMARY

The first general purpose programmable computers to be flown onboard spacecraft were centralized machines monitoring and controlling the various subsystems. More recent spacecraft designs have taken the approach of using more than one computer and of having computers dedicated to certain functions such as attitude control, while under the overall command of a central command and control computer.

The two extremes in spacecraft computer architecture are the completely centralized and the fully distributed. The completely centralized approach has one large central computer serving the needs of all the subsystems, while the fully distributed approach consists of several small computers serving these needs as peers. Neither of these approaches is optimal for the space environment. The highly centralized system calls for significant data communication overheads and complex resource allocations within the computer while a fully distributed system can result in system coordination problems [HOPK75a].

The approach being taken in current spacecraft computer system architectures is very much a combination of these two extremes which permits capitalizing on most of the advantages of both. The Unified Data System (UDS) which is the model for the command computer system aboard the most recent satellite, Galileo, is representative of that approach (see Section 4). Table 5.3 lists the characteristics of some current on-board computer system [STAK81] while Table 5.4 details the

characteristics of the processors available for space missions in the

1980s [HOLC80].

| Com | outer             | Mission           | Number | Memory Size<br>(in bits) | туре           | Processor        | Tim  |

|-----|-------------------|-------------------|--------|--------------------------|----------------|------------------|------|

| 1.  | NSSC-1            | MMS (Generic)     | 1 or 2 | 8-64K by 18              | CORE           | TTL              | 1.   |

| 2.  | AOP               | Landsat-B/C       | 1      | 4K by 18                 |                | TTL              |      |

| 3.  | NSSC-1            | SMM               | 2      | 48K by 18                | PWM            | TTL              | 1.   |

| 4.  | AOP               | IUE               | 2      | 12K by 18                | PWM            | TTL              | 1.   |

| 5.  | OBP               | OAO-C             | 1      | 16K by 18                | CORE           | DTL              | 2.   |

| 6.  | DOC               | ATS-6             | 2      | 4K by 18                 | PWM            | LPTTL            | 5.   |

| 7.  | GCSC              | Viking Lander     | 2      | 18K by 18                | PWM            | LPTTL            | 5.   |

| 8.  | CCS               | Viking Orbiter    | 2      | 8K by 18                 | PWM            |                  | •    |

| 9.  | FDS               | MJS-77 (Voyageur) | 2      | 8K by 18                 | CMOS           | DMOS             | 2.   |

| 10. | CCS               | MJS-77 (Voyageur) | .2     | 8K by 18                 | PWM            | ·                | 1.   |

| 11. | AACS              | MJS-77 (Voyageur) | 2      | 8K by 18                 | PWM            |                  | - 1. |

| 12. | SCP-234           | TIROS-N           | 2      | 18K by 18                | CMOS           | CMOS             | 2.   |

| 13. | SCP-234<br>(USAF) | Block 5D          | 2      | 16K by 18                | CMOS           | CMOS             | -    |

| 14. | COSMAC            | AMSAT Phase IIIB  | 1      | 16K by 18                | CMOS           | CMOS             | 1    |

| 15. | NSSC-1*           | Landsat-D         | 2      | 64K by 18                | CORE           | TTL              | 1.   |

| 16. | AAC-16ms*         | Galileo           | 2      | 32K by 18                | CMOS           | LSI bit<br>slice | 0    |

| 17. | CDC 469           | HEAO              | 2      | 16K by 18                | Plated<br>Wire | PMOS/LSI         |      |

#### Abbreviations

| CMOS   | - Complementary Metal-Oxide Semiconductor     |

|--------|-----------------------------------------------|

| DTL    | - Diode-Transisor Logic                       |

| LPTTL  | - Low-Power Transisor-Transistor Logic        |

| PWM    | - Plated-Wire Memory                          |

| TTL    | - Transistor-Transistor Logic                 |

| AACS . | - Attitude and Articulation Control Subsystem |

| AOP    | - Advanced On-board Processor = NSSC-1        |

| CCS    | - Computer Command Subsystem                  |

| DOC    | - Digital Operations Controller               |

| FDS    | - Flight Data Subsystem                       |

| OBP    | - On-board Processor                          |

| NSSC-1 | - NASA Standard Spacecraft Computer           |

| MMS    | - Multimission Modular Spacecraft             |

| SMM    | - Solar Maximum Mission                       |

| IUE    | - International Ultraviolet Explorer          |

| OAO    | - Orbiting Astronomical Observatory           |

| ATS-6  | - Applications Technology Satellite           |

|        | 0,                                            |

TABLE 5.3

CHARACTERISTICS OF SOME CURRENT ON-BOARD COMPUTER SYSTEMS (from [STAK81])

| Identification                         | IBM<br>NSSC-I                              | Martin M.<br>Enhanced<br>NSSC-I | IBM<br>NSSC-II             | Litton<br>4516E            | App. Tech.<br>ATAC-16MS |

|----------------------------------------|--------------------------------------------|---------------------------------|----------------------------|----------------------------|-------------------------|

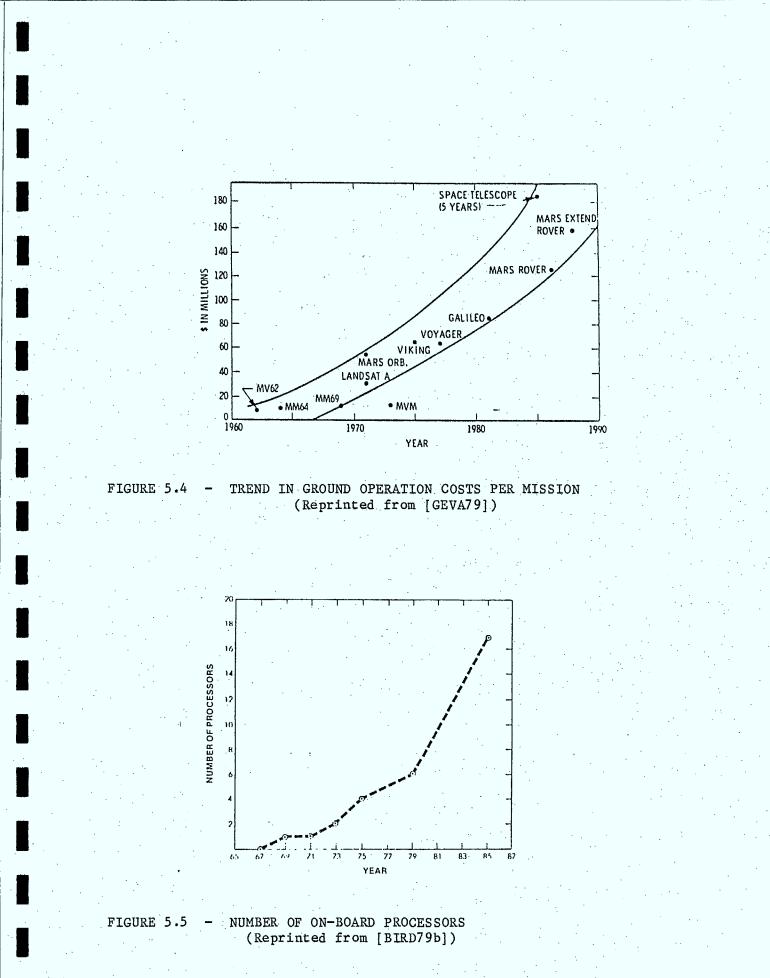

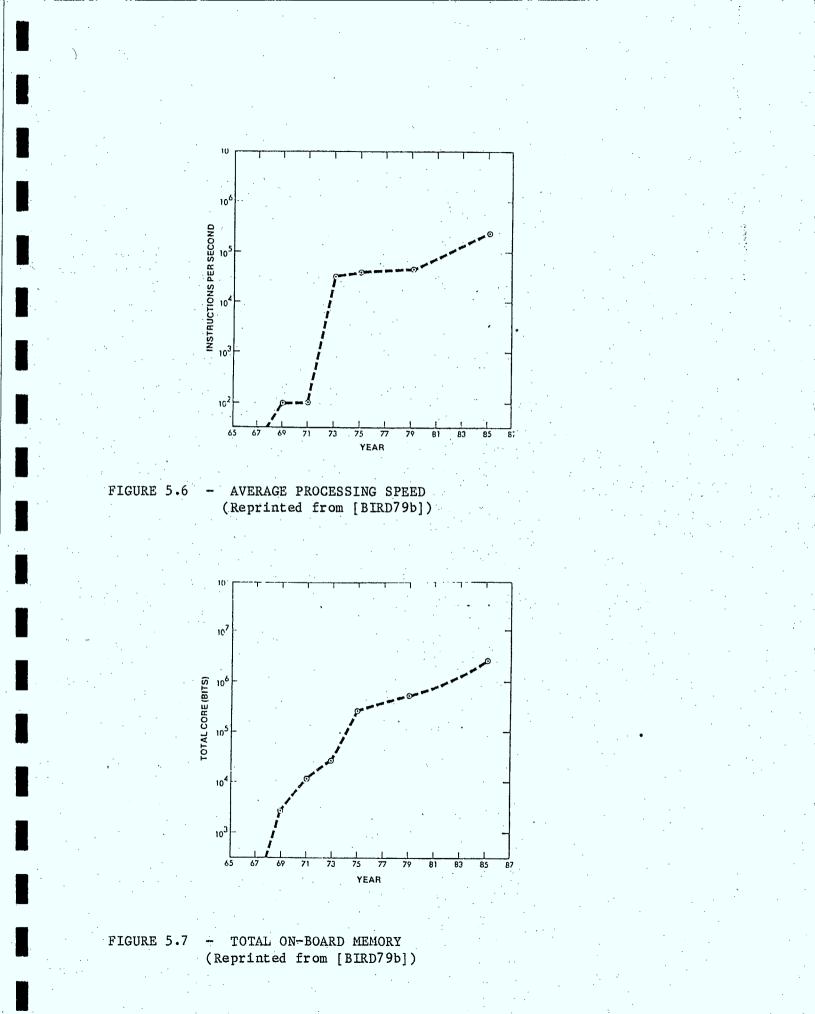

| Configuration                          | 2 CPU's<br>2 Stint's                       | 2 CPU's<br>2 Stint's<br>2 APU's | 2 Sing.<br>String<br>CPU's | 2 Sing.<br>String<br>CPU's | 2 Sing.<br>String       |