lintellitech

P 91 C655 C6661 1982

Queen

The Definition and Specification of an Integrated Set of CAE Tools for Spacecraft Multiprocessor System Design

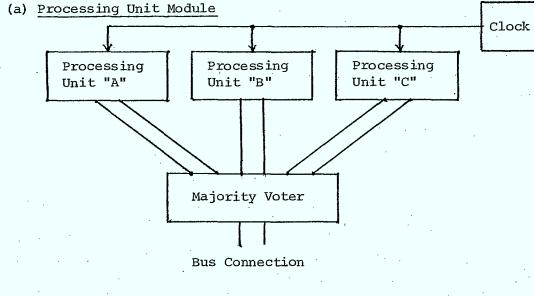

The Definition and Specification of an Integrated Set of CAE Tools for Spacecraft Multiprocessor System Design

> Industry Canada Library Queen JUE 2 0 1998 Industrie Canada Bibliothèque Queen

# Report No. INT-82-16

# March 1982

Approved by:

Dr. S.A. Mahmoud

Dr.S.A. Mahmoud

Authors:

Dr. C. Laferriere Mr. W.T. Brown Mr. J.G. Ouimet

Department of Communications

Gouvemement

du Canada

Government

of Canada

DOC CONTRACTOR REPORT

1:

DOC-CR-SP-82-046

DEPARTMENT OF COMMUNICATIONS - OTTAWA - CANADA

SPACE PROGRAM

TITLE: The Definition And Specification Of An Integrated Set Of CAE Tools For Spacecraft Multiprocessor System Design AUTHOR(S): C. Laferriere

W. Brown

J. Ouimet

S.A. Mahmoud

ISSUED BY CONTRACTOR AS REPORT NO: INT-82-16

PREPARED BY: Intellitech Canada Ltd. 352 MacLaren St. Ottawa, Ontario K2P OM6

DEPARTMENT OF SUPPLY AND SERVICES CONTRACT NO: 3ER.36100-1-0273 SN: 0ER81-03151

DOC-SCIENTIFIC AUTHORITY: R.A. Millar

CLASSIFICATION: Unclassified

This report presents the views of the author(s). Publication of this report does not constitute DOC approval of the reports findings or conclusions. This report is available outside the department by special arrangement.

# Preface

This work was performed for the Department of Communications,<sup>3</sup> Communications Research Centre under DSS Contract No. OER81-03151 , entitled "Computer-Aided Engineering Tools for Spacecraft Multi-Microprocessor Design", from September 15, 1981 to March 31, 1982. This report is one of the following four contract deliverables:

- 1. Executive Summary

- Report #1 Review of Multiprocessor Systems and their Spacecraft Applications.

- 3. Report #2 A Survey of Computer-Aided Engineering (CAE) Tools for the Design and Simulation of Multiprocessor Systems.

- 4. Report #3 The Definition and Specification of an Integrated Set of CAE Tools for Spacecraft Multiprocessor System Design.

# Acknowledgement

The study team gratefully acknowledges the technical guidance of Mr. R.A. Millar of the Communications Research Centre. His knowledge and experience in the field of computer simulation of spacecraft systems have contributed to the quality of the work and provided a constant source of encouragement to the study team.

As well, the study team wishes to thank Mr. J.M. Savoie, also from CRC, for his fruitful discussions and critical reviews.

ii

| Table | of | Contents |

|-------|----|----------|

|       |    |          |

|     |              |                                                          | Page    |

|-----|--------------|----------------------------------------------------------|---------|

|     |              |                                                          |         |

|     | Pref         | ace                                                      | i       |

|     |              | owledgement                                              | 1<br>11 |

|     |              | e of Contents                                            | iii     |

|     |              | of Figures                                               | <br>v   |

|     |              | of Tables                                                | vii     |

|     |              |                                                          |         |

| 1.  | Intr         | oduction                                                 | 1       |

|     |              |                                                          |         |

|     | $1.1 \\ 1.2$ | Scope and Definition of Multiprocessors                  | 5       |

|     | 1.4          | Structure of the Report                                  | . 7     |

| 2.  | Prop         | osed Methodology                                         |         |

| 4.  | LTOD         | osed methodotogy                                         | 9       |

|     | 2.1          | Scope of Existing Tools                                  | 10      |

|     | 2.2          | Toward an Integrated Set of                              | 10      |

|     |              | CAE Design Tools                                         | 13      |

|     | 2.3          | Approaches for Modelling Functional                      |         |

|     |              | Component Description                                    | 14      |

|     |              |                                                          |         |

| 3.  | Spec         | ification/Validation                                     | 21      |

|     | . · .        |                                                          |         |

|     | 3.1          | Introduction                                             | 21      |

|     |              | 3.1.1 Problem Definition                                 | 21      |

|     | •            | 3.1.2 Spacecraft Environment                             | 23      |

|     |              | 3.1.3 Design Philosophy<br>3.1.4 Overview of the Section | 26      |

|     |              | 3.1.4 Overview of the Section                            | 28      |

|     | 3.2          | Specification/Decomposition                              | 29      |

|     |              | 3.2.1 High Level Specification                           | 29      |

| . • |              | 3.2.2 Methods of Decomposition                           | 30      |

|     | . ,          | 3.2.3 Formalizing the Specification/                     |         |

|     |              | Decomposition Process                                    | 34      |

|     |              | 3.2.4 Ada as a Specification Tool                        | 36      |

| , · | , ×          | 3.2.5 A Decomposition Example                            | 44      |

|     | •            | 3.2.5.1 Various decomposition levels                     |         |

|     |              | 3.2.5.2 Observations on the model                        | 62      |

|     |              | 3.2.5.3 System simulation and testing                    | 69      |

|     |              | 3.2.5.4 Computer aided tools and the                     |         |

|     | · · ·        | specification process                                    | 74      |

|     | 3.3          | Validation of Specifications                             | 76      |

|     | 5.5          | 3.3.1 Validation                                         | 76      |

|     |              | 3.3 2 Testing                                            | 80      |

|     |              | 3.3.3 Verification                                       | 83 .    |

|     | :            | 3.3.4 Automated Verification Systems                     | 96      |

| . * |              | 3.3.5 Proposed Validation Capabilities                   | 107     |

|     |              |                                                          | •       |

|     | 3.4          | Summary and Conclusions                                  | 112     |

| 4.  | Perfo     | ormance | and Relia                  | ability       | • • • • • • • | • • • • • •   | • • • • • • • | ••••            | ••    | 115   |

|-----|-----------|---------|----------------------------|---------------|---------------|---------------|---------------|-----------------|-------|-------|

|     | 4.1       | Totood  |                            |               |               | · ·           |               |                 |       | 115   |

|     |           |         | luction                    |               |               |               |               |                 |       | 115   |

|     | 4.2       |         | of CAE To                  |               |               |               |               |                 |       | 116   |

|     |           | 4.2.1   | Architec                   |               |               |               |               |                 | ••    | 117   |

|     |           | 4.2.2   |                            |               |               |               |               |                 |       |       |

|     |           |         | Selection                  | n)            | • • • • • •   | • • • • • •   | • • • • • • • | • • • • • • • • | ••    | 118   |

| •   | 4.3       | Reliab  | ility Mode                 | els           |               |               |               |                 | • •   | 122   |

|     |           | 4.3.1   | Componen                   |               |               |               |               |                 |       | 122   |

|     |           | 4.3.2   | Exhausti                   |               |               |               |               |                 |       | 123   |

|     |           | 4.3.3   | Imperfec                   |               |               |               |               |                 |       | 126   |

|     |           |         |                            |               |               |               | •             |                 |       | 140   |

|     | 4.4       | Resour  | ce Usage 1                 | Aodels.       |               |               |               |                 | • •   | 127   |

| · . |           | 4.4.1   | Simple T                   | otals M       | odel          |               |               |                 | • •   | 128   |

|     |           | 4.4.2   | Effects                    |               |               |               |               |                 |       | 129   |

| •   |           | 4.4.3   | Effects                    |               |               |               |               |                 |       | 131   |

|     |           |         |                            |               |               |               |               |                 |       |       |

|     | 4.5       | Areas   | for New or                 | c Impro       | ved CA        | E Tool        | s             |                 | ••    | 134   |

|     | · .       | 4.5.1   | Architec                   | ture In       | depend        | ent CA        | E Tools       |                 |       | 135   |

|     |           |         | 4.5.1.1                    | Ada Ba        | sed Ge        | neral         | Purpose       |                 |       |       |

|     |           |         |                            |               |               |               |               |                 | · • • | 135   |

|     |           | · .     | 4.5.1.2                    | Exhaus        | tion o        | f Spar        | Ac            |                 | ••    |       |

|     |           |         |                            |               |               |               |               |                 |       | 136   |

|     |           |         | 4.5.1.3                    |               |               |               | Analys        |                 | • •   | 100   |

|     | •         |         | 4.7.1.2                    |               |               |               |               |                 |       | 1.0.0 |

|     |           |         | 1 <b>E</b> 1 1             |               |               |               |               |                 | • •   | 136   |

|     |           |         | 4.5.1.4                    |               |               |               | y Analy       |                 |       |       |

|     |           |         |                            |               |               |               |               |                 | • •   | 136   |

| •   |           |         | 4.5.1.5                    |               |               |               | n Analy       |                 |       |       |

|     |           |         | * <b>.</b> .               | Tool          | • • • • • •   | • • • • • • • | •••••         | • • • • • • • • | • •   | 137   |

|     |           | 4.5.2   | Architec                   | ture De       | nenden        | + CAE         | Toole         |                 | · · · | 138   |

|     |           |         | 4.5.2.1                    |               |               |               |               |                 | • •   | 100   |

|     |           |         | 7 6 J 6 4 6 I              |               |               |               | •             | •               |       | 138   |

|     |           |         |                            |               |               |               |               | ••••            | • •   | 100   |

|     |           |         | 4.5.2.2                    |               |               |               | age Ana       |                 | •     | 1.40. |

|     |           |         | 1 = 0 0                    | 1001          | • • • • • •   | •••••         | • • • • • • • |                 | • •   | 140   |

|     |           |         | 4.5.2.3                    | -             |               |               |               | nalysis         |       |       |

|     |           |         |                            | Tool          |               | • • • • • •   | • • • • • • • |                 | ••    | 141   |

|     |           | _       |                            |               |               |               |               |                 |       |       |

| 5   | 4.6       | Summar  | y                          | • • • • • • • | • • • • • •   |               | • • • • • • • | • • • • • • • • | ••    | 142   |

| 5.  | Tation    |         | and to be Described        |               | 7 -           |               |               |                 |       | 150   |

| э.  |           |         | with Exi                   |               |               |               |               |                 |       | 156   |

|     |           |         | luction                    |               |               |               |               |                 |       | 156   |

| •   | 5.2       |         | tion Betwe                 |               |               |               |               |                 |       | 157   |

|     | 5.3       | Select  | ion of Ex                  | isting        | Tools.        | • • • • • •   |               | • • • • • • • • | • •   | 159   |

| 6.  | S 11 mm - |         | Further W                  | Jonic         | . `           |               |               |                 |       | 166   |

| 0.  |           | -       |                            |               |               |               |               |                 |       |       |

| •   | 6.1       |         | <b>Y</b> • • • • • • • • • |               |               |               |               |                 |       | 166   |

|     | 6.2       | rurthe  | r Work                     | • • • • • • • | • • • • • •   | • • • • • •   | • • • • • • • | • • • • • • • • | .• •  | 171   |

|     |           | •       |                            |               |               |               |               |                 | · ·   | 1 7 0 |

|     | Keiel     | rences. |                            |               |               |               |               |                 | • •   | 173   |

• •

4

iv

# List of Figures

|   |        | · ·     |                                                           | Page |

|---|--------|---------|-----------------------------------------------------------|------|

|   | Figure | 2.1     | Multiprocessor Specifications/Design                      |      |

| • |        | · ·     | Levels and Corresponding CAE Tools                        | 17   |

|   | Figure | 2.2     | Design Phases Using an Integrated                         |      |

|   |        |         | Set of CAE Tools                                          | 18   |

|   | Figure | 2.3     | Functional Decomposition in a<br>Top-down Approach        | 19   |

|   | Figure | 2.4     | Example of a Data Flow Model                              | 20   |

|   | Figure | 3.1     | A Spacecraft Control System                               | 24   |

|   | Figure | 3.2     | Hierarchy of Machines and Programs                        | 26   |

|   | Figure | 3.3     | Machine Equivalence                                       | 27   |

| • | Figure | 3.4     | Tree Structure Resulting from<br>Functional Decomposition | 30   |

|   | Figure | 3.5     | Dataflow Example                                          | 32   |

|   | Figure | 3.6     | Result of the Mixed Approach                              | 33   |

|   | Figure | 3.7     | An Ada Package                                            | 37   |

|   | Figure | 3.8     | An Ada RendezVous                                         | 38 - |

|   | Figure | 3.9     | Basic Structure of a Specification Block                  | 41   |

|   | Figure | 3.10    | Device Servicing in Ada                                   | 43   |

|   | Figure | 3.11    | Description of the Example                                | 44   |

|   | Figure | 3.12    | A First Attempt at Decomposition                          | 46   |

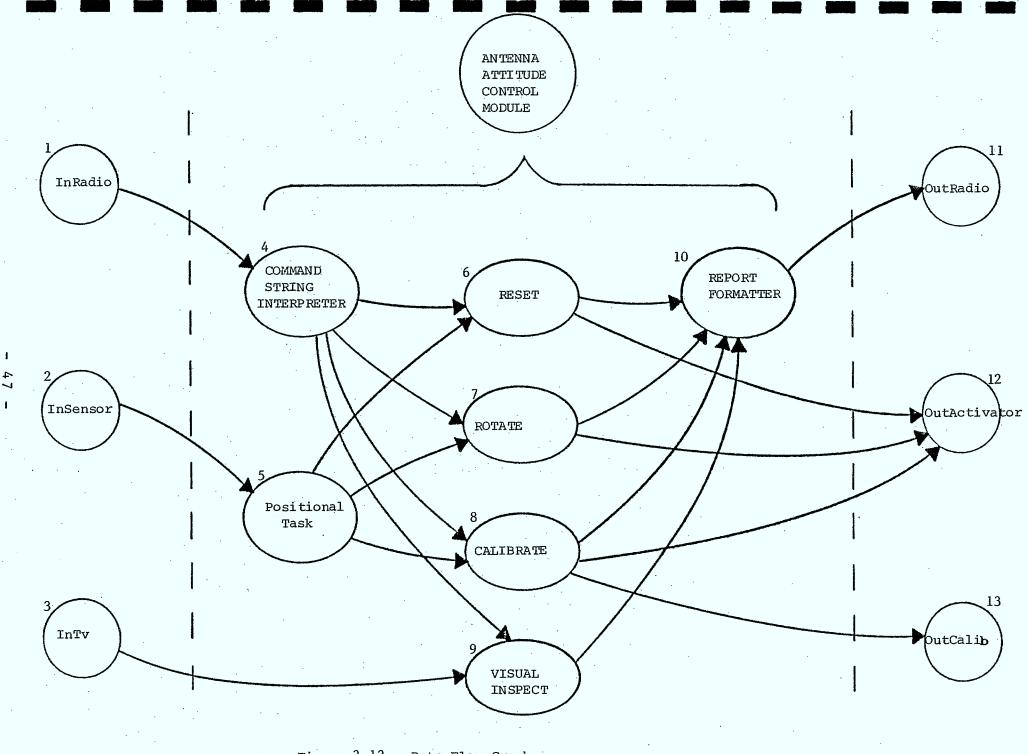

|   | Figure | 3.13    | Data Flow Graph                                           | 47   |

|   | Figure | 3.14    | Definition of Various Commands                            | 48   |

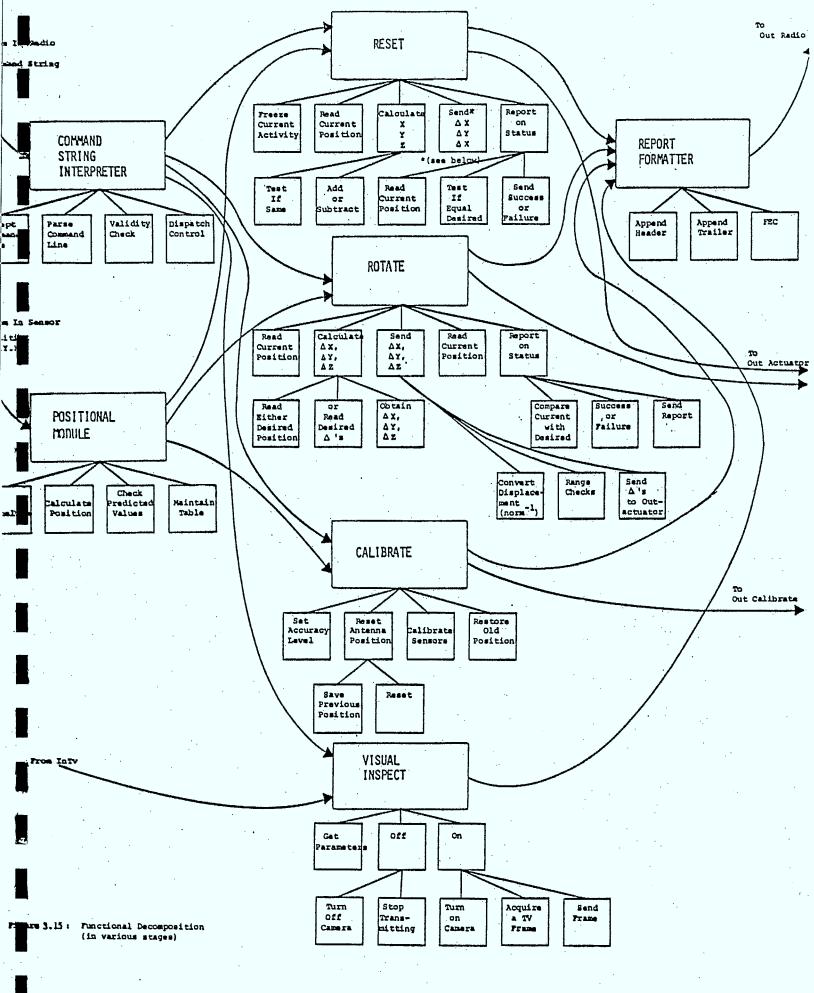

|   | Figure | 3.15    | Functional Decomposition<br>(at various stages)           | 52   |

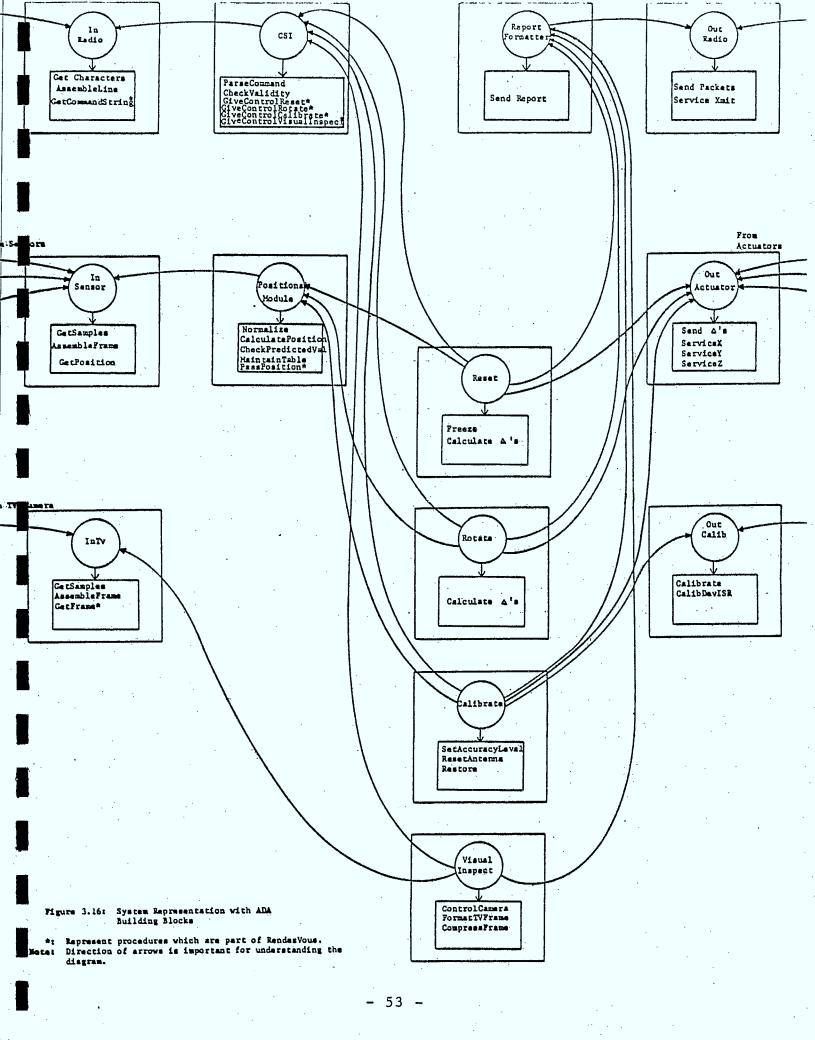

|   | Figure | 3 16    | System Representation with Ada                            | . 94 |

|   | riguie | J.I.U . | Building Blocks                                           | 53   |

|   | Figure | 3.17    | Ada RendezVous and Passing of Control                     | 56   |

|   | Figure | 3.18    | CommandStringInterpreter                                  | 59   |

|   | Figure | 3.19    | Expansion of a Separate Procedure                         | 60   |

|   | Figure | 3.20    | Description of the Reset Module                           | 61   |

|   | Figure | 3.21    | Procedure Call Arrangements in Ada                        | 64   |

| , | Figure | 3.22    | Representation of an Input Module                         | .67  |

|   | Figure | 3.23    | System Model and TestBed                                  | 69   |

|   | Figure | 3.24    | Device Simulation Module                                  | 70   |

- v -

|          |        | , * · · · · · |                                                    |     |

|----------|--------|---------------|----------------------------------------------------|-----|

| •        | Figure | 3.25          | Simulation and Testing Package                     | 71  |

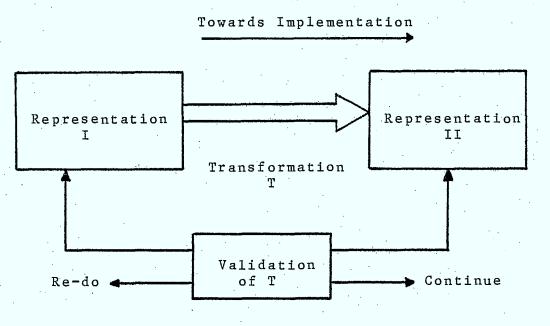

|          | Figure | 3.26          | Example of Transformation                          | 76  |

|          | Figure | 3.27          | Validation of the Design Process                   | 77  |

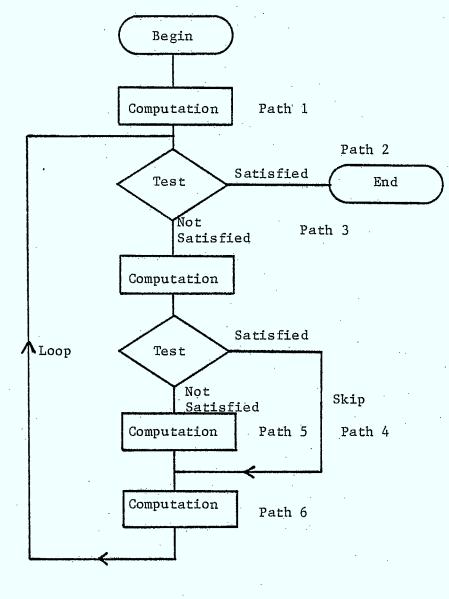

|          | Figure | 3.28          | Skeleton of a Program Control Structure            | 81  |

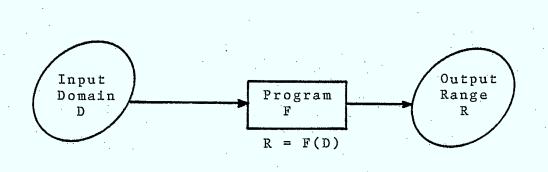

|          | Figure | 3.29          | A Program's Domain and Range                       | 81  |

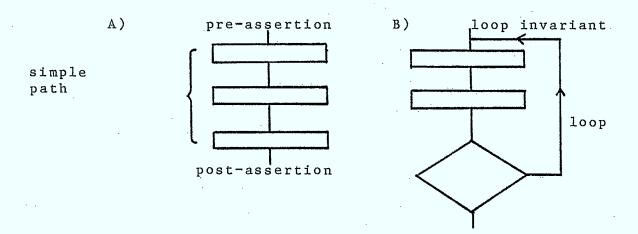

|          | Figure | 3.30          | Paths and Assertions                               | 85  |

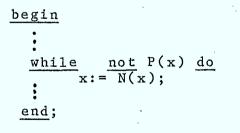

| <b>.</b> | Figure | 3.31          | Simple Loop Example                                | 88  |

| -        | Figure | 3.32          | Subprogram for Simple Division                     | 91  |

|          | Figure | 3.33          | Subprogram with Assertions                         | 91  |

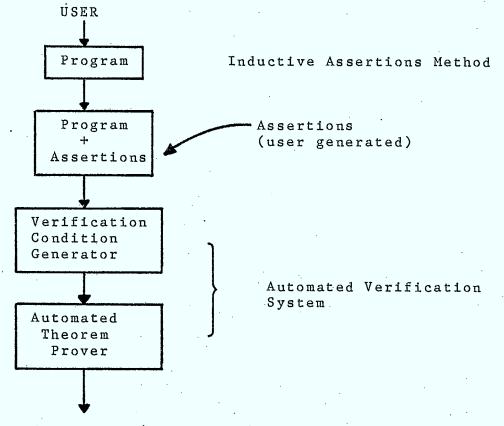

|          | Figure | 3.34          | Design and Verification of Programs                | 97  |

| L        | Figure | 3.35          | Procedure InsertSorted                             | 99  |

|          | Figure | 3.36          | Verification Condition 15                          | 102 |

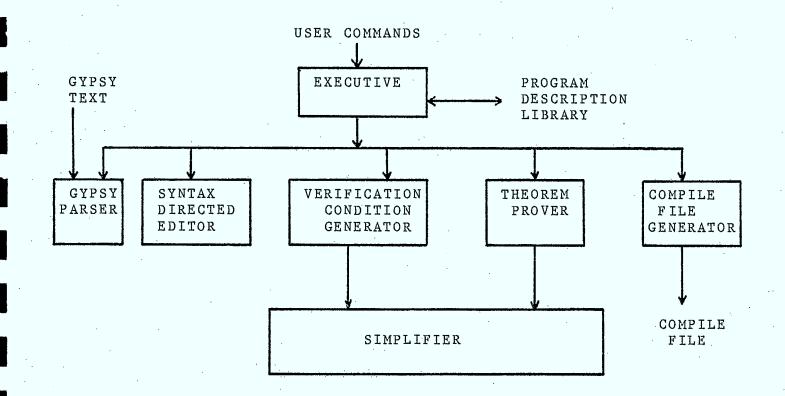

|          | Figure | 3.37          | Gypsy Verification Environment                     | 104 |

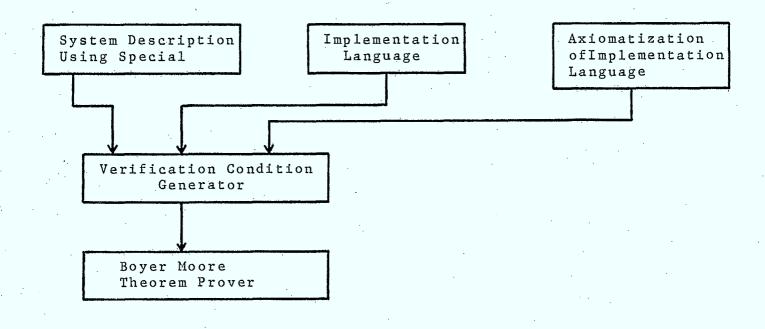

|          | Figure | 3.38          | Description of the HDM System                      | 105 |

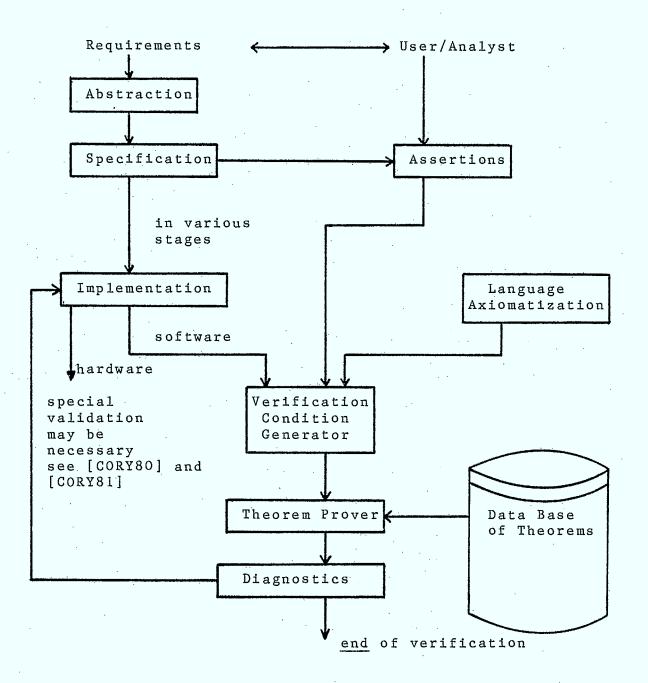

|          | Figure | 3.39          | An Ideal System                                    | 107 |

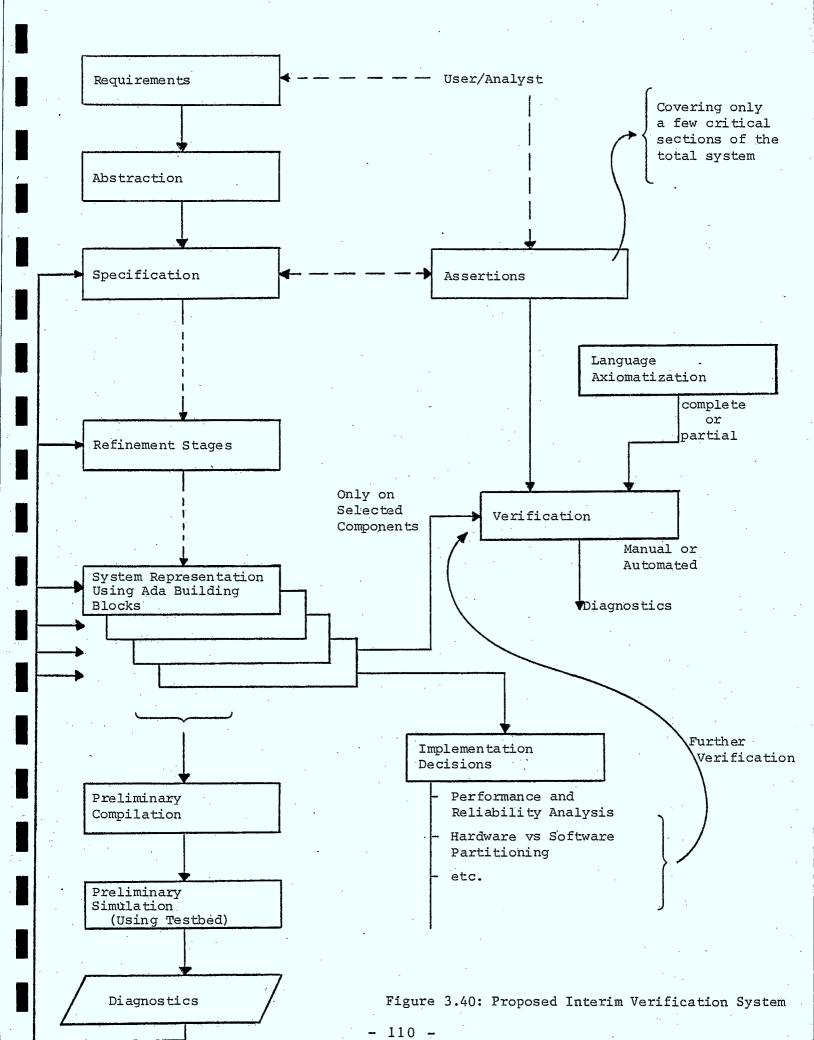

|          | Figure | 3.40          | Proposed Interim Verification System               | 110 |

|          |        |               |                                                    |     |

| • •      | Figure | 4.1           | Performance/Reliability Design<br>Methodology      | 145 |

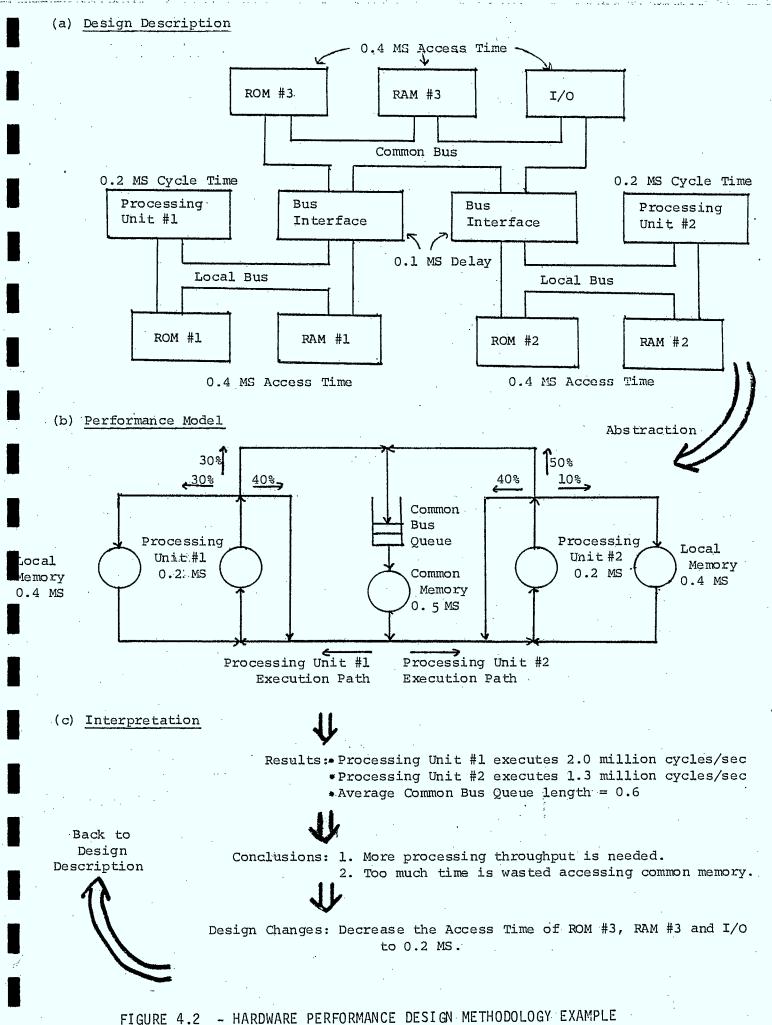

| -        | Figure | 4.2           | Hardware Performance Design<br>Methodology Example | 146 |

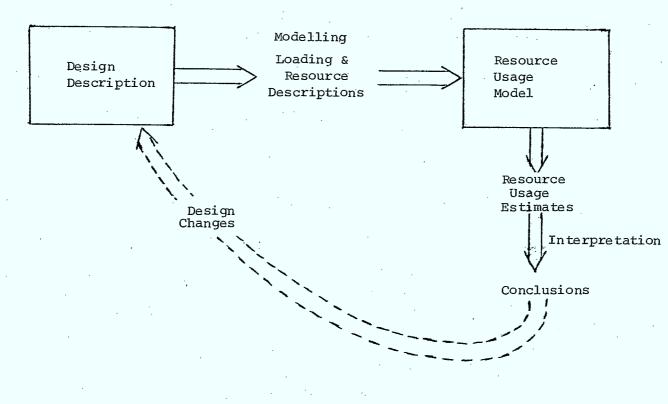

|          | Figure | 4.3           | Resource Usage Design Methodology                  | 147 |

|          | Figure | 4.4           | Example Simple Totals Model                        | 148 |

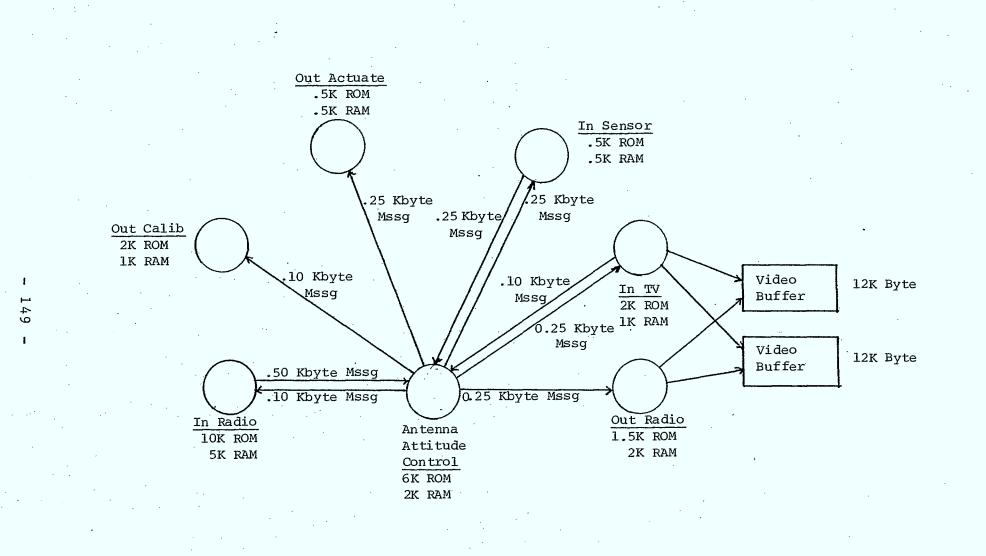

|          | Figure | 4.5           | Example Access Graph                               | 149 |

|          | Figure | 4.6a          | Example Effects of Loading Model                   | 150 |

| •        | Figure | 4.6b          | Example Effects of Loading Model                   | 151 |

|          | Figure | 4.6c          | Example Effects of Allocation Model                | 152 |

|          | Figure | 4.7a          | Hardware Reliability Analysis<br>Tool Example      | 153 |

|          | Figure | 4.7b          | Hardware Reliability Analysis<br>Tool Example      | 154 |

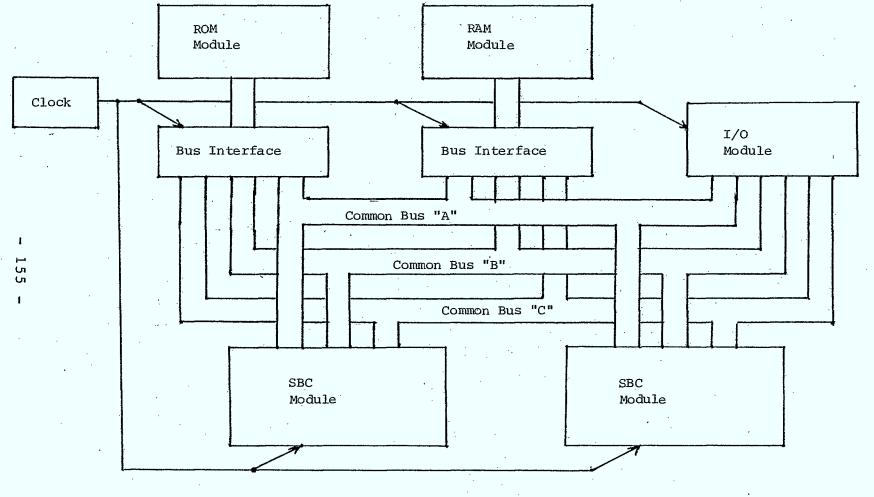

|          | Figure | 4.7c          | Hardware Reliability Analysis<br>Tool Example      | 155 |

|          | ·      |               |                                                    |     |

- vi -

.

# List of Tables

|           |                                                  | Page |

|-----------|--------------------------------------------------|------|

| Table 5.1 | Existing Tool Functional Characteristics         | 163  |

| Table 5.2 | Existing Tools Implementation<br>Characteristics | 164  |

| Table 5.3 | Existing Tools Selection Evaluation              | 165  |

- vii -

Interest in multiprocessor and distributed intelligence computer systems have increased dramatically in recent years. This interest has been fostered by the availability of micro-processors with ever increasing performance-price ratios and the expected emergence of monolithic systems with still higher capabilities in the near future.

Advances in LSI and VLSI semi-conductor technology have significantly reduced computer hardware weight, power consumption and cost. It is now feasible and practical to employ multi-processor systems on spacecraft in order to increase the reliability, extend mission duration and satisfy increasingly more computational demand during the mission.

The development of multiprocessor and distributed intelligence computer systems and their utilization in various applications have been impeded by the lack of an appropriate theoretical base. The control of systems containing large number processors is not well of While considerable work has been done recently understood. to develop a theoretical base, it seems unlikely that this work will have significant impact on practical system design in the near future. As a result, multiprocessor system designers have turned to the use of CAE tools for the

the development of such systems. Such CAE tools are used, in general, to support the skill level of the designer, provide insight into the attributes of alternative architectures, allow evaluation of these architectures and support the development, simulation and testing of actual multiprocessor systems.

More specifically, computer-aided engineering tools are required to simulate alternate hardware configurations, evaluate the software implications on selecting a particular hardware configuration, perform required hardware-software tradeoffs, establish that the specified hardware and software are compatible and that overall system performance requirements are met. All of these must be done at an early stage in the design process, before the software is coded and the hardware is constructed.

In the absence of such computer-aided engineering tools, it is difficult for the designer to assess and evaluate system performance adequately before constructing a breadboard prototype, developing its software, and testing the resulting system. At this late stage in the design process, discovered inadequacies and inconsistencies are expensive and time-consuming to correct and often require significant redesign. With the appropriate CAE tools, the chances of this happening at such a late stage in the design process are minimized.

- 2 -

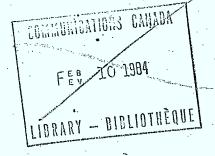

In an accompanying report [MAHM82], a survey which examined existing CAE tools for multi-processor design has been presented. The survey identified six specification and design phases for the purpose of identifying the utility and applications of the various available tools. These phases are:

- 1. The Requirements Specification phase,

- 2. The Functional Components Definition phase,

- 3. The Architectural Design phase,

- 4. The System Model phase,

- 5. The Processing Element Partitioning

- (Register Transfer Level) phase, and

- 6. The Logic Design (hardware) phase.

The survey indicated the availability of many design simulation tools which satisfy different design needs, depending on the design level (or levels) for which it is developed. Unfortunately, no one simulator was found to be useful throughout all specification and design phases. This multiple simulator approach outlined in the survey has two advantages and several disadvantages. The advantages are:

- 1. Each simulation can be written in a language tuned for one particular level, and

- 2. Each simulation tool can optimize its runtime organization for one particular task.

- 3

The disadvantages include the following:

- The design effort is multiplied by the necessity of learning several simulator systems and writing a design in each.

- The possibility of error is increased as more human manipulation is involved.

- 3. As the design becomes increasingly fragmented, it becomes impossible to simulate an entire multiprocessor system at a low level of abstraction. Therefore, only small fragments can be simulated at any one time.

- 4. Each fragment needs to be driven by a supply of realistic data and its output must be interpreted. This may make the software written to serve these needs extremely costly.

Several tools have been developed to overcome the above difficulties and provide the designer with a uniform simulation approach starting at the architecture design level and going down to the register transfer simulation level. The utility of these tools can be improved substantially by augmenting them with a high level specification package which allows the designer to describe the functional components of the system being designed and to interface this high level description to existing tools at the architectural level. In addition, two design aspects must be addressed in augmenting existing tools:

- Redundancy and fault-tolerance characteristics analysis must be provided at the architectural levels if the tools are to be useful in the design of spacecraft (or avionics) multiprocessor systems.

- 2. The high level specification language must contain mechanisms for system verification. As the design process continues, these mechanisms will evolve naturally towards validation and verification of the software.

The study reported here is concerned with the issue of augmenting existing tools to generate an integrated set of multiprocessor design and simulation tools that can be useful throughout the various phases of the design.

#### Scope and Definition of Multiprocessors

1.1

The proliferation of various publications dealing with interconnecting microprocessors to form unified systems has given rise to some ambiguity with respect to the definition of "multiprocessor systems" and "distributed microprocessor systems". To avoid such ambiguity, we introduce a definition

-- 5 -

for the term "multiprocessors" which will be used throughout this report. We also define the "scope of configurations" of such systems considered to be relevant for spacecraft applications.

For the purpose of this report, we define a multiprocessor system to be [JENS78]:

"a multiplicity of microprocessors that are physically and logically interconnected to form a single system in which overall executive control is exercised through the cooperation of decentralized system elements".

Moreover, we define the scope of multiprocessor systems considered in this study through the following general characteristics:

- 1. The microprocessors forming the system, as well as all other system elements co-exist in the same locality (i.e., no telecommunication lines are used since the elements are not geographically separated).

- The microprocessors and other system elements are interconnected according to one of alternative structures (uni or multi-bus, a loop or ring connection, a matrix switch, etc.).

2.

~ 6 ·

- 3. Conceptually, a single executive manages all of the system's physical and logical resources in an integrated fashion. The kernel (control) logic and data structures are replicated among a number of processors or memories.

- The number of processors to be interconnected is relatively small (e.g., under 30 processors).

- 5. Redundancy in the hardware is assumed through the use of identical spares, which along with other fault recovery mechanisms constitute what is known as "fault-tolerant" architectures.

## 1.2 Structure of the Report

The basic methodology adopted for generating an integrated set of CAE tools for multiprocessor systems is explained in Section 2. It is shown that the underlying concept is based on a top-down design approach starting from a high level specification phase.

Section 3 of this report introduces the basic definitions and specifications of a high level design tool constructed using ADA as the basic programming language. An example is provided to illustrate the basic functional

· **-** 7

decomposition process. The example is based on a hypothetical application of a multiprocessor system as a controller for a set of sensors and actuators in a spacecraft.

Section 4 examines the performance evaluation aspects associated with designing multiprocessor systems for spacecraft applications. Two performance criteria are considered: resource utilization and reliability (redundancy and recovery from failures). The use of CAE tools to assist in evaluating both criteria is examined.

Section 5 investigates the interfaces needed to integrate existing CAE design tools at the architectural and system model levels with the high level functional specification tool described in Section 3. Finally, Section 6 presents a summary of the contents of this report and a set of recommendations for future work aimed at assimilating an integrated set of CAE design tools for multi/microprocessors.

### 2.0 Proposed Methodology

As explained previously, current design practice of multiprocessors consists of a series of steps which starts by stating the general requirements and terminates by detailed hardware and software design, development and testing. A broad spectrum of tools exists to assist the designer at each step.

Our survey of existing tools [MAHM81] indicated that while several design and simulation tools exist to satisfy different needs, no one simulator is useful throughout all the specification and design phases. In addition, a gap exists at the high levels of the design which makes it difficult to use the output of the tools at the functional components specification level to generate the input to the architecture selection stage. This gap will be explained before introducing the proposed methodology.

In this section, we review briefly the design phases and the general features of the tools used in each phase. We use the review to highlight certain deficiencies which exist in the spectrum of available tools. The review is followed by an explanation of the concepts underlying the methodology proposed in this report.

In a general sense, it will be shown that the proposed methodology is aimed at closing the gap which exists between the functional component specification phase and the

- 9 -

architecture design phase, and at the same time augmenting existing tools with mechanisms to evaluate the performance and the reliability of the system at various design stages. This will ultimately result in an integrated set of CAE tools which can be utilized in a consistent fashion throughout the various design levels.

## Scope of Existing Tools

2.1

Figure 2.1 illustrates the specifications and design levels of multiprocessor systems (see survey report [MAHM82], also referenced in the preface of this report). Existing tools can be classified according to the design level (or levels) at which the tool is utilized.

At the requirement specification level, tools are used to define the demands placed upon the system in a complete, consistent and unambiguous set of statements. The output of the tools is usually given in a machine readable format. The input can be generated by several authors and the tool is expected to merge the input from these authors while removing all redundancies. The output document is used by all design team members as a reference for the requirements of the

system.

Design occurs after the requirements phase has been completed. The first level of the design process consists of an orderly definition of the main functional components of

- 10 -

the system which satisfy the requirements. This is followed by further decomposition of the main functional components into smaller subfunctions, and the process continues until a system architecture emerges in which a hardware-software model can be abstracted and the sub-functions can be mapped into elements in the model.

Several tools are currently available for automating the process of defining the functional components of the system and for decomposing these components into smaller, less complex components. The utility of these tools in the design of multiprocessors is limited by the following factors:

- 1. the tools lack the ability to describe the dynamic interaction between the decomposed functional components. Thus aspects such as concurrency, synchronization, etc., cannot be formally described.

- 2. behaviour of the system cannot be The described formally using existing tools at functional components level. the The designer is forced to extract this behaviour manually before deciding on a suitable architecture. This informal extraction is bound to generate errors and inconsistencies.

3. The output of existing tools is not interfaceable directly to architecture

- 11 -

level procedural simulation languages with their formal syntax. This creates a gap in the transition to the next lower design level, i.e., the architecture selection level.

4. Subfunctions and other resources (e.g., data structures) that are shared by the main functions, as well as their access control structures, cannot be described easily by existing tools, particularly in the dynamic interaction environment of spacecraft multi/microprocessors.

The above difficulties motivate the development of a tool at the functional component definition level which can be mutually integrated with the tools used at the architecture selection level.

A large number of simulation tools exist at the architecture selection level and the levels below it. These tools can be substantially enhanced with two additional features:

1. The incorporation of formal rules to

verify the modelled behaviour of each module and of the entire system.

The incorporation of reliability analysis tools to model and simulate the faulttolerance characteristics of the system.

- 12

The development of a formal specification and verification tool at the functional component description level, together with the enhancement of existing tools to handle the analysis of reliability requirements can be viewed as the catalyst of the proposed methodology.

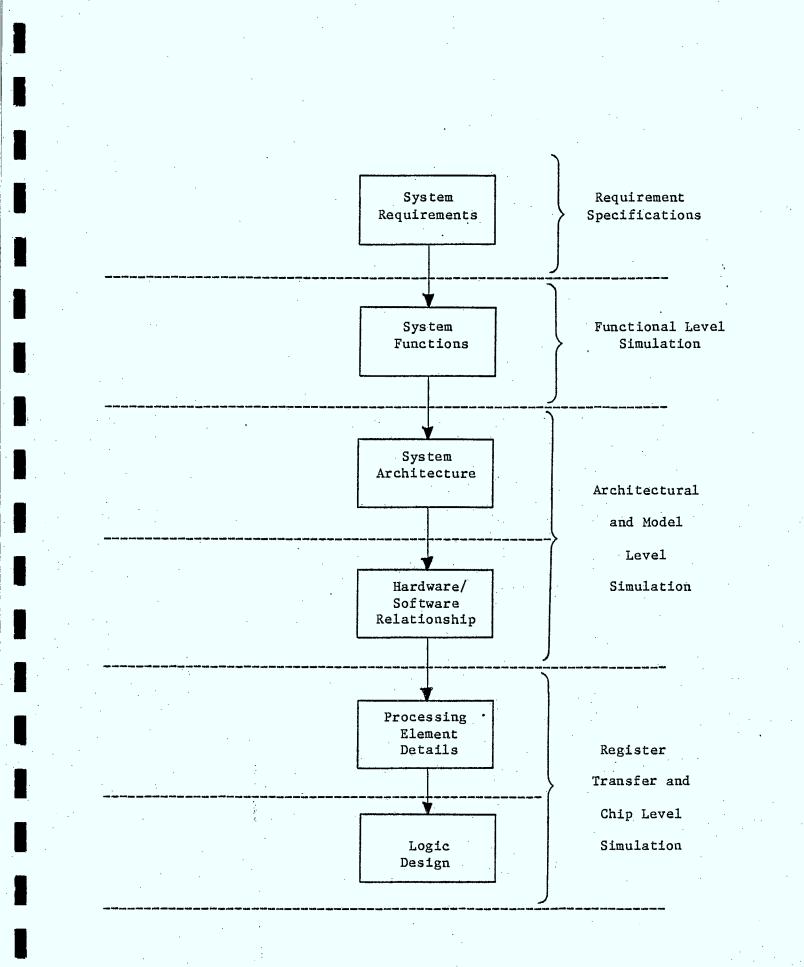

#### 2.2 Toward an Integrated Set of CAE Design Tools

The discussion of Section 2.1 indicated that a "missing link" exists at present in the set of currently available CAE design tools for multiprocessors. This "missing link" is at the functional component description level (see Figure 2.1). A tool is needed at this level which will be utilized in the design level between the requirements specification level, and the system architecture level. The newly developed tool can be interfaced with existing tools for the requirements specification and with tools currently used in the simulation of system architecture.

Figure 2.2 depicts the role of the proposed Functional Component Specification tool in the multi-phase design approach. The tool is utilized to translate system requirements specification into functional components described using a high level behavioural description language. As well, preliminary system architectures can be selected and evaluated using this tool. The output of this phase will serve as input to the next phase; namely, the detailed architecture phase, for which excellent design tools exist at

present.

- 13 -

The main concepts underlying the high level functional description tools are introduced in Section 2.3 with the full details presented in Section 3. The evaluation tools for resource utilization performance models and reliability characteristics models are discussed in Section 4.

#### Approaches for Modelling Functional Component Description

The development of a high level specification tool to simulate the functional components is based on a modelling approach which captures the behaviour of its component, its relationship to other components and the interconnection of the components to form the entire system. Two alternative approaches are generally employed for this purpose:

1. A top-down decomposition approach,

2. A data flow model approach.

2.3

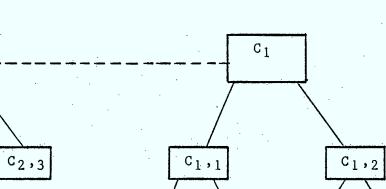

The general concept underlying the top-down approach can be summarized as follows (see Figure 2.3):

> each of the main functional components of the system, defined in the requirements specification phase, is described in terms of its external interfaces and the basic functions it performs.

each component can then be treated separately and divided into subcomponents. Collectively, these subcomponents must maintain the same external interfaces of

- 14 -

the parent component. Again, each subcomponent is desribed in terms of its external interfaces.

the process of decomposition can be applied iteratively to the subcomponents until they are refined into the simplest possible (elementary) components.

a validity check is applied at each decomposition step to ensure the completeness and consistency of the decomposition.

The top-down design approach is suitable for the design of complex systems since it systematically reduces the design process to simpler components which can be tackled separately. Its main drawback in the multiprocessor area lies in its inability to capture the relationship between the various data structures at different decomposition levels. This is because many data structures are difficult to decompose in a hierarchical order.

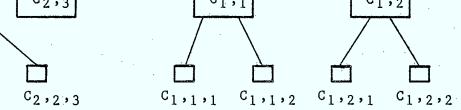

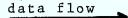

The data flow model approach represents the system as a set of computational modules, sequentially processing a flow of data. The modules form a network with data merging and branching out. The source of data is a set of input modules and the terminal is a set of output modules. An example of data flow model is depicted in Figure 2.4. This model bears

- 15 -

some relation to many of the features of the spacecraft processing environment in that the latter consists of input sources (sensors), output terminals (actuators) and a set of data processing modules (algorithms). In general, data flow models are not convenient to use in describing and designing complex systems.

The development of a high level functional component description tool (Section 3) is based on a hybrid approach in which the data flow model is used initially to describe the behaviour of the system. Each computational module in the data flow model is regarded as a system component which is then decomposed in a top-down approach. This hybrid approach will be shown to combine the advantages of the data flow model and the top-down decomposition approach.

- 16 -

Figure 2.1 Multiprocessor Specifications/Design Levels and Corresponding CAE Tools

- 18 -

· · · · ·

c<sub>2</sub>

C<sub>2</sub>,2

C<sub>2</sub>,<sub>2</sub>,<sub>1</sub> C<sub>2</sub>,<sub>2</sub>,<sub>2</sub>

C<sub>2</sub>,<sub>1</sub>

- 19 -

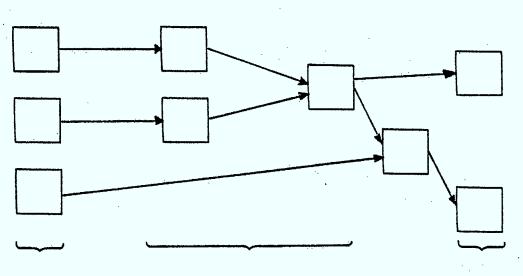

# Input Modules Computational Modules

Figure 2.4 Example of a Data Flow Model

20 -

Output Modules

# SPECIFICATION/VALIDATION

#### 3.1 INTRODUCTION

3.

## 3.1.1 Problem Definition

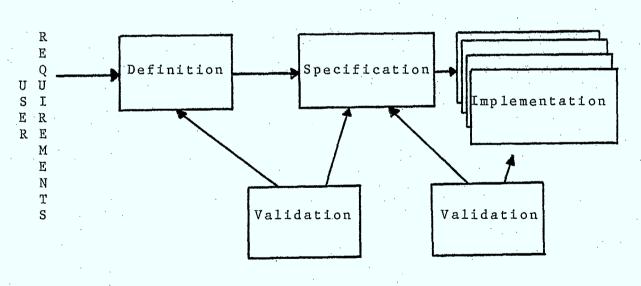

Traditionally, computing systems have been designed by a team of individuals. The design process was initiated with an effort to determine the requirements of the system to be built. The term "requirement" takes on different interpretation depending on the background of a given individual in the design team. Hardware and software induced misunderstandings abound in that early design Nonetheless, what emerges is a list of items phase. (often conflicting) depicting in detail what the system should do, how fast and how often it should do it and how reliable its performance should be.

The next phase is a mapping of the requirements, usually stated in a very informal fashion, to formal and complete specifications. This mapping is not trivial and, once done, may require validation; in other words, going back and checking that the formally specified system meets the requirements.

What follows is a series of decomposition or refinement steps on the original specifications which are normally at a very high level. Keeping in

- 21 -

specification should lead to mind that implementation, the high level specifications have to be translated into more manageable, lower level specifications. In this manner, a transition into a complete software description of the intended behaviour of the system is accomplished. At this point, validation may also be needed.

With the behaviour of the system formally described, a partitioning of some functions into hardware/software or dedicated hardwired controller can be attempted. The necessary guidelines to assist in this process are obtained through performance analysis and simulation.

A design methodology encompasses all the stages that have been described, namely: requirements, specification, refinement/decomposition, implementation, and performance analysis. This section is devoted to describing the high level specification activities and the ensuing series of refinement steps. The output of this process will be a formal description of the system's behaviour in a high level language; this description will also be in a form suitable for further processing by other levels.

22 .-

# 3.1.2 Spacecraft Environment

A design methodology catering to general purpose environments would be very difficult to specify precisely. This is due to the multifarious nature of the tradeoffs involved in system design. Fortunately, working within a spacecraft environment allows for some assumptions to be made so as to restrict the scope of the methodology. The simplication thus achieved should significantly reduce the complexity of the methodology, and in particular of the specification/decomposition process.

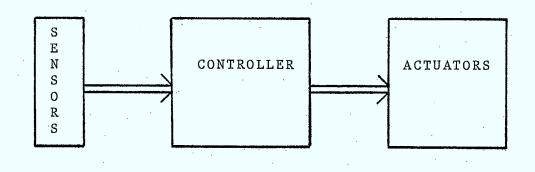

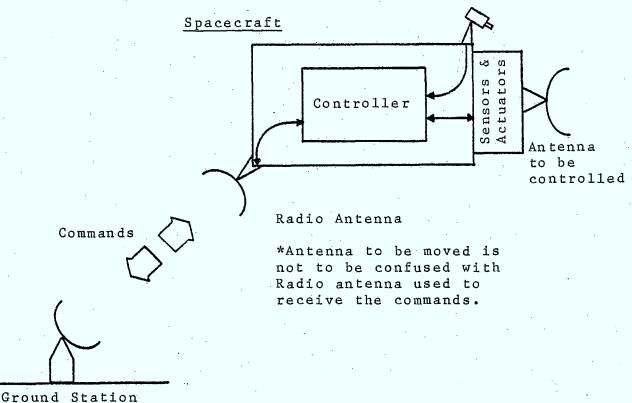

A computer system aboard a spacecraft is, by definition, a dedicated controller. It overseas most of the current activities and may also be called upon to perform complicated computations. A basic representation of such a system is shown in Figure 3.1 where the input/output characterization of a spacecraft is illustrated. The controller has the capabilities to perceive the outside world through its sensors and to influence and to act

- 23 -

Figure 3.1: A Spacecraft Control System

upon the physical environment through the actuators. The attitude of an antenna, for example, can be sampled by some sensors and the controller (or computer system) can be made aware of it. Based upon stored directives or upon remote commands, the controller may decide to change the orientation of the antenna. The Actuators, (or servomotors) would then be used to effect this change on the physical environment.

There is yet another aspect to be considered: the real time nature of these actions. It may be required, for the sake of accuracy perhaps, that the sampling of the position of the antenna be done every milisecond. Similar constraints may also exist on how often and how fast the antenna can be moved. These observations lead to the conclusion that most tasks performed by onboard computer are periodic. The literature on such systems would seem to substantiate this view.

- 24 -

The set of requirements for onboard an controller would reflect the flow of data and its The sensors would be characterized by an rate. output data type, and other information such as average data rate and peak data rate. Similarly for the actuators, requirements concerning the input data type, the maximum permissible data rate, the minimum data rate, etc., would be given. The control tasks to be performed by the computer can be described by a transformation of various input types some output types, according to into some These functions would also have time algorithm. constraints imposed on them to determine their These input, output, and execution speed. processing constraints are easily expressed in a

data flow framework.

- 25 -

# 3.1.3 Design Philosophy

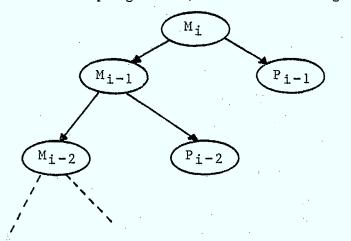

As indicated before, the design process is a translation of informal requirements into formal specifications, followed by gradual refinement steps on these specifications. This stepwise refinement approach is analogous to a hierarchical system of machines and programs (as shown in Figure 3.2).

Figure 3.2: Hierarchy of machines and programs

In Figure 3.2,  $M_i$  is the highest machine. It would correspond to a machine which would perform all the system functions in one high level program instruction. Such a program,  $P_i$ , is a trivial program and is not shown. When considering the problem of designing a complex system, it may be advantageous to decompose the original design of  $M_i$ into the design of  $M_{i-1}$  and  $P_{i-1}$ . The machine  $M_{i-1}$ supports the computations performed by  $P_{i-1}$  and is the computational structure of the system to be the computational structure of the system to be designed. The Program  $P_{i-1}$  is the computational behaviour of the system. The fact that  $M_{i-1}$  does not exist is of no concern; it can always be created by further decomposing  $M_{i-1}$  into  $M_{i-2}$  and  $P_{i-2}$ .

The methodology presented here, first assumes the existence of  $M_{i}$ . It decomposes  $M_{i}$  into  $M_{i-1}$  and  $P_{i-1}$ . Subsequently,  $P_{i-1}$  is specified using a high level language and leaving out lower level details. At that stage, machine  $M_{i-1}$  is assumed to exist. To proceed further,  $M_{i-1}$  is decomposed into  $M_{i-2}$  and  $P_{i-2}$ . Since all the instructions of  $P_{i-1}$  were directly executable by  $M_{i-1}$  (i.e., were written in  $M_{i-1}$ 's native language), it is easy to see that  $P_{i-2}$ is, in fact, a stepwise refinement on certain sections of  $P_{i-1}$ . At that level, the combination of  $P_{i-1}$  and  $P_{i-2}$  executing on  $M_{i-2}$  still corresponds to  $M_{i}$ , (as shown in Figure 3.3).

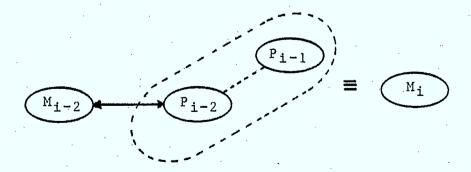

#### Figure 3.3: Machine equivalence

- 27 -

The methodology calls for this process to be applied iteratively so that a hierarchy of programs and machines is created.

The question of when to stop and implement physically a given machine (or parts of a machine) is not answered by this level of the methodology. The goal of the Specification/Decomposition process is to specify and refine down to a level where other tools such as performance evaluators can be applied. The results of such tools should help answer the implementation questions.

## 3.1.4 <u>Overview of the Section</u>

This section comprises main two parts: specification/decomposition and validation. In the first part, the concept of creating a hierarchy of programs is covered in details and an example of specification and decomposition is introduced. The second part addresses the problem of validation which was briefly mentioned in the introduction. A survey of validation techniques and of automated verification tools constitutes most of the subsection.

A summary of the section, together with concluding remarks will also be found at the end of the section.

#### 3.2 Specification/Decomposition

#### 3.2.1 <u>High Level Specification</u>

The first step of the methodology involves a translation of the requirements into very high level specifications. The nature of this translation process is not easy to document since it is mostly accomplished by systems analysts (i.e., humans) and relies on their intellectual capabilities. Human intervention in the translation process may introduce errors in this first attempt at specification. Substantial research activity has been generated, notably, [RAMA81] in which a dual team, design dual specification approach is advocated. The superiority of their technique has to be firmly established. Requirements vet definition has also been studied in [ROSS77a], and [ROSS77b] in which a structured analysis approach was proposed.

As mentioned earlier, the first specification attempt, as well as all others, embodies the hierarchical concept of machines and programs. It is important to realize that a machine program representation is isomorphic to a representation involving structure and behaviour. The latter type of representation has been used extensively in assisting hardware design endeavours [HILL79].

29 -

#### 3.2.2 <u>Methods of Decomposition</u>

Stepwise decomposition is the series of activities that will transform the high level specification into an acceptable implementation. Although there are several methods to do this, only two of the most popular techniques will be described. (Also see [BERG81]).

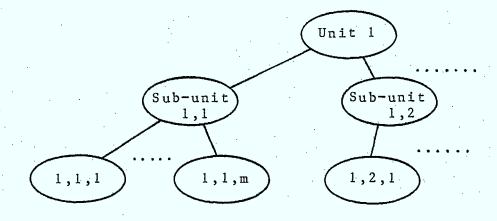

# 1. Functional decomposition

functional decomposition The technique of involves a divide and refine approach. The problem is first considered as a whole and then divided into more manageable sub-problems. Those sub-problems can, in turn, be decomposed using the same technique. The result is a tree-like structure as shown in Figure 3.4.

Figure 3.4: Tree structure resulting from Functional Decomposition Functional decomposition, (as described in [DIJK76] and others), has been in use for a long time, and lends itself well to hierarchical development of the The approach is not without type proposed herein. difficulties however. One of the major problems associated with its use is the lack of similarity among independent decompositions of the same problem. Functional decomposition requires а concept (e.g., time, dataflow, groups of functions) with respect to which decomposition will be done. Lack of uniformity in choosing this concept causes the discrepancies previously mentioned.

2. Data Flow decomposition

An alternative to functional decomposition is data flow analysis. The problem to be solved is reduced to a flow problem in which afferent\* modules collect various data and transmit these data to a network of computing modules. Those modules transform and alter the data and in so doing also change the flow. The end result, still in a flow form, is then given to the efferent modules for interfacing with the application. This method is described in Figure 3.5.

In data flow terminology, afferent and efferent modules are meant to be input and output modules leading into or away from a network of computing elements.

- 31 -

Afferent Efferent Modules Network of Computational Modules Modules

Figure 3.5: Data flow example

The data flow technique is well documented in [YOUR75]. It lends itself very well to the dynamic flow of data model of a spacecraft. It is, however, unwieldy to use at times, since some problems are not amenable to this functional decomposition with respect to data flow.

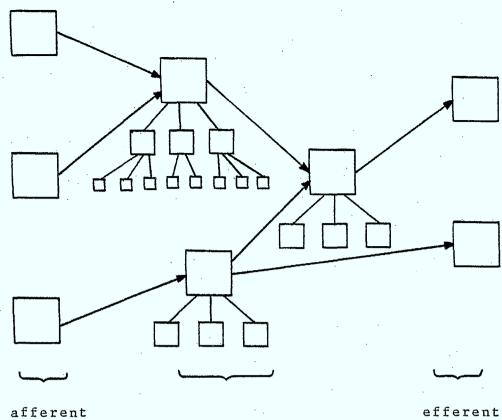

3. A mixed approach

In view of the affinity of the data flow analysis with the spacecraft design problem, this method was adopted, at least in the first few attempts at decomposition. To remedy some of the data flow analysis shortcomings, a functional decomposition method will also be used after the initial data flow decomposition. Figure 3.6 shows a hypothetical system decomposition carried out along those lines.

32 -

modules

efferent modules

network of computing modules subjected to further functional decomposition

Figure 3.6: Result of the mixed approach

It is expected that this mixed approach will be able to capture the inherent data flow aspect of the role of an on-board controller and to help in creating the hierarchy of machines and programs which is essential to the general methodology. The mixed approach to decomposition will be used extensively in an example which will be worked out in detail in Section 3.2.5.

# 3.2.3 Formalizing the Specification/Decomposition Process

The specification and decomposition process requires formalism to establish a common frame of reference. This goal can be achieved by using either specification languages or procedural languages. Each option has its own merit and is adequate in describing the system.

1. Specification languages

Specification or functional languages are non-procedural languages, often used for the purpose of specifications. HISP (Hierarchically Structured Specification Processor) [OKAD80] is such a language. HISP manipulates objects which are represented as:

#### P = (Q, S, 0, E)

where P is an object, Q is a set of objects, S is a set of "sorts", O is a set of operators and E is a set of equations. In HISP, sorts are representation of data items relevant to the system. HISP also defines operations on objects (creation, construction, renaming, substitution, refinement) which allow a system to be completely specified. It is also possible to use a flowchart-like type of approach as formalized in [ROSS77b]. Although not a language as such, this method is, in fact, a graphical representation of a functional language.

The advantages of using functional languages are as follows:

- i) their semantics are easy to define,

- ii) they lend themselves readily to expressing mathematically certain properties of the system. (In other words, proofs of correctness are facilitated.),

- iii) they are not encumbered by lower level details which may detract from precise specifications.

The major difficulty associated with their use is that they eventually require translation to a procedural language like Ada\* or Pascal.

\*Ada is a trademark of the U.S. Department of Defense.

#### Procedural languages

2.

The major complaint associated with the use of procedural languages is the presence of lower level details in the specification process. These details have been minimized to a great extent in newer languages such as Pascal and specially Ada. It is now quite feasible to use the data flow arcs of a high level "mixed decomposition approach" as basic data structures and to use procedures (either specified or stubs) to represent the functionality of the system. Stepwise refinement is, of course, possible on procedures not completely specified.

Using procedural languages for specification obviates the need for translation and imposes a strict formalism on the description of the system. It is always possible to introduce a mathematical model by means of assertions.

#### 3.2.4 Ada as a specification tool

Ada is a programming language built to the specifications of the U.S. Department of Defense. It is a powerful language [WEGN80], [PYLE81],

- 36 -

[DOD80], [COMP81] with facilities for data typing, data and procedure encapsulating, support of concurrency, etc.

Some of those features are very helpful in specification/decomposition work:

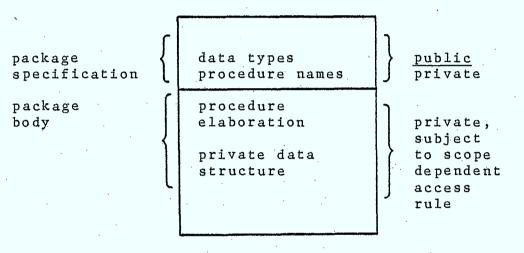

1. Packages

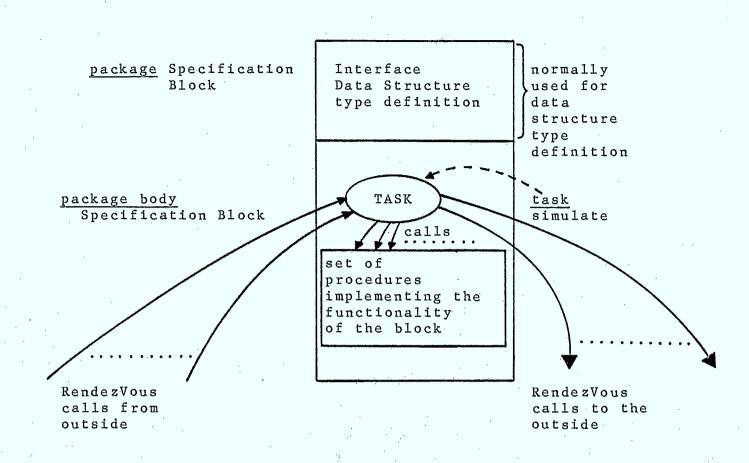

A package is a module encapsulating data and a set of associated procedures. An Ada package is shown in Figure 3.7.

Figure 3.7: An Ada Package

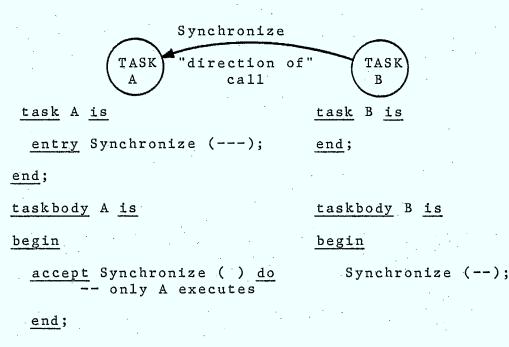

A package comprises two parts: a specification in which the interface to the outside is defined and a body in which the actual processing is done. The body does not have to be completely coded in the early stages of the design; all is required is a complete specification part. The Ada compiler will make the necessary linking adjustments. 2. RendezVous

Ada supports concurrency and therefore has the necessary mechanisms to allow several tasks to execute in parallel. Concurrently executing tasks will often require some means of synchronizing their activities. To this end, Ada provides a RendezVous capability, graphically illustrated in Figure 3.8.

end;

Figure 3.8: An Ada RendezVous

Task B is the active part in the RendezVous of Figure 3.8 and it calls task A. In Ada, tasks have the same specification and body structure than packages. In the specification part of a task, potential RendezVous are listed in the form of entries. A RendezVous is initiated when either task B calls the procedure Synchronize or task A accepts it. If task B is first, it waits until task A accepts the RendezVous. If the reverse occurs, task A is the one waiting. The actual RendezVous takes place when both tasks A and B are ready. During RendezVous, the parallel executions of A and B will be reduced to a serial execution and at the end of the RendezVous, both tasks will resume their parallel execution.

# 3. Separate Compilation Units

There are extensive facilities in Ada for the support of separate compilation units. Separate compilation is possible for library units, package bodies and procedure bodies. Some of the rules governing separate compilation may seem at first a bit intricate, but this feature is extremely useful when attempting stepwise refinement during the decomposition phase. In fact, only the procedure or package interface need be specified initially. The body of a procedure, for example, can be left as a stub and refined later on.

- 39 -

When it comes to specifying and applying the "mixed approach" decomposition to a system, it can be very advantageous to use Ada as the specification language. As a procedural language, Ada would provide the formalism required of such an exercise. The translation from specification to implementation would be done in such a way as to result in code that could very often be of immediate use.

the The end result of "mixed approach" decomposition is a network of computing functions which were further subjected to functional decomposition. Despite its powerful features, Ada cannot be applied directly. What is needed is a construct which would facilitate the specifying of computing functions while at the same time allow for the representation of the functional decomposition process. Such a construct, called a "Specification Block", is shown in Figure 3.9 and is elaborated on

next.

Figure 3.9: Basic Structure of a Specification Block

A specification block is expressed by means of a package; its interface is defined in the specification part of the package. Data structure types are elaborated at that level although similar results can be achieved in the specification part of the "Simulate" task.\* The package body of the specification block contains the "simulate" task and

\* For that reason, the simulation block package will be usually represented only by the package body.

- 41 -

a set of procedures implementing the functionality of the system. Those procedures will be the object of stepwise refinement. The "simulate" task fulfills two functions:

a) Through the RendezVous mechanism, it is linked to the data flow network of the decomposition model. The "simulate" tasks is called and calls other tasks, thereby emulating the flow of data of the model.

b)

The "simulate" tasks embodies the algorithmic structure of a functional block. This embodiment is the result of the sequence of procedure calls the "simulate" task is going through. Functional refinement is made easier when dealing with such a construct.

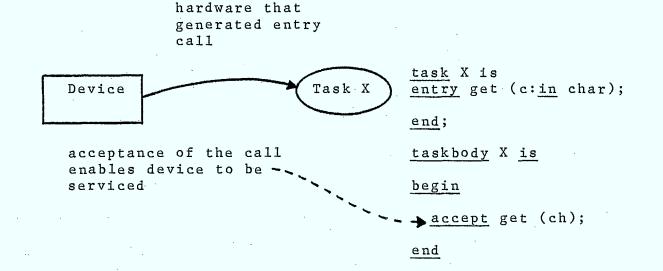

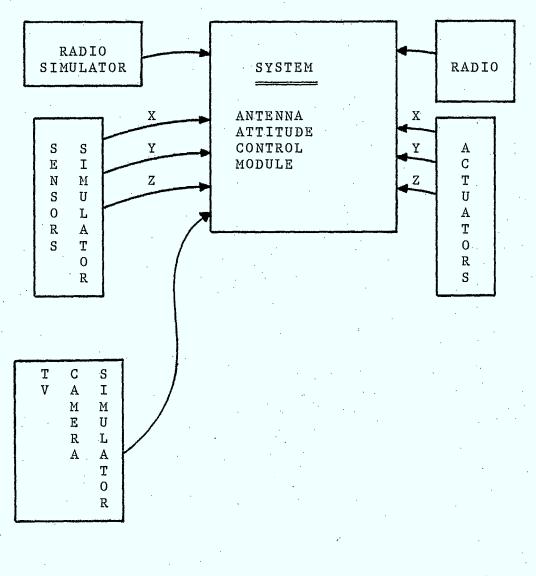

The usefulness of the Ada specification block is not limited to the representation of computing functions. Even lower level devices can be accommodated by Ada, as shown in Figure 3.10, in which an interrupt driven device is interfaced to an Ada module.

- 42 -

Figure 3.10: Device Servicing in Ada

It can be easily seen that, given a system decomposition, a translation can be made of all the functional modules to a network of Ada specification blocks. This process, although awkward and tedious to explain, is relatively straightforward. It is best illustrated by a thorough example of a small part of a system.

4 ዓ

#### 3.2.5 A Decomposition Example

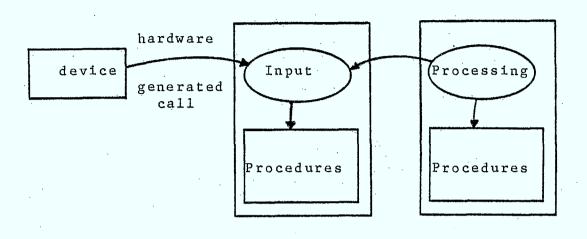

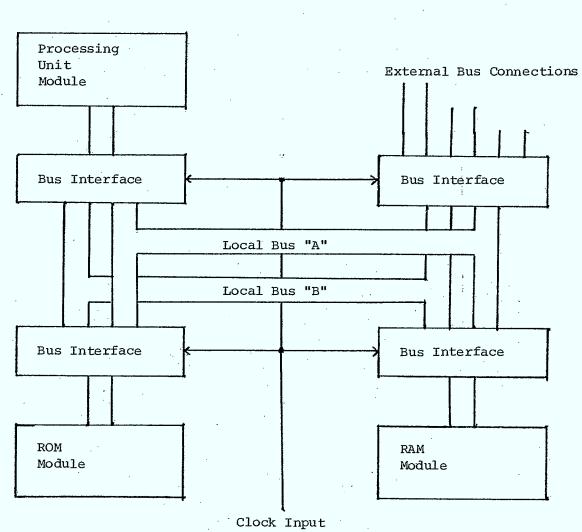

In this example, the decomposition process will be applied to an antenna attitude control module. The example, shown in Figure 3.11, consists of a remote controller for the positioning of a spacecraft antenna. The on-board controller is made aware of the actual position of the antenna through sensors so as to implement a closed loop control. To complement the sensors, a television camera with digital output is also provided. TV Camera

Figure 3.11:

Description of the example

#### 3.2.5.1 Various decomposition levels

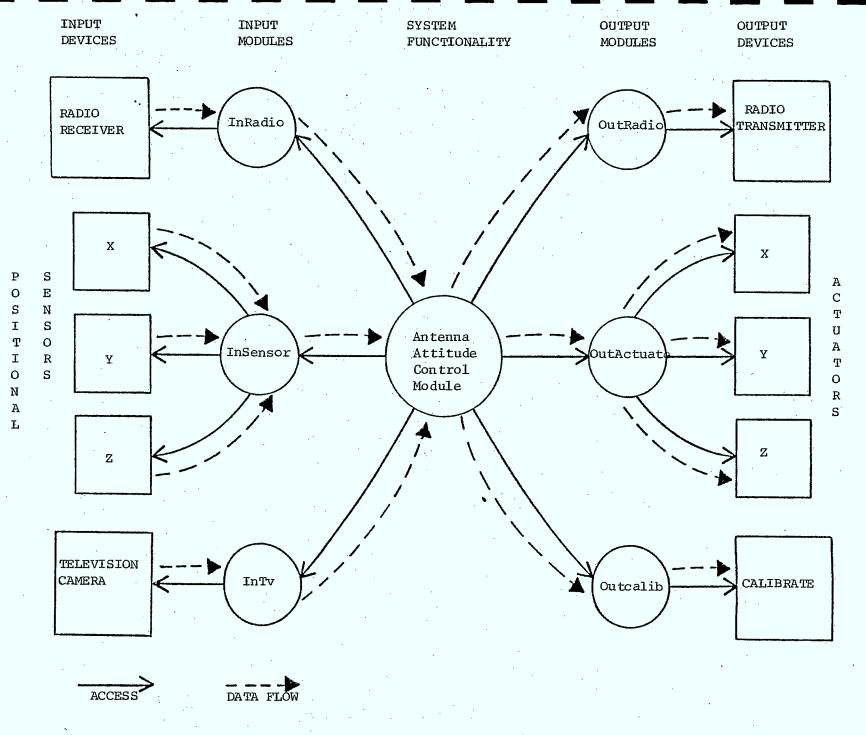

The first attempt at decomposition is shown in Figure 3.12. Three types of modules are visible in that figure:

1- Input modules

InRadio, InSensors, InTv

2- Output modules

OutRadio, OutActuators, Outcalib

3- Functional modules

Antenna attitude control module

The functional module can also be further decomposed as shown in Figure 3.13. In that figure, the data flow model will be the last level of such decomposition. The functions of each module are outlined below, in preparation for functional decomposition (NOTE: numbers correspond to those of Figure 3.13.):

- 1- InRadio is the input module dedicated to the radio receiver. It can be thought of as a device handler.

- 2- InSensor is the input module dedicated to the X,Y,Z co-ordinate sensors.

- 3- InTv is the input module dedicated to the TV camera.

#### • 45 -

Figure 3.12: A first attempt at decomposition

46 -

Figure 3.13: Data Flow Graph

Devices not Shown

1

\*numbers refer to description

4- Command String Interpreter receives commands from the ground station. The commands are structured as shown in Figure 3.14.

# type CommandString <u>is</u> <u>record</u> CommandType: (VisualInspect, Reset, Rotate Calibrate); <u>case</u> CommandType <u>is</u> <u>when</u> Rotate ⇒ Desired Position: Position; <u>when</u> Calibrate ⇒ Desired Accuracy: Accuracy; <u>when</u> VisualInspect ⇒ Magnification:Integer;

Switch: (on,off)

end case; end record;

#### Figure 3.14: Definition of Various Commands

- 48 -

· · · · · ·

The Command String Interpreter will activate the desired modules (and also pass parameters when applicable) based upon the value of the Command type contained in the Command String.

5- PositionTask receives the X,Y,Z position of the antenna. Those values are the result of sampling done at regular intervals. The PositionTask also maintains an up-to-date table of statistics on the dynamics of the antenna.

6- Reset resets the antenna position to a given initial point. It then sends confirmation to the ground station, to indicate the status (success of failure) of the command.

Rotate rotates the antenna to a position 7 specified in the command parameters. An indication of the success or failure of the command is also sent back to the ground station.

8- Calibrate moves the antenna to a known position and re-calibrates the sensors through the use of the Calibrate module. A Report is sent back to the ground station.

9- VisualInspect starts the TV camera and transmit back to the ground station digitized pictures. A VisualOff parameter stops this process.

- 49 -

- 10- ReportFormatter accepts various types of input data, (e.g., confirmation of successful rotation, result of calibration, digitized television pictures, etc.) and prepares them for transmission.

- 11- OutRadio is the output module for the radio transmitter. It is, in fact, a device handler.

12- OutActuator is the output module which takes care of the servo control mechanisms of the antenna.

- 13- OutCalib is the output module dedicated to the Calibrator device.

At this point, it should be noted that, although Input and Output modules have always been included, their presence is not mandatory. In actual fact, practical considerations may dictate that they be incorporated in other modules. However, the reason for their being separate entities is that the functions they implement have to exist in most cases. It is reasoned that it is easy to merge them with other functions and, besides, they add to the clarity of the decomposition exercise.

Following two stages of decomposition with respect to data flow, the system is subjected to a

- 50. -

functional decomposition. The result is shown in Figure 3.15. The various modules are broken down with respect to the functions they are supposed to implement. This functional decomposition is illustrated by the tree structures subtending the data flow modules. The decomposition process is also shown in various stages of completion and it should be remembered that it does not necessarily correspond to reality since its prime purpose is didactic.

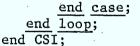

In the complete design methodology, the functional decomposition, as exemplified by the diagram of Figure 3.15, is a transitory step. Its main purpose is to provide a bridge to a system representation using the Ada specification blocks. This system representation is to be found in Figure 3.16.

several differences between There are the system representations of Figures 3.15 and 3.16. The most noticeable is, of course, the use of a procedural language to describe the system. The formalism of Ada helps in solidifying the description of the system and of its various characteristics. Another extremely important point

- 51 -

is the disappearance of data flow arcs and their replacement by procedure call arcs. It should be noted that the direction of a procedure call arc is not necessarily indicative of the direction of the flow of parameters, if and when parameters are passed. In Ada, the direction of a procedure call arc has a further significance beyond determining the calling and called parties. In fact, it plays a role in establishing how control is passed, and if not properly set up, may become the proximate cause of deadlock. Considerations on how the direction of those arcs affects deadlocks will be found in Section 3.2.5.3.

Other aspects of Figure 3.16 are worth mentioning briefly and are listed below: i) There is direct linking to devices. Hardware generated interrupts are interpreted as procedure calls into one of the input or output modules.

The control structure of the Rendez Vous mechanism in Ada has been examined earlier. Based upon that knowledge, it is interesting to observe that, for a procedure call from a main functional module to one of the input/output modules, the body of that procedure will be in the called module.

- 54 -

ii)

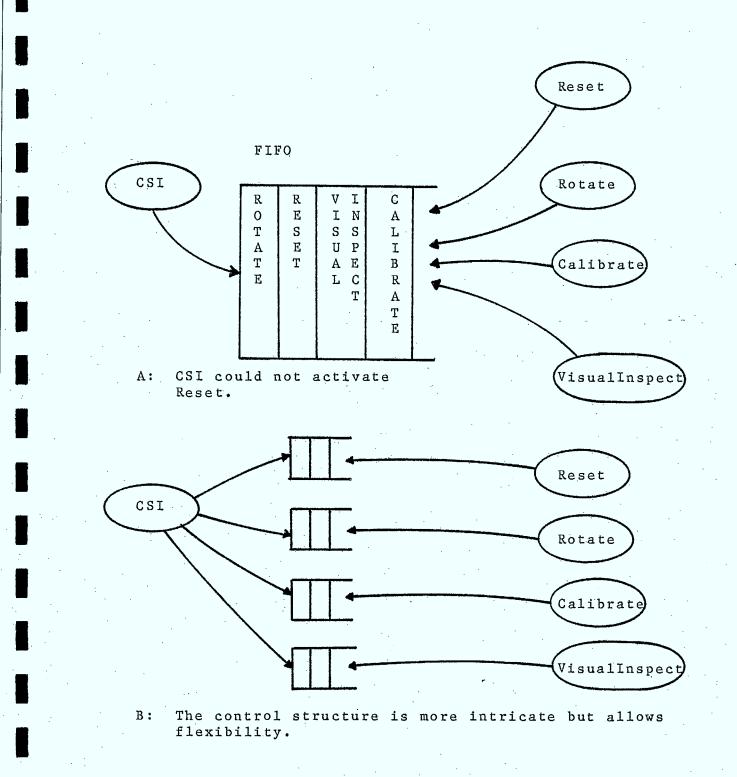

iii) The structure of the RendezVous, [SILB8], [MAHJ81], [LAFE81], while generally very flexible, is sometimes awkward to manipulate, especially in cases where control is to be dispatched to other modules. Two cases should be considered:

> Case 1: The Command String Interpreter (CSI) passes control to one of the Reset, Rotate, Calibrate, or VisualInspect modules depending on the Command String, the CSI got from the InRadio module. The procedure call arcs afferent to the CSI module are distinct, (i.e., Give Control Reset, Give Control Rotate,

> > Give Control Calibrate,

Give Control Visual Inspect). Were they not distinct, the CSI module would not be able to activate the desired module. This situation is shown graphically in Figure 3.17 (a & b).

- 55 -

- 56 -

Case 2: Calls to the Positional module from other modules (in order to co-ordinates) are get not distinct. In this case, the need for distinct procedures is . obviated by the structure of the system. The calling modules, (Reset, Rotate and Calibrate) will normally be waiting for the CSI module to give them control. Only one of them will execute at any one time and, as such, no contention is present, hence no need for separate calls.

Further functional decomposition can be carried out easily with the system model of Figure 3.16. This will be demonstrated by specifying a subset of modules such as the CommandStringInterpreter and the Reset modules. To keep the example simple, the packaging of those modules will not be shown; Ada manuals [DOD80], [WEGN80], [PYLE81], describe how to build packages quite well. The description will proceed from tasks to procedure stubs. The reader is also referred to Figure 3.14 which contains a full type definition of a command string.

- 57 -

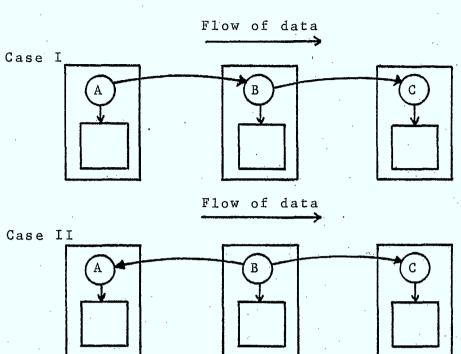

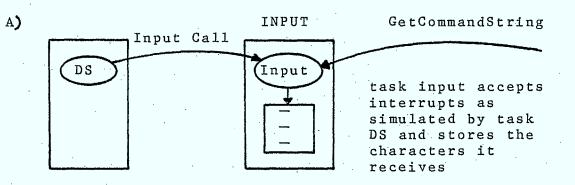

first task to be specified is the The Command String Interpreter task which interfaces with most of the tasks in the system. The CSI task in Figure 3.18, with the function shown is "GiveCommandString" specified separate. as Figure 3.19 describes how the link up to the CSI module will be done. The Reset module is of greater complexity than CSI and, as such, makes an interesting example. It is shown in Figure 3.20. No entry specifications are found in task Reset since it is the active party in RendezVous all the

time.

58 -

#### task CSI is

entry GiveControlReset (CS: out CommandString); entry GiveControlRotate (CS: out CommandString); entry GiveControlCalibrate (CS: out CommandString);

entry GiveControlVisualInspect (CS: out CommandString); end CSI;

<u>task body</u> CSI <u>is</u>

LN: CommandString

<u>function</u> GiveCommandString (Y:CommandString) <u>return</u> CommandString <u>is separate</u>

#### begin

loop

GetCommandString (LN); case LN.CommandType is

#### NOTE:

It should be realized that in this case the function GiveCommandString is redundant. It was included to show how, if such a function became necessary, link up is possible either to inside or outside the package.

Figure 3.18 Command String Interpeter (CSI)

## separate(CommandStringInterpreter);

function GiveCommandString(Y:CommandString)returnCommandString is Test:boolean; function CheckValidityOf(X:CommandString)returnboolean is separate;

<u>iunction</u> oneckvariattyor(k.oommandotring)<u>ictum</u>oorcan <u>is</u> separates

begin

Test:=CheckValidityOf(Y); <u>if</u> Test <u>then</u> return Y; <u>else</u> raise "exception"; <u>end</u> if; end GiveCommandString;

# Figure 3.19: Expansion of a separate procedure

- 60 -

```

task Reset;

```

task body Reset is CS: CommandString; CST: CommandStatus; CP: CurrentPosition; Mssg: Message: DV: DisplacementValue; InitialPosition: Position:=0,0,0;

```

procedure GiveControlReset(X:CommandString) is separate;

procedure GetPosition(X:Position) is separate;

procedure NewPositionDisplacement(X,Y:Position) is separate;

procedure MoveAntennaPosition(X:DisplacementValue;Y:CommandStatus) is separate;

procedure SendMessage(X:Message) is separate;

procedure AbortSystemActivities is separate;

```

#### begin

| <u>loop</u>                |                        |

|----------------------------|------------------------|

| GetCommandString(CS);      | part of RendezVous     |

| AbortSystemActivities;     |                        |

| GetPosition(CP);           | part of RendezVous     |

| DV:=NewPositionDisplacemen | t(CP,InitialPosition); |

| MoveAntennaPosition(DV,CST | );                     |

| if CST=Success             |                        |

| then Mssg:=Success;        |                        |

| else Mssg:=Failure;        | · · · ·                |

| raise actuator failur      | e;                     |

| end if;                    |                        |

| SendMessage(Mssg);         |                        |

| end loop;                  |                        |

| end Reset;                 | •                      |

Figure 3.20: Description of the Reset Module

Task Reset also exemplifies the use of separate procedures. Those procedures can either be in the package itself or in a different package which may be compiled separately. In the latter case, many stages of refinement may have taken place; proper procedure specification ensured that the rest of the model was not affected by changes in the separate procedure body.(\*)

#### 3.2.5.2 Observations on the Model

The use of the decomposition methodology yields a system model which exhibits several desirable properties. The most important advantage is that the system is described formally as opposed to an informal description whose meaning may be subjected The model is also easy to to misinterpretation. visualize. Procedures and functions which serve may be grouped together similar purpose in anticipation of a complete software design. Such grouping of subprograms would optimize the coding of the system tasks. It should be realized, however, that the system tasks obtained through decomposition are not necessarily optimal nor are they the only set of tasks which could be obtained. Different designers or analysts will more than likely arrive at different task decomposition.

(\*) The Ada Manual [DOD80] has a lot more on that issue.

- 62 -

The Ada representation of the model makes an early compilation possible. This compilation, although not intended to produce executable code, can check the validity and consistency of data types and most importantly of procedure calls. The network of Ada building blocks can also be incorporated in a testbed, early in the design phase. This will be covered shortly in more detail.

The importance of properly designing the model with respect to procedure call arcs was stressed before; a few guidelines will now be provided. Three cases are of interest and are shown in Figure 3.21.

63 -

# Figure 3.21: Procedure call arrangements in Ada

- 64 -

Case I is the most likely situation to be Task A calls Task B encountered. and passes parameters to the latter. The same process takes place again for B and C. The direction of the data flow also coincides with that of the calls. This case of innocuous appearance can be a potential cause of deadlock if a cycle is allowed to form, (e.g., A calls B and is delayed because B called C and B was delayed because C had called A and had been delayed, etc.)

<u>Case II</u> is introduced to lessen the possibilities of deadlock when two tasks (e.g., A & C) have to communicate with each other but, at the same time, cannot afford to wait on one another. The reason for this unwillingness to wait may be that both A and C are tasks offering general purpose services to other tasks. It should also be noted that agent task B will convey the parameters of the call from A to C only. If a reverse flow is desired, another agent task is required.

Deadlocks are not likely to occur in this arrangement because task B will be alternately waiting on A to get a message, and on C to give the message. The actions involved in each case are very short and

- 65 -

should hinder neither A nor C, as task B is doing the waiting. It is easily seen that the overhead in terms of executive services (e.g., context switching) may be substantial for this configuration.

Case III also lessens the possibilities of deadlock and is used in cases such as:

- a) An input (or output) module which has to service hardware interrupts while at the same time making the data available to other tasks in the system.

- b) A module which provides various services to other tasks, and as such, cannot be delayed.

An example of an arrangement typifying Case III is shown in Figure 3.22 which depicts an input module servicing a hardware device. The input module makes the data that it collected available to the processing task.

- 66 -

Figure 3.22: Representation of an Input Module

The reason behind the call structure of Figure 3.22 is that the Input task should always (ideally) be able to schedule a hardware generated entry call from the device. If that is not the case, a loss of input data will result, caused by either too fast a device or an inadequate call structure. The proposed structure, however, affords the Input task the best potential for quick scheduling of the service requests from the device.

67

Case II and Case III help design systems with lower probability of deadlock. They do not completely eliminate the risk of deadlock. Total elimination of deadlock can only be achieved by a careful design and, if need be, some simulation to increase the confidence in the operations of the system.

- 68 -

3.2.5.3 System Simulation and Testing

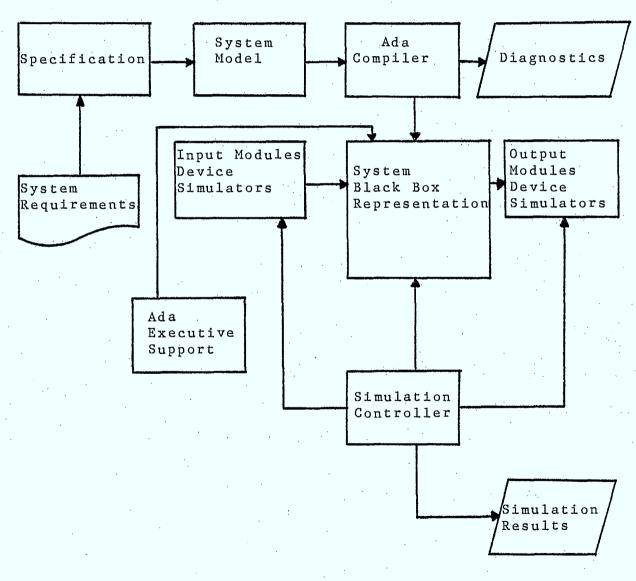

Preliminary simulation and testing can be attempted on a model which is completely (or even only partially) specified by Ada specification blocks. Figure 3.23 shows the modelled system as a black box surrounded by device simulator modules.

#### Figure 3.23: System Model and Test Bed

- 69 -