# **Eidetic Systems Corporation**

A review of spacecraft fault-tolerant computer design concepts / T. Gomi, M. Inwood

Checked 11/83

Department of Communications

DOC CONTRACTOR REPORT

DOC-CR-SP-82-049

Industry Canada Library . Queen

· JUE 2 0 1998

Industrie Ganada Bibliothèque Queen

DEPARTMENT OF COMMUNICATIONS - OTTAWA - CANADA

SPACE PROGRAM

TITLE: A Review Of Spacecraft Fault-Tolerant Computer

Design Concepts

AUTHOR(S): T. Gomi, M. Inwood

ISSUED BY CONTRACTOR AS REPORT NO: 82-001

PREPARED BY: Eidetic Systems Corporation

P.O. Box 13440

Kanata, Ontario

K2K 1X7

DEPARTMENT OF SUPPLY AND SERVICES CONTRACT NO: 3ER.36100-1-0274

SN: OER81-03138

DOC SCIENTIFIC AUTHORITY: R.A. Millar

CLASSIFICATION: Unclassified

This report presents the views of the author(s). Publication of this report does not constitute DOC approval of the reports findings or conclusions. This report is available outside the department by special arrangement.

DATE: March 3, 1982

A REVIEW OF SPACECRAFT FAULT-TOLERANT COMPUTER DESIGN CONCEPTS

Technical Report No. 82-001

T. Gomi / M. Inwood Eidetic Systems Corporation March 3, 1982.

P91 C655 G64 198.2 DD4589357 DL4589391

#### CONTENTS

|    | Acknowledgements                                                                                                                   | Page<br>i                       |

|----|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|    | Acronyms                                                                                                                           | ii                              |

| 1. | Summary                                                                                                                            | 1-1                             |

| 2. | Introduction                                                                                                                       | 2-1                             |

| 3. | JPL's Unified Data System/Fault-Tolerant<br>Building Block Computer                                                                | 3-1                             |

| ٠. | 3.0 General 3.1 UDS Design Concepts 3.2 FTBBC Components 3.3 FTBBC Features Tree                                                   | 3-1<br>3-1<br>3-5<br>3-1        |

| 4. | Comparisons with other Fault-Tolerant<br>On-Board Computers                                                                        | 4-1                             |

|    | 4.0 General 4.1 Features of the OBDH 4.2 Features of the AASC 4.3 The Basis of the Comparison                                      | 4-1<br>4-1<br>4-3<br>4-7        |

| 5. | Discussion of Relevant Technology<br>Developments                                                                                  | 5-1                             |

|    | <ul> <li>5.0 General</li> <li>5.1 Distributed Systems and Local Area Network</li> <li>5.2 Structured Design and Software</li></ul> | 5-1<br>5-1<br>5-2<br>5-3<br>5-4 |

| 6. | Conclusion                                                                                                                         | 6-1                             |

|    | References                                                                                                                         | 7-1                             |

|    | Appendix A - D.A. Rennels Interview.                                                                                               | A-1                             |

|    | Appendix B - FTC Design Rules (Eidetic)                                                                                            | B-1                             |

#### ACKNOWLEDGEMENTS

This study was performed for the Department of Communications, Communications Research Centre, Shirley Bay, Ottawa, Ontario, Canada under DSS Contract OER 81-03138.

Eidetic Systems Corporation would like to acknowledge the support of Dr. D.A. Rennels of the Jet Propulsion Laboratory of the California Institute of Technology and Dr. George C. Gilley of The Aerospace Corporation, Los Angeles, California, for their comments and cooperation obtained during the course of the study.

The authors are also indebted to R. Millar, of the Communications Research Centre, Ottawa for his guidance and support.

## ACRONYMS

```

AASC

Advanced Autonomous Spacecraft Computer

ABI

Address Bus Interface (FTBBC/MIBB)

Ada

DoD defined Ada programming language

AE

Access Element (FTBBC/MIBB)

ALU

Arithmetic-Logic Unit

AP

Attached Processor (AASC)

ASM

Autonomous Spacecraft Maintenance

BA

Bus Adaptor (FTBBC/BIBB)

BB

Building Block

Bus Controller (FTBBC/BIBB)

BC

Bus Interface Building Block (FTBBC)

BIBB

Bus Interface Unit (AASC)

BIU

BCT

Bus Control Table (FTBBC/BIBB)

Bit Replacement

BR

Core-BB Core Building-Block (FTBBC)

CP

Command Processor (FTBBC/HLM)

Check Bits Parity Check

CPC

CPDU

Control and Power Distribution Unit (OBDH)

Central Processing Unit

CPU

CRC

Cyclic Redundancy Check

CTU

Central Terminal Unit (OBDH)

Data Bus Interface (FTBBC/MIBB)

DBI

DB

Data Bus

Double error

DE

Direct Memory Access

DMA

EBI

External Bus Interface (FTBBC/MIBB)

ECS

Error Control Section (FTBBC/MIBB)

ESA

European Space Agency

ESTEC

European Space Technology and Research Centre

FHE

Fault Handler Element (FTBBC/Core-BB)

Fault Handler (FTBBC/BIBB)

FΗ

FΡ

Format Processor (FTBBC/HLM)

Fault Sequencer (FTBBC/Core-BB)

FS

Fault-Tolerant Building Block Computer

FTBBC

FTC

Fault-Tolerant Computing

GDP

General Data Processor (AASC)

HLM

High-level Module (FTBBC)

Internal Bus Interface (FTBBC/BIBB)

IBI

IBS

Intercommunications Bus System (FTBBC)

IOBB

Input/Output Building Block (FTBBC)

IOP

Input/Output Processor (AASC)

ΙP

Interface Processor (AASC)

JPL

Jet Propulsion Laboratory

LAN

Local Area Network

LSI

Large Scale Integration

MCS

Memory Control Section (FTBBC/MIBB)

```

Memory Control Unit (AASC) MCU MDR Memory Data Register (FTBBC/MIBB) Master Fault Indicator (FTBBC/Core-BB) MFI Memory Interface Building Block (FTBBC) MIBB MIPS Mega Instructions Per Second NIU Network Interface Unit (AASC) NRZ Non-Return To Zero OBDH On Board Data Handling, an ESA standard for computer based on-board housekeeping methodology (ESA) PCE Process Check Element (FTBBC/Core-BB) PLA Programmed Logic Array RAM Random Access Memory RBI Remote Bus Interface (ESA/OBDH) RTI Real Time Interrupt (FTBBC) RTU Remote Terminal Unit (OBDH) RS Recovery Sequencer (FTBBC/Core-BB) SCCM Self-Checking Computer Module (FTBBC) SE Single Error SEC/DED Single Error Correction/Double Error Detection SGC Syndrome Generator Check (FTBBC/MIBB) SSI Small Scale Integration TM Terminal Module (FTBBC) UDS Unified Data System - a JPL designation for a standardization of fault-tolerant on-board computer system.

Very Large Scale Integration

VLSI

#### 1. SUMMARY

The Fault-Tolerant Building Block Computer (FTBBC), designed by the Jet Propulsion Laboratory (JPL) for satellite on-board use, incorporates extensive fault-tolerant mechanisms. An evaluation of these are made in comparison with two systems which have similar objectives; a European system developed for unmanned applications, and the preliminary design for implementation of the latest, or imminently available technology. These are the European Space Agency's On-Board Data Handling (ESA/OBDH) system and the Advanced Autonomous Spacecraft Computer (AASC). The capabilities and limitations of the FTBBC are pinpointed by reference to this comparison and to recent developments in associated technologies. The conclusions drawn from this comparison point to the direction in which future advances should lead.

Current research is investigated and its relevance to space applications is discussed. Contacts made within the space community are reported and information gained through these channels is included.

A set of design rules which has evolved during the study is appended.

#### 2. INTRODUCTION

The Jet Propulsion Laboratory's (JPL) Fault-Tolerant Building-Block Computer (FTBBC) was initiated in the early 1970s as an exercise in designing an on-board computer which would take advantage of current developments in the fields of fault-tolerance and technology. In particular, the FTBBC one of the first computers to incorporate extensive fault-handling functions in its hardware design. study reveals, the mechanisms to detect hardware faults, and confine them are extensive, whilst attempts are also made to analyze and recover from them. The flexibility of the Central Processing Unit (CPU) and the memory selection afforded by the Self-Checking Computer Module (SCCM) arrangement, for example, are essential features of any fault-tolerant computer design. Furthermore, the Unified Data System/FTBBC is the first major computer system development based on microcomputer technology that addresses issues related to fully distributed systems, either for space use or otherwise. A version of the FTBBC will be flown on Galileo (Ref.1).7

A second computer of the building-block type, the European Space Agency's On-Board Data Handling (ESA/OBDH) system, which was well defined by 1973, has been studied. This was also intended as a reusable, distributed system for unmanned satellites, and contains some redundancy and building-block features. It was the result of combined development by European countries. The Europeans made no effort to use available components and designed the system in the custom-built style traditional to the space industry. High costs and long development time were mitigated by distributing the responsibility for the various modules amongst member countries.

Development of the FTBBC computer has now been in progress for a decade. During this time research has gone ahead in fields which may well have a considerable impact on fault-tolerant concepts and methods of implementing them. Aspects which have been problematical in the past are now being approached, and solutions are being presented to concerns which were not clearly understood at the time of the FTBBC. This report is an attempt to understand and high-light these concepts, and study their relevance to the present stage of the FTBBC.

A further outcome of this study has been the formulation of the Fault-Tolerant Computing Design Rules. This is a set of criteria which, it is felt, should be applied to the design of on-board spacecraft computers. These rules have been used as a point of reference in the comparison contained herein.

An understanding of the present status of the FTBBC and current research has been gained by conducting personal and telephone interviews with Dr. D.A. Rennels and other JPL personnel and also with other active participants in the area of on-board computing. Reference has been made to the open literature available from JPL, ESA and other international institutions.

# 3. JPL'S UNIFIED DATA SYSTEM/ FAULT-TOLERANT BUILDING BLOCK COMPUTER

#### 3.0 General

The FTBBC project grew out of an earlier study on the Unified Data System (UDS) at JPL (Ref.4) in which Dr. David Rennels, the chief architect of the present system, took a leading part. Whereas the UDS is a system level design, the FTBBC is a hardware implementation of a Self-Checking Computer Module, an essential component of the UDS system. Since the FTBBC is best viewed in this context, a brief outline of the UDS is given first.

## 3.1 Features of the Unified Data System (UDS)

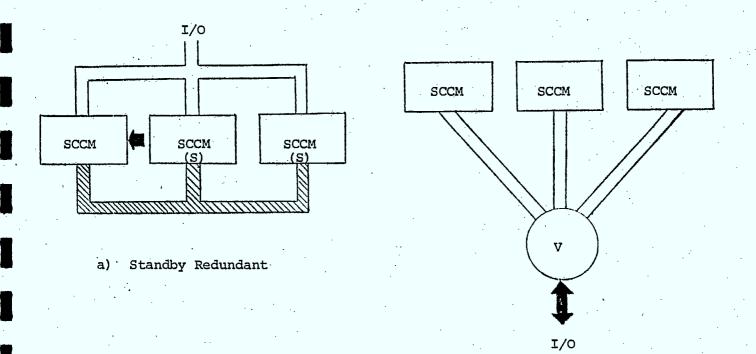

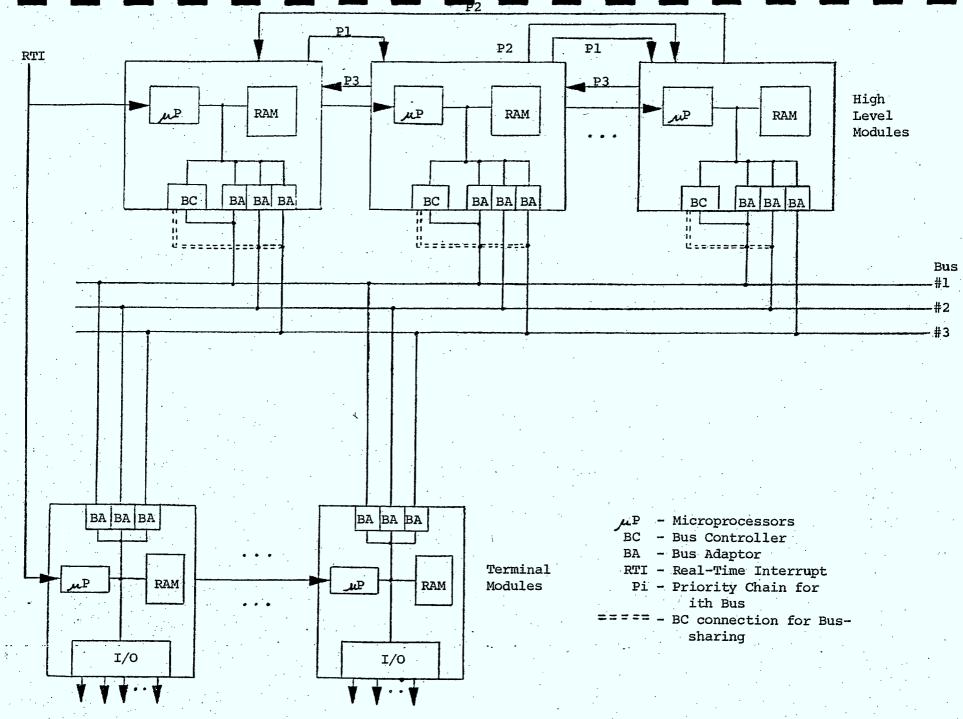

The UDS was developed as a distributed computer network architecture for spacecraft on-board processing. It consists of a set of SCCMs connected by a redundant set of intercommunication buses. Microcomputers, utilized as High Level Modules (HLM) or Terminal Modules (TM), may be combined in a variety of different configurations, as shown in Figure 1.

TMs are dedicated to a particular spacecraft subsystem and are responsible for control and data collection within it. A TM cannot initiate bus communications but can be commanded to fetch or deposit data into its memory. In addition, it actively supports DMA transactions and it can be accessed through several buses simultaneously.

HLMs are responsible for coordinating processing within the remote TMs, for controlling the Intercommunication Bus System (IBS), and for high level processing such as data compression and decision making. HLMs contain the same internal components as the TMs but with the addition of a Bus Interface Building Block (BIBB) programmed as a Bus Controller (BC). Unlike the TM, an HLM has no I/O circuitry apart from the IBS and only communicates with other computer modules.

Each serial bus is connected to a Bus Adaptor (BA) in each of its associated SCCMs (HLM or TM). It is also assigned a primary BC in its controlling HLM. Control can pass to another HLM if the bus is not powered or the processor commands release to a lower priority BC for a specific time interval. Priority is established on a fixed basis and implemented through a daisy-chain structure for each bus which is shown in Figure 2. This, theoretically, enables spare modules to take over from a failed HLM or, in the event of bus failure, the BCs may share one bus. The buses are physically independent of each other and

SCCM SCCM SCCM SCCM SCCM HLM (S) (S) SCCM SCCM SCCM SCCM SCCM SCCM SSM (S) (S) (S) I/O I/O I/O

Voted Configuration

I/O

I/O

I/O

I/O

I/O

III Intercommunications Bus

HLM - High Level Module

SSM - SCCMs in Subsystems

(S) - Spare Module

Fig.1 Fault-Tolerant SCCM Configurations

Fig.2 RTI and Daisy-Chain Priority in SCCM Distributed Network.

there is no common clock. Each SCCM uses its own internal clock and the buses use the clock of whichever module is transmitting.

The number of buses is dependant on mission and redundancy requirements. In the event of failure a mission may be reconfigured throughout - even to the extent of a single remaining bus supporting essential functions.

One HLM is designated as the system executive and issues a common system-wide clock, the Real Time Interrupt, (RTI) of 2.5 ms. All modules receive and compare the RTI with their own internal clocks. On failure of an RTI generator, the computers will automatically switch to a backup. If an individual clock fails then damage will be confined to one module. Figure 2 shows the RTI line between modules.

Subordinate HLMs or TMs are commanded to start specific programs which the timing information from the executive HLM will synchronize with the rest of the system. Most programs are self-synchronizing and timing within them is tightly regulated, the time count of each event being precisely specified.

Each HLM/TM contains an identical local executive program for communication with user software. Software is run in a foreground/background partition with well-defined segmented programs running concurrently in the foreground, whilst more complex and lengthy programs are assigned to the background mode. The local executive is responsible for activating and deactivating foreground/background programs using a scheduling table. A UDS Program Design Language enables a program to communicate with the executive and request modifications to start, stop, suspend or delete itself.(Ref.5) On completing the execution of available foreground programs, control is returned to the background program for the remainder of the time slot.

I/O granularity is defined by sampling inputs and holding them for a fixed period. Several segments of concurrent foreground programs may be executing during a time period and their outputs collected and held for simultaneous execution at the end of the time period. Programs can be removed, added and re-ordered within a time interval without impacting others. This approach is intended to allow a great deal of visibility into the system and to simplify simulation, debugging and modification of software.

Fault-tolerant aspects of the software are mainly confined to increased reliability and testing. Timing has been simplified at the intercommunication bus interface to obviate incompatibilities between user-supplied subsystems. Bus access is

restricted to localize the effects of software failure. Reasonableness checks at the HLM level can verify the proper functioning of low level dedicated software. The HLM has little actual protection against software faults. The UDS local executive has a mechanism for software fault detection which checks proper return of control after execution of a foreground program. In the event of a problem, a software fault is signalled and a user-supplied recovery routine is executed.

Fault recovery requirements for the UDS include a dedicated "hot" spare for the system executive HLM. Cross-checking by modules at each RTI will reveal failure of either one and trigger recovery of the extant module. It should also have ability to activate a further "hot" spare if necessary. A primary HLM generates output and gathers data for the spare and itself. Additional "hot" spares may be utilized under critical conditions. Other HLMs are backed-up by non-dedicated spares. Controlling HLMs are responsible for polling TMs, recognizing failures, internal reconfiguration where possible or continuing operation in a degraded mode. Bus system failures are determined by rerouting suspect messages through a different HLM-bus configuration. Since TMs are dedicated, their spares must also. Such spare TMs are assumed to be physically built into each subsystem. The fault-tolerant responsibility of a TM is detection within its associated subsystem and repairs where possible. Where repair is not possible the TM records error information, institutes a "safe" disabled state and notifies its HLM.

#### 3.2 Features of the FTBBC

## 3.2.1 The Self-Checking Computer Module (SCCM)

The FTBBC itself arose from the desire to combine off-the-shelf components into an SCCM (Ref.3). The appeal of this approach lies in the following features:

- proven reliability of components

- shorter development time

- flexibility of configuration for different applications

- easy upgrading of facilities and standards.

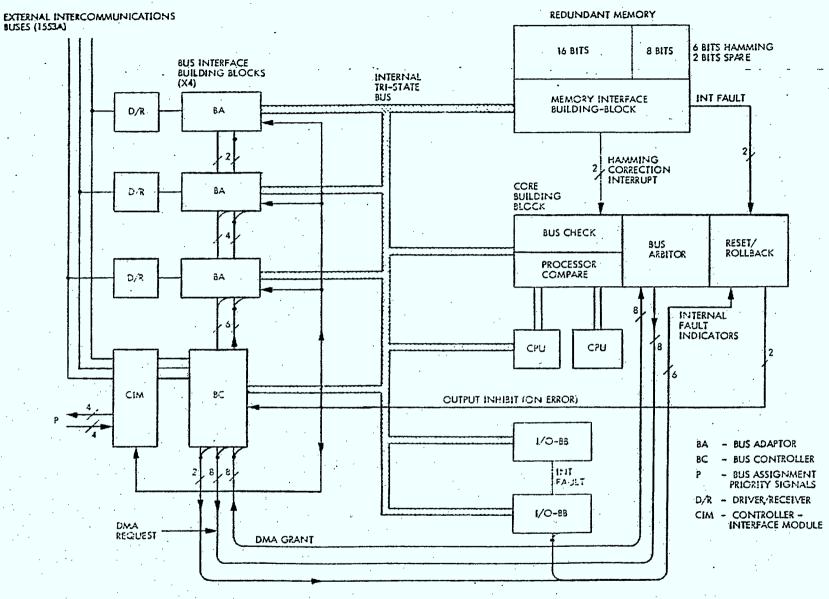

The building blocks, four in number, are intended as VLSI fault-tolerant interfaces to the standard components. They consist of the Memory Interface Building Block (MIBB), Programmable Bus Interface Building Block (BIBB), Core Building Block (Core-BB), and the I/O Building Block (IOBB). Figure 3 shows these building blocks as they are combined to form a self-checking computer module (SCCM). The SCCM can be designated either as an HLM or TM. The building blocks should be able

Fig. 3 The Self-Checking Computer Module (SCCM)

to detect faults internally and in their associated circuitry and give a fault indication to the Core Building Block. The SCCM should, additionally, be able to signal its own malfunctions to other SCCMs and disable its outputs when necessary.

## 3.2.2. Memory Interface Building Block (MIBB)

The memory module consists of two parts; a set of RAM chips and the MIBB. Memory consists of 24 bits, separately packaged in order to contain circuit failure damage. Sixteen bits are used for storage, six for Single-error-correcting/Double-error-detecting (SEC/DED) Hamming code and two are redundant bits in case of failure.

The BB itself is responsible for interfacing memory to the internal bus. It is capable of implementing fault detection and correction within memory using Hamming code and within its own circuits. Information transfer on the internal bus is safeguarded by parity generation and checking. Fault conditions are signalled to the Core-BB and, upon system command, up to two faulty bit planes in memory can be reconfigured.

The memory module uses "memory-mapped I/O" which avoids processor specific I/O operations and also allows access to building blocks by internal SCCM software and Direct Memory Access (DMA) by other SCCMs via the internal bus. This gives an external SCCM the ability to load and read memory via the bus, sample error status information, command internal reconfiguration, and even remotely control I/O in a faulty SCCM. Optional configurations available to the user include variations in memory size (8K, 16K, 32K) and a choice of Ham or non-Ham mode. Non-Ham mode, i.e. without Hamming code, is provided for applications requiring very low power, weight, and volume. In this mode, error detection, correction, and bit-plane replacement are performed under system control, but two parity bits for error detection are retained in the MIBB.

All circuits within the MIBB are either self-testing, fault-secure, or duplicated so that no single circuit failure will produce an undetected output error.

The MIBB consists of four sub-elements: Address Bus Interface (ABI), Error Control Section (ECS), Data Bus-Storage Array Interface (DBI), and Memory Control Section (MCS).

The ABI provides the address parity checking and decoding required to select a memory module. An incoming address is stored in the Memory Address Register (MAR) and validated before a read/write operation is performed. If no errors are detected the low-order 12 bits are sent to the Storage Array

Block for on-chip decoding. The high-order bits are detected and used for memory-mapping. An alternative is to associate a separate decoder with each bit-plane enabling the single error correction/double error detection SEC/DED data word error code to be used in the address decoding. The address which is currently being referenced is stored for future diagnosis in case a fault recurs.

The ECS is concerned with error detection, correction, and analysis within the MIBB. It generates and checks Hamming code check bits and syndromes, and byte parity for the internal bus. ECS circuits are self-testing. The Error Status Register/Memory Error Interrupts issue two fault-detection signals:

- a code-correction indicator, which is sent to the duplex processors as an interrupt indicating that a single memory bit is being corrected by Hamming code. This facilitates the processor's decision on bit replacement.

- internal fault indicator for faults which cannot be corrected within the memory system i.e., when:

- a fault is detected within the MIBB itself

- improperly coded information is received over the internal bus

- a data error occurs within memory that cannot be corrected by Hamming code.

This internal fault indicator is sent to the Core-BB which may, in the case of a transient error, be able to resume correct operations using a rollback or reset/restart sequence.

All circuits are self-testing.

The DBI interfaces the Memory Data Register (MDR) with the internal bus. The MDR consists of two Data Bit Modules, a Check Bit Module for storing Hamming codes, a Replacement Control Section containing the spare bit planes, and interfacing networks. In the event of a faulty bit plane, error decoding is performed on chip but the replacement decision is made by the system.

The MCS generates control signals to implement operation and command algorithms. Read/write instructions with low-order addresses are treated as normal memory operations. High-order addresses are reserved for "memory-mapped I/O". Certain of these out-of-range commands are recognized as pertaining to the MIBB.

## 3.2.3. Core Building Block (Core-BB)

The Core-BB is responsible for:

- synchronizing and comparing duplex CPU outputs

- fault-handling through-out the SCCM.

- internal bus arbitration

One processor is designated as primary and the other as check processor. Processor faults are detected by the Processor Check Element (PCE) by running two synchronized units using the same data and executing the same programs in lock-step. Parity coding of incoming data is checked. Outputs to the internal bus are compared and outputs to address and data buses are parity encoded. The PCE contains self-checking parity checkers, a duplex command decoder and morphic (one-out-of-two) reduction trees. It also samples various fault indicators to provide information for external computer modules.

The Bus Arbitration Element (BAE) accepts bus request signals from the various DMA controllers throughout the SCCM and obtains release of the bus by the CPUs. Access is granted to requesting BB's on the basis of a fixed hardware priority. The BAE signals are duplicated and morphically compared.

Within the Fault Handler Element (FAE), the Fault Synchronizer (FS) accepts fault indicators from throughout the SCCM and morphically reduces them to produce a single clock synchronized morphic fault indicator, the Master Fault Indicator (MFI).

This MFI is sent to the Recovery Segment which disables SCCM output and resets the CPUs. A program rollback can optionally be caused and computation reinitialized. If no additional faults are detected the processors can reenable the module.

The FS and Recovery Sequencer (RS) are duplicated and paired and either pair can disable SCCM output. RS outputs are also compared and disagreements signalled to both Fault Sequencers.

There is a small circuit provided for manual or external module control. This facilitates program restart either by front panel switches or under program control via out-of-range commands.

## 3.2.4. Bus Interface Building Block (BIBB)

The BIBB enables information to be transferred between SCCMs via an intercommunications bus system. It is programmable as either a Bus Controller, one per HLM, or a Bus Adaptor, one per bus in each HLM or TM. They utilize the MIL-STD-1553A bus format, with enhanced capabilities.

The BC can communicate with several redundant buses. A BA is connected to only one bus and serves as a remote terminal. The Controller and Adaptors operate in a relatively autonomous fashion. Their enhanced capability enables them to move data directly between SCCM memories attached to a given data bus with a minimum of software support.

When an HLM wishes to initiate a data transfer between modules on the bus it alerts the BC. This reads a Control in its host's memory, specifying the source and destination of information along with the length of transmission. specifies one BA as a data source and one or more remote BAs as data acceptors and names the data to be moved. As the 1553 format does not provide directly for multiple acceptors, additionmodules must be commanded to "listen in" on a terminal-to-terminal transmission. The specified data extracted by the BA from its host's memory using cycle-stealing and is placed on the bus. It is removed from the bus simultaneously by the acceptor BA and loaded into its SCCM host's memory. The BC monitors this process and signals completion to the host. As many as three buses may communicate with an SCCM without conflict. A BA acts only in response to a Bus Controller, either remotely or within its own SCCM. A BC or BA can recognize several out-of-range addresses relevant to their own functions.

The internal structure of a BIBB is the same for a BC or BA and contains the following:

- the Mill; a small processor with ROM, RAM, internal registers, and an Arithmetic and Logic Unit (ALU). It has responsibility for generating addresses for DMA, word counting, testing control words, and buffering data in transit between the external bus and the SCCM.

- the External Bus Interface (EBI) which interfaces the Mill and the external bus. It encodes parallel commands and data words from the Mill for serial transmission over the bus. It also performs serial to parallel conversion on incoming Manchester encoded data words, making them available to the Mill, and signals their arrival to the Controller. Improperly coded commands and signal/parity er-

rors are indicated to the Fault Handler (FH).

- a DMA interface between the Mill and SCCM provided by the Internal Bus Interface (IBI). Registers in the IBI are used to buffer incoming and outgoing data and DMA requests and acknowledge control logic. The IBI also contains a command decoder which is used to recognize and decode memory-mapped commands from the host SCCM to the BIBB.

- the Controller generates control signals for the other BIBB subelements from internal or external SCCM commands and conditions sampled within the BIBB. It is programmed using a ROM and a Programmed Logic Array (PLA).

The BIBB internal circuits use either duplication and self-checking comparison or error detection codes. The FH combines fault signals from these circuits into a single morphic Internal Fault Indicator. The FH terminates any ongoing transmission on detecting an internal fault. BC faults are signalled to the Core-BB which disables the host SCCM in order to prevent damaged information from being propagated throughout the system. A faulty BA merely disables its own communicating ability. As an SCCM contains several redundant BAS, messages can be rerouted via a different BA.

# 3.2.5 I/O Building Block (IOBB)

The design for the IOBB has not been completed. However, certain typical requirements and functions have been specified.

In order to retain consistency with FTBBC modules all building blocks must provide memory-mapped I/O. Fault tolerant requirements are that:

- the IOBB must check the coding of incoming addresses and data, and utilize duplication or coding checks to verify proper functioning of its internal logic.

- either data errors or internal faults must generate an error indicator to the Core-BB. Error indicators should be morphic to prevent a single point of failure.

- incoming data must be encoded for presentation to the host computer's bus.

One of the more important I/O functions which should be provided by IOBB modules is synchronization of inputs and outputs with the RTI. This:

- ensures synchronism in voting configurations

- decouples I/O timing from detailed instruction timing in the TM

enables software to be changed without altering the I/O timing of unmodified programs

- prevents I/O timing being changed as a result of the use of stolen memory cycles during DMA activity on the IBS which may cause slight variations of processor speed.

- is expected to simplify verification and validation through restricted interaction with the host coupled with synchronous software.

The circuitry for I/O functions is not expected to be complex and fault-detection implementation should be straightforward. Parity checking can be utilized where the data structure is preserved and control functions can be duplicated with morphic comparison.

In order to achieve redundancy in TMs, two or more modules can be cross-strapped, i.e. their inputs and outputs hooked together. Only one module is powered; the others are cold standbys. In this usage short protection should be provided at all output connections to avoid deactivation of all the spares. IOBBs may be used redundantly within an SCCM.

### 3.3 The FTBBC Features Tree

This tree, which is shown in Table 1, is an aid to understanding the extent and placement of the aspects of fault-tolerance which are embodied in the FTBBC design. The tree is a means of representing a hierarchical structure and has been applied, in this case, to the fault-tolerance features distributed within the FTBBC. The level of each feature in the structure is indicated by its level of indentation within the tree. A table of functions has been included to show the purpose of each feature of the module.

The features have been classified into four areas of applicability: detection, containment, analysis, and recovery from faults. The types of fault-tolerant protection found within the FTBBC are enumerated and their location indicated by the right-most column.

A number in parentheses against a feature indicates the fixed number of units contained within the module. Flexibility in the quantity of units, as used for redundant spares for example, is indicated by "(n)".

|     | FEATURES                                                                     |    | FUNCTIONS                                                                                                                                        | F-T TYPES                            |

|-----|------------------------------------------------------------------------------|----|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| sco | CM - Self Checking Computer Module (n)<br>(HLM - High-level Module (n)<br>or |    | - configured as HLM or TM<br>- designated executive or lower HLM,                                                                                | C,R                                  |

| M   | (TM - Terminal Module (n)<br>IIBB - Memory Interface Building Block (1)      |    | - dedicated to a specific subsystem<br>- interfaces redundant                                                                                    |                                      |

|     | (Ham mode or non-Ham mode)                                                   |    | memory chips to internal bus                                                                                                                     | _                                    |

| •   | ABI - Address Bus Interface                                                  |    | <ul> <li>selects appropriate memory module</li> </ul>                                                                                            |                                      |

|     | MAR - Memory Address Register                                                |    | - stores 16-bit memory<br>address                                                                                                                | ~                                    |

|     | APC - Address Parity Checker                                                 |    | - validates address                                                                                                                              | 1bm,6,12m,D                          |

|     | SNC - Soft Name Checker<br>EWAR - Error Word Address Register                |    | - decodes high-order address bits<br>- stores address currently referen-                                                                         | G,11m,12m,D,                         |

|     |                                                                              | •  | ced                                                                                                                                              | 10,R                                 |

|     | ORC - Out-of-Range Command Detector                                          |    | <ul> <li>detects out-of-range commands to<br/>the MIBB</li> </ul>                                                                                | 11,D                                 |

|     | ECS - Error Control Section                                                  | •  | - generates Hamming code check bits,<br>analyzes errors in bus and                                                                               | •                                    |

|     |                                                                              |    | interface circuits                                                                                                                               | 6,D                                  |

| •   | SGC - Syndrome Generators/<br>Checkers                                       |    | <ul> <li>generates Hamming code check bits<br/>and syndromes (in Ham mode only)</li> </ul>                                                       | 2m,6,D                               |

|     | DPCG - Data Parity Checker/<br>Generator (Internal bus)                      | -  | <ul> <li>byte-parity generation and checking</li> </ul>                                                                                          | lam,1bm,6,D                          |

|     | SDA - Single and Double<br>Error Analyzer                                    |    | <ul> <li>analyzes inputs from error coding,<br/>parity checking &amp; all self-testing<br/>circuits</li> </ul>                                   | la,1b,5m,6,D,R,A                     |

|     | ESR/MEI - Error Status Register/<br>Memory Error Interrupts                  |    | <ul> <li>records error conditions from<br/>SDA, gives indication of<br/>correction, prevents write operation,<br/>checks SDA circuits</li> </ul> |                                      |

|     | DBI - Data Bus-Storage Array Interface                                       |    |                                                                                                                                                  | ,.,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

|     | DBM - Data Bit Modules (2)                                                   | ٠. | - 8-bit data storage                                                                                                                             |                                      |

|     | CBM - Check Bit Modules<br>Bit-Plane Interface                               | _  | <ul> <li>stores Hamming code (Ham mode)</li> <li>interfaces 2 parity bits in non-Ham mode</li> </ul>                                             | 2,10D,R                              |

|     | Position Decoder                                                             |    | - on-chip decoding                                                                                                                               | R                                    |

|     | Spare Plane Interface                                                        |    | <ul> <li>interfaces MDR with spare bit plane</li> </ul>                                                                                          | R                                    |

| ٠.  | Bit Interface Module                                                         | •  | interfaces MDR with regular bit plane                                                                                                            | R                                    |

|     | RCS - Replacement Control Section                                            |    | ,                                                                                                                                                |                                      |

|     | Decoders (2)                                                                 |    | - decodes replacement registers                                                                                                                  | R                                    |

|     | Replacement Registers (2)                                                    |    | - used to replace faulty bits in DBM/CBM                                                                                                         | 4.R                                  |

|     | MCS - Memory Control Section                                                 |    | <ul> <li>provides control signals for<br/>implementation of operation and</li> </ul>                                                             |                                      |

|     |                                                                              |    |                                                                                                                                                  | ·                                    |

| FEATURES                               | FUNCTIONS                                                                                             | F-T TYPES     |

|----------------------------------------|-------------------------------------------------------------------------------------------------------|---------------|

|                                        | command algorithms                                                                                    |               |

| CI - Control Interface                 | - SCCM/MIBB handshaking circuits                                                                      | 9,D           |

| CPG - Clock Generator                  | - system synchronization                                                                              | 8,14a,14b     |

| KG - Condition Generators (2)          |                                                                                                       | llm,D         |

| SS - State Sequencers (2)              | - implements steps of operation/                                                                      | 11,0          |

| ,                                      | control algorithms                                                                                    | 8,11,D        |

| CSG - Control Signal Generators (2)    | - generate signals for register & -                                                                   | 0,11,0        |

| the control beginned demonstration (2) | selection networks                                                                                    | llm,D         |

| CSR - Control Signal Comparator        | - reduction of control signals                                                                        |               |

| obn. comparator                        | reduction of control signals                                                                          | 12m,5,D,      |

| Core-BB - Core Building Block          | - detects CPU/bus faults, collects                                                                    | 11 5          |

| core bb core barraring brock           | faults from other BB's, self-                                                                         | 11,D          |

|                                        | disabling                                                                                             |               |

| CPU (i) Master                         |                                                                                                       |               |

| (ii) Check                             | - operates synchronously with                                                                         | 11,D          |

| PCE - Processor Check Element          | redundant processor                                                                                   |               |

| FCE - Flocessor Check Element          | - compares output of processors,                                                                      |               |

|                                        | encodes/checks internal bus parity,                                                                   |               |

| MOUD Manufile Community and All        | decodes commands on internal bus                                                                      |               |

| MCMP - Morphic Comparators (i)         | - compares address output of CPU's                                                                    | 12m,6,D,      |

| (ii)                                   | - compares CPU output with data bus                                                                   | 12m,6,D,      |

| Isolator                               | <ul> <li>allows input data to be passed</li> </ul>                                                    | 15,D          |

|                                        | to Check CPU                                                                                          |               |

| MPC - Morphic Parity Check/            | <ul> <li>check/generate parity (i) on</li> </ul>                                                      |               |

| Generators (i) & (ii)                  | address bus, (ii) on data bus                                                                         | 1bm,6,D       |

| CMD - Command Decoders (2)             | <ul> <li>generates 2 out-of-range addresses</li> </ul>                                                | llm,D         |

| Status Registers (2)                   | - samples fault indicators for access                                                                 |               |

|                                        | by external SCCM                                                                                      | 5,10,D,A,R    |

| BAE - Bus Arbitration Element          | <ul> <li>arbitrates internal DMA requests</li> </ul>                                                  | ,             |

|                                        | from other BB circuits                                                                                | 5,12,D        |

| Priority Resolvers (i) 'true'          | <ul> <li>synchronously compared to detect</li> </ul>                                                  | 11,12m,D      |

| (ii) 'false'                           | faults, arbitrate bus requests                                                                        |               |

| FHE - Fault Handler Element            | - responsible for overall fault                                                                       |               |

|                                        | detection in SCCM & limited                                                                           |               |

| •                                      | recovery action                                                                                       |               |

| Fault Synchronizers (2)                | - examines signals from within SCCM                                                                   | 8,11m         |

|                                        | & sends MFI to RS                                                                                     | 5,D,R         |

| Control Signal Generator               | - generation of internal control                                                                      | 3,5,1         |

| · · · · · · · · · · · · · · · · · · ·  | signals                                                                                               |               |

| RS - Recovery Sequencers (2)           | - disables outputs from SCCM/                                                                         | 5,8,11,12m,13 |

|                                        | resets CPU's                                                                                          | D,C,R         |

| Manual and External Module Control     | - clears fault latches/initializes                                                                    | DICIN .       |

| imidat and precinal module control     | program restart                                                                                       | 0 145 145 D   |

| BIBB - Bus Interface Building Block    |                                                                                                       | 8,14a,14b,R   |

| a) Bus Controller or                   | - programmed as either a or b                                                                         | *             |

| b) Bus Adaptors (3)                    | <ul> <li>transfers information between SCCM's,</li> <li>moves data into/out of SCCM memory</li> </ul> |               |

| ni nga vaghenta (2)                    | - moves unta into/out of SCCM memory                                                                  |               |

| FEATURES                                   | FUNCTIONS                                                                                                                                                        | F-T TYPES                                                  |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| The Mill<br>Memory<br>ALU a)<br>b)         | <ul> <li>responsible for BIBB processing<br/>requirements; sampling incoming<br/>data, DMA address generation,<br/>word counts, testing control words</li> </ul> | la,lb,lc,ld,m,5,l2m<br>lc,8,D,A,R<br>a) la<br>b) 5m,l1,l2m |

| Internal Registers (2)                     | word coding, robbing control words                                                                                                                               | -, o, 22, 22                                               |

| EBI - External Bus Interface A) B)         | - interface between Mill/external bus                                                                                                                            | A) 11,D,<br>B) 12m,D                                       |

| MNT - Manchester/NRZ Translator            | <ul> <li>translates incoming code from<br/>Manchester-NRZ</li> </ul>                                                                                             | 4,8,D                                                      |

| BAC - Buffer and Logic Control BAC Control |                                                                                                                                                                  |                                                            |

| Command Decoder State Control              | <ul><li>detects improperly coded commands</li><li>controls input/output mode</li></ul>                                                                           | 5,D                                                        |

| M Counter                                  | <ul> <li>counts incoming/outgoing data words</li> <li>alerts controller of throughput of</li> </ul>                                                              | 8,D                                                        |

| Controller Alert Logic                     | data words, synchronizes A & B copies                                                                                                                            |                                                            |

| BAC Data Paths                             | ,                                                                                                                                                                | ~                                                          |

| XFR - Transfer Register                    | <ul> <li>serial/parallel conversion</li> </ul>                                                                                                                   | •                                                          |

| CDR - Command Data                         | <ul> <li>single buffer for incoming/</li> </ul>                                                                                                                  |                                                            |

| Register                                   | outgoing words                                                                                                                                                   |                                                            |

| Manchester Encoder                         | - encodes outgoing data                                                                                                                                          | 3                                                          |

| Parity check/generate                      | - checks incoming codes, encodes                                                                                                                                 |                                                            |

| circuit                                    | outgoing words                                                                                                                                                   | la,1b,D                                                    |

| BAC Fault Detection Logic                  | - sends Master Fault Indicator<br>to BIBB FN                                                                                                                     | 5,12,D                                                     |

| IBI - Internal Bus Interface               | - DMA interface between the Mill/                                                                                                                                | 3,12,0                                                     |

| ibi inccinai bas inccitace                 | SCCM memory                                                                                                                                                      | lc,11,R                                                    |

| DC Reg - Direct Command Register           | - contains fault handling circuits                                                                                                                               | 2,D                                                        |

| Address Register                           | - contains toute nanotting citeditis                                                                                                                             | 1b                                                         |

| Data Registers (2)                         | <ul> <li>one each, incoming/outgoing</li> </ul>                                                                                                                  | 1b                                                         |

| DMA Controller (2)                         | - request and acknowledge control logic                                                                                                                          | 1bm,11,R                                                   |

| Command Decoder (2)                        | - detects memory-mapped commands                                                                                                                                 | 1b,11,12,D                                                 |

| Bus Assignment Latch                       | <ul> <li>stores number of external bus being requested</li> </ul>                                                                                                | 1b,D                                                       |

| Fault Handling Circuits                    | - generates single fault indicator                                                                                                                               | 12m,5m,R                                                   |

| CONT - the Controller                      | <ul> <li>generates control signals for BIBB<br/>sub-elements</li> </ul>                                                                                          |                                                            |

| CS - Control Sequencer a) & b)             | <ul> <li>samples circuit conditions within<br/>BIBB outputs: a) data b) parity bits</li> </ul>                                                                   | a) 12m,D<br>b) 1a,D                                        |

| PLA - Programmed Logic Array               |                                                                                                                                                                  | ·                                                          |

| MLC - Microprogram Location Counter        | - generates addresses for CROM                                                                                                                                   | 8,D                                                        |

| Status Register                            | - contains status word for output                                                                                                                                | 1a,5,7,D                                                   |

| ID compare                                 | - compares hard/soft names with                                                                                                                                  | 12                                                         |

|                                            | commands                                                                                                                                                         |                                                            |

| ·                                                                                                                                                |                                                                                                                                 |                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| FEATURES                                                                                                                                         | FUNCTIONS                                                                                                                       | F-T TYPES             |

| Loop counter                                                                                                                                     | <ul> <li>underflow signal sent to condition multiplexor</li> </ul>                                                              | 8,D<br>8,D            |

| TOC1 - time out counter                                                                                                                          | - verifies completion of DMA                                                                                                    | 8,D                   |

| TOC2 - time out counter                                                                                                                          | <ul> <li>detects non-arrival of incoming/out-<br/>going word</li> </ul>                                                         | 8 , D                 |

| CROM - Control ROM                                                                                                                               | <ul> <li>receives addresses from CS, maps<br/>these into control signals<br/>to operate BIBB</li> </ul>                         | la,1b,2,D             |

| FH - Fault Handler                                                                                                                               | <ul> <li>terminates ongoing transmission<br/>when internal BIBB fault detected<br/>stops clock to BIBB, resets pulse</li> </ul> | 5,11,12m,14b<br>D,C,R |

| IBS - Intercommunication Bus System                                                                                                              | - redundant bus system                                                                                                          | 4,R                   |

| 10BB - I/O Building Block (2)                                                                                                                    | - proposed attributes:                                                                                                          | 3,16,1b,5m,11         |

|                                                                                                                                                  |                                                                                                                                 |                       |

| KEY to types of Fault-Tolerance:                                                                                                                 |                                                                                                                                 |                       |

| <ul> <li>a) Parity encoding (double)</li> <li>b) Parity checking "</li> <li>c) Parity encoding (single)</li> <li>d) Parity checking "</li> </ul> |                                                                                                                                 |                       |

| 2. SEC/DED (Hamming) code                                                                                                                        | •                                                                                                                               |                       |

| <ol> <li>Manchester/NRZ coding</li> </ol>                                                                                                        |                                                                                                                                 |                       |

|                                                                                                                                                  |                                                                                                                                 |                       |

Status codes Timers, counters

Redundant spares Fault indications

- Handshaking

- 10. Error information storage for diagnostics

- 11. Duplication

- 12. Comparison/reduction of results

Self-checking logic circuits

- 13. Restart, retry

- 14. Switched circuit a) manual

- b) automatic

- 15. Special circuits to monitor critical elements

- 16. Cross-strapping

- Morphic attributes

- D Detection

- C Containment

- A Analysis

- R Recovery

#### 4. COMPARISONS WITH OTHER FAULT-TOLERANT ON-BOARD COMPUTERS

#### 4.0 General

Comparisons were made among three significant fault-tolerant on-board computing facilities: the UDS/FTBBC, European Space Agency's On-Board Data Handling (OBDH) System (Refs.7-15), and the proposed Advanced Autonomous Spacecraft Computer (AASC) using Intel Corporation's new iAPX 432 computer and its advanced fault-tolerance extensions (the detail of iAPX 432 fault-tolerance is still restricted information).

The purpose of the comparisons is to place the FTBBC in perspective and to determine its strengths and weaknesses as a system. Every effort was taken to make the comparisons as impartial as possible. However, as is always the case with comparisons of objects from different origins, there may be a level of disposition unknown to the authors, in the form of a biased selection of features or topics against which comparisons were made, or the subjective evaluation of scoring by particular system(s) in such comparisons.

A brief outline of the OBDH and AASC follows.

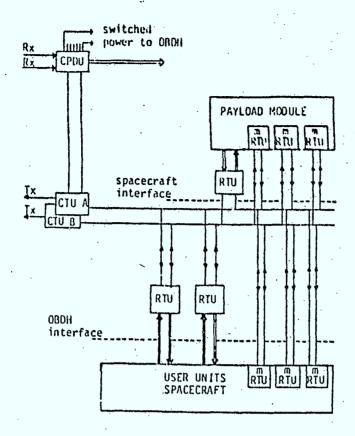

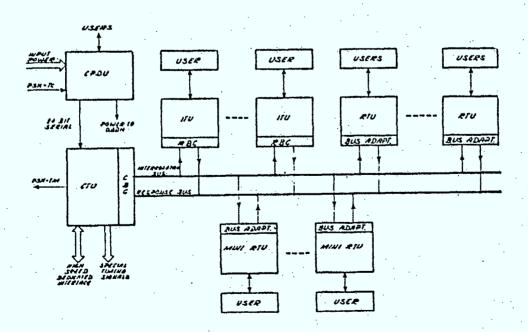

## 4.1 Features of the OBDH

The OBDH is a modular, distributed system which comprises a Central Unit (CTU), a Data Bus, Remote Terminal Units (maximum 31), and a Command and Power Distribution Unit (CPDU) as shown in Figure 4.

The CTU is responsible for timing, internal bus traffic, time-shared access to the external bus, formatting data for telemetry purposes, command and housekeeping handling. Optionally, it can provide user facilities such as data collection from sub-systems, dedicated processing power with access to all OBDH data channels, and user specified pulses. (Ref.16)

The RTUs distribute operational commands and data to other subsystems and acquire data from these subsystems. There are three versions available, for single user, multiple users and multiple users with limited I/O. (Ref.12)

The Data Bus sends commands, data and an operating clock in a continuous, self-clocking, Litton-encoded form to the RTUs via the Interrogation Bus. The Response Bus is used for return messages either to the CTU or another RTU at the CTU's command. Messages are allocated according to predetermined time-slots under CTU control. In-flight programming can be performed via the Programming Bus which is controlled by the Smart-Controller

Fig.4 ESA-OBDH System

Fig. 5 OBDH bus, CPDU, CTU, and RTU

within the CTU.

The CPDU has the following functions; demodulation and bit synchronization of up-link telecommand signals, frame verification, distribution of priority commands and serial load commands, and configuration control of the OBDH subsystem.

CTUs, RTUs and the Data Bus may be duplicated as required to provide a redundant configuration as shown in Figure 5. There is internal redundancy within the RTU and the CPDU. There is no internal redundancy within the CTU, which must rely on a standby spare. (Refs. 8, 12, 16) Software fault detection features include monitoring terminal status, watchdog timers, and detection of abnormal conditions.

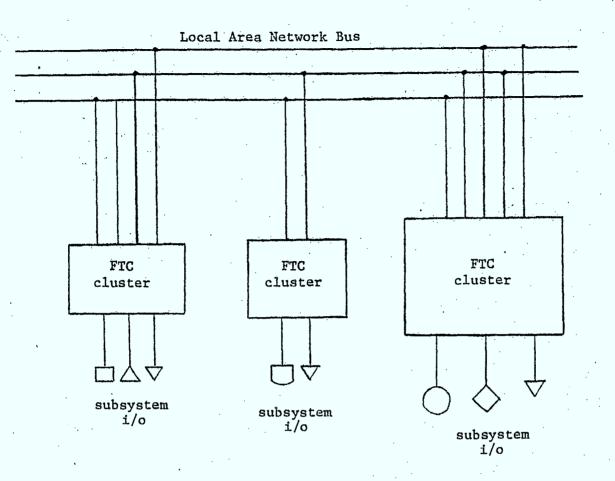

### 4.2 Features of the AASC

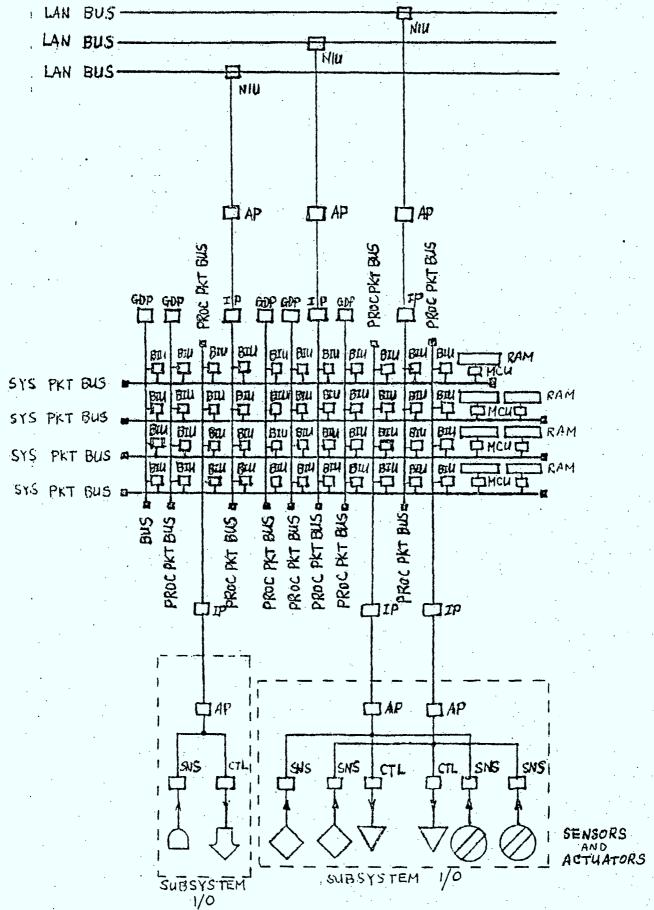

The AASC is an autonomous computer system consisting of clusters of highly fault-tolerant computer complexes distributed along inter-cluster buses. A cluster interfaces the inter-cluster buses at one end and, in general, i/o subsystem(s) at the other, as shown in Figure 6. The inter-cluster bus is very much like a local area network bus.

The hardware redundancy is provided at several levels within the system hierarchy: every element of the system may exist in multiple copies to provide non-dedicated redundancy at hardware level. These include the following: cluster, inter-cluster bus, inter-cluster bus to cluster interface, intra-cluster processor, intra-cluster bus, intra-cluster memory control unit, and local and global memory modules.

The inter-cluster bus is not specified in detail as its design is intended to be independent of available technology. However, a fully distributed architecture is assumed, i.e. no dedicated controllers on the bus and no polling scheme enforced over the bus, multi-drop, and a bandwidth of at least 10MBit per second.

A cluster consists of three sections; the network access section, the FTC complex, and the subsystem support section. An example of a typical cluster is shown in Figure 7.

The network access section establishes contacts between the cluster and the rest of the system. Each of the multi-drop connections to the intercluster bus is achieved by a Network Interface Unit (NIU). The NIU handles at least the first two layers of a multi-layer network protocol. The NIU, in turn, is connected to an Attached Processor (AP) which processes and deals with the issues associated with the network protocol in la-

Figure 6. AASC On-Board System

Fig.7. A 432FTC cluster and spacecraft subsystems

yer 3 and upwards. The other end of an AP is connected to an Interface Processor (IP). This processor is responsible for managing address windows into the FTC complex: it maps address spaces defined in the AP into those in the FTC complex, or vice versa.

The FTC complex is based on Intel's iAPX 432 fault tolercomputer. It houses the upper layers of the local intelligence required for the cluster and provides most of the numerical computing power of the system. It consists of a packet oriented buses flanked by processors and controllers. The System Packet bus handles inter-processor communications, the Processor Packet Bus controls distribution of information between a processor and a number of System Packet Buses. The former is supported jointly by all processors in the complex, while the latter is sponsored by a single processor - either a General Data Processor (GDP) or an Interface Processor (IP). At the intersection of the processor packet buses is a Interface Unit (BIU), which controls information transfer between them. The Memory Control Unit (MCU) attaches module (RAM) to the System Packet Bus. The intelligent memory controller converts logical address spaces implied on the packet bus into physical addresses in the memory module.

The fault-tolerance embedded in the FTC complex hardware surpasses that of any known computer system. The current version of GDP provides a throughput of approximately 0.2 MIPS (Million Instructions Per Second), or the capability of a typical minicomputer. The multiprocessing is performed in a manner completely transparent to the overlaying software structure. The over-all computing power of the cluster is determined as a function mainly of the number of GDPs and system packet buses.

The subsystem support section handles all non-network i/o to and from the FTC complex. It employs the same IP-AP structure as in the Network Access Section. In place of NIUs, however, the AP is connected to a structure that controls an i/o subsystem. The i/o subsystem in this application would be a satellite subsystem such as an AOCS, a temperature control subsystem, an uplink/downlink channel, an on-board power management subsystem, etc. The fault-tolerance within the subsystems will be provided using known FTC techniques, including the use of multiple copies of such a subsystem.

The software will consist of three major module groups: the operating system and its support, the fault-tolerance management software, and the application software. They will be developed as Ada packages and will remain highly configurable to permit intense customization by the application system designer. Together, modules from these three groups will estab-

lish and support hierarchical process structures which may dynamically change shape during their life according to the needs of the system.

The execution of such software will be carried out under the protection of the data structure protection mechanism inherent in the FTC complex hardware. This implies the extension of the enforcement of Ada type-checking concepts into the execution environment (in Standard Ada, this is done only at compile time).

# 4.3 The Basis for Comparison

For the UDS/FTBBC system, a system with a typical UDS configuration that would employ three HLM-1553A bus pairs, each having several TMs is considered. For the OBDH system, a configuration with one CPDU, two CTUs, and two sets of OBDH buses, each supporting several RTUs, is assumed and is illustrated in Figures 4 and 5. For the AASC system a few clusters are envisaged, each containing several GDPs (Ref.17) and IPs, several packet buses and BIUs that inter-connect processors, and memory modules and MCUs. Each cluster is linked together by wide-band local network arrangements similar to Ethernet, as shown in Figures 6 and 7.

While the AASC is only a hypothetical system, its detailed design is well underway and supporting VLSI hardware and software components are the subject of the manufacturer's extensive development efforts. The system is considered here as a reference point in order to evaluate the other two systems against the latest technological developments in the area of fault-tolerant computing.

Comparisons are made on several aspects of these systems including over-all system design, software, hardware, and physical characteristics. In those comparisons which are less open to subjective evaluations, a score is given on the scale of 0 - 9 and a weighted score (0 - 81) is calculated in an attempt to establish the basis for a quantitative comparison. Such weighted scores are tabulated for each system to yield accumulated sums. Note that the weighting of features, individual system scores and hence the weighted scores themselves, may be subjective. The method is nevertheless preferrable to arbitrary, non-exhaustive comparisons.

As the result of the comparison is greatly in favour of the AASC, the authors would emphasize that they have made every effort to remain unbiased. The capabilities of the AASC can be fully demonstrated only after the details of the fault-tolerant extension to iAPX 432 are made public.

Explanatory notes to Table 2 are indicated under "#n", and are appended to the table.

| ·                                                                                    |     |                                                            |      |      |                                                                                     |    |     | •                                       |            |     |    |

|--------------------------------------------------------------------------------------|-----|------------------------------------------------------------|------|------|-------------------------------------------------------------------------------------|----|-----|-----------------------------------------|------------|-----|----|

| FEATURES                                                                             |     | UDS/FTBBC                                                  |      |      | ESA-OBDH                                                                            |    |     | AASC                                    |            |     |    |

| 1                                                                                    | Wt. | •                                                          | Sc.  |      | :                                                                                   | Sc | •   | * • • • • • • • • • • • • • • • • • • • |            | Sc  | •  |

| system hierarchy                                                                     | 8   | sets of (HLM-bus-<br>TM'S)   1                             | 7 !  | 56   | CTU-owned buses                                                                     | 5  | 40  | fully distributed                       | <u>1</u>   | 9   | 72 |

| system-wide synch-<br>ronization                                                     | -   | One HLM as clock master 2.5ms #2                           |      |      | CTU generates bus-<br>clocks at 500KHz                                              | :  | ٠., | tightly synchron-<br>ized buses.        | -          |     |    |

| estimated software/<br>hardware effort<br>ratio for typical<br>application           |     | 30% : 70%                                                  | •    | ٠    | 40% : 60%                                                                           |    |     | 80% : 20%                               |            |     |    |

| multiple mission potential                                                           | 9   | yes                                                        | 9. ( | 81 . | yes                                                                                 | 9  | 81  | yes                                     |            | 9   | 81 |

| mission to mission adaptability                                                      | 9   | expected to be un-<br>stable in larger<br>mission 14       | 5 4  | 45   | limited to small to medium scientific missions 15                                   | б  | 5.4 | highly<br>flexible                      | <b>#</b> 6 | . 9 | 81 |

| subsystem interface: - clarity #7                                                    | 8   | HLM involvement touchy #8                                  | 6    | 48   | clean                                                                               | 9  | 72  | clean                                   |            | 9   | 72 |

| - load, range                                                                        | 7   | up to the capa-<br>city of MIL-STD-<br>1553A bus           | 7    | 49   | multiple RTU's,<br>but limited #9                                                   | 5  | 35  | very wide                               | 10         | 9   | 63 |

| - system transparency #11                                                            | 8   | HLM-sets always<br>visible   12                            | 4    | 32   | CPDU/CTU always visible   113                                                       | 5  | 40  | fully trans-<br>parent                  | 14.        | _   | 72 |

| <pre>system test and validation estimates: - cost of setting up test procedure</pre> | 5   | average #15                                                | 8    | 40   | low-average #16                                                                     | 9  | .45 | major project                           | 117        | 4   | 20 |

| - cost of testing and validation                                                     | 7   | high                                                       | 4    | 28   | average                                                                             | 6. | 42  | low - automated                         | 20         | 9   | 63 |

| - quality of testing and validation                                                  | 9   | average                                                    | 6 5  | 54   | average - high                                                                      | 7  | 63  | very high - auto-                       | -          | 9   | 81 |

| - possibility of software validation                                                 | 8   | difficult                                                  | 4    | 32   | very difficult                                                                      | 3  | 24  |                                         | 22         | 9   | 72 |