CAULLY P 91 C655 C66691 1984

INT-83-65i

(2)

SIMULATION OF THE SBP 9989

MICROPROCESSOR

USING THE CAE TOOL

N.mPc ON A VAX 11/780

SEPTEMBER 1984

Industry Canada Library Quəen

생생는 2 **0 1998**

Industrie Canada Bibliothèque Queen

Prepared By: Max/Streit

Approved By:

Dr. S.A. Mahmoud

Dr. C. Laferriere

COMMUNICATIONS CANADA

. MAY 13

LIBRARY - BIDLIOTHÈQUE

INTELLITECH CANADA LIMITED

352 MacLaren Street Ottawa, Ontario K2P OM6 Government Gouvernment of Canada du Canada

Department of Communications

DOC CONTRACTOR REPORT

DOC-CR-SP -84-023

DEPARTMENT OF COMMUNICATIONS - OTTAWA - CANADA

SPACE PROGRAM

TITLE: Simulation of the SBP 9989 Microprocessor Using the Computer Aided

Engineering Tool N.mPc on a VAX 11/780

AUTHOR(S): Max Streit

INTELLITECH CANADA LIMITED

352 MacLaren Street Ottawa, Ontario

K2P 0M6

ISSUED BY CONTRACTOR AS REPORT NO: INT-83-65i

PREPARED BY: Max Streit

DEPARTMENT OF SUPPLY AND SERVICES CONTRACT NO: OER 83-05075

DOC SCIENTIFIC AUTHORITY: Michel Savoie

COMMUNICATIONS RESEARCH CENTRE

Ottawa, Ontario

CLASSIFICATION: unclassified

This report presents the views of the author(s). Publication of this report does not constitute DOC approval of the reports findings or conclusions. This report is available outside the department by special arrangement.

DATE: SEPTEMBER 1984

#### SUMMARY

This report describes the simulation of the Texas Instrument 9989 microprocessor using the computer aided engineering design development tool N.mPc, developed by Case Western University. The simulation was developed and run on the VAX 11/780 System of Analysis and Simulation Laboratory, Communications Research Centre. simulation includes a hardware description, a command file for programmable assembler and a command file for the programmable linking/loader. A test program is also included. Taken together, these components constitute a software implementation of the SBP 9989 as well as a complete software development system for the SBP 9989 on the VAX 11/780. The architecture of SBP 9989 is discussed, its implementation in N.mPc and a test simulation are described. Comments based on the experience gained during the hardware and software simulation of the SBP 9989 processor are provided. This report describes part of the work under contract OER83-05075 for the Communications Research Centre of the Department of Communications, Government of Canada.

#### FOREWORD

This report describes work involving processor hardware description and simulation using the Computer Aided Engineering (CAE) tool N.mPc which runs on the VAX 11/780 of the Analysis and Simulation Laboratory, CRC. As in all new fields of endeavour, CAE design activities introduce new concepts, hence a new vocabulary. particularly confusing at first is the general tendency of re-using terminology which may have a different meaning in other engineering fields. The purpose of this foreword is, therefore, to provide a common point of reference with regard to the various terms used in the report. This will be achieved by briefly describing the use of the CAE tool N.mPc.

Traditionally, microcomputer based products have been designed in the following fashion:

- The necessary hardware components are built. This usually includes the microcomputer itself which is build using a microprocessor and other peripheral components.

- 2. The software programs are written for the target machine.

- 3. Software and hardware components are integrated and tested.

Very frequently, the software is produced on a host machine using a cross development package (if available).

The development process usually involves many time consuming and costly iterations. A CAE tool such as N.mPc improves the situation by providing a simulation environment which is suitable for testing many design alternatives in a short period of time. The implications of using N.mPc are as follows:

- 1. It is no longer necessary to build the hardware components at the beginning of the design work. Instead, N.mPc provides what amounts to a micro-programmable, register transfer level machine which can be programmed to emulate the target hardware completely. In other words, a designer working on a VAX host for example, could create a VAX executable program which, when run, would emulate the target hardware.

- 2. N.mPc provides a cross development package for the software to be written. The cross development facilities are, however, totally programmable. Programming the cross development facilities of N.mPc is part of the preparatory work which needs be done only once for a given type of hardware.

- 3. Facilities exist in N.mPc to take the user written, application software produced by the cross development package and to incorporate it into the hardware emulation module. The result thus becomes the execution of the application software by the target hardware which in turn is an emulation run by the host computer.

- 4. The rationale for using a tool such as N.mPc is that programmability implies flexibility. Given that a base exists, i.e. most of the hardware emulation is available as well as the cross development package, a designer can alter the design parameters with ease and test various alternatives without committing to any hardware choice.

N.mPc introduces new activities and redefines some traditional concepts. The hardware building stage which is to result in a host executable emulation involves programming the register transfer level machine provided by N.mPc. This programming is done in the ISP

language and is referred to as "implementing" the hardware or preparing the hardware description. Similarly, the programming of the cross-development package involves the preparation of various command files and is considered part of the "implementation" of the target hardware.

A complete N.mPc simulation is the execution of a complete simulation module which includes the hardware emulation and the application programs which have been developed by the cross development package. The fact that the hardware is also simulated may lead to confusion. Therefore, the hardware simulation is usually referred to as emulation whereas the term simulation is reserved for the execution of user programs on the emulated hardware.

This brief foreword, however, falls short of explaining the complexities of a system like N.mPc. Its main purpose was to warn prospective readers that some terms such as simulation, emulation and implementation have a very special meaning in the N.mPc context. The interested reader will find many references to work reporting applications of N.mPc in the field of processor design. A list of references is included at the end of this report.

# TABLE OF CONTENTS

| 1.0 | INTRODUCTION                                                         | 1  |

|-----|----------------------------------------------------------------------|----|

|     | 1.1 Background                                                       | 1  |

|     | 1.2 Simulation - The Modern Approach to Microprocessor System Design | 2  |

|     | 1.3 Structure of the Report                                          | 3  |

| 2.0 | TMS 9900 AND SBP 9989 MICROPROCESSORS                                | 5  |

|     | 2.1 Architecture of the TMS 9900                                     | 5  |

|     | 2.2 Architecture of the SBP 9989                                     | 8  |

| 3.0 | IMPLEMENTATION OF TMS 9900 AND SBP 9989 ON N.mPc                     | 12 |

|     | 3.1 N.mPc File Naming Conventions                                    | 12 |

|     | 3.2 Implementation of the TMS 9900 on N.mPc                          | 14 |

|     | 3.3 Implementation of the SBP 9989 on N.mPc                          | 21 |

| 4.0 | DISCUSSION                                                           | 23 |

|     |                                                                      |    |

|     | REFERENCES                                                           |    |

|     | APPENDIX A: The Hardware Modules                                     |    |

|     | A.1 The SBP9989 Description (t9989.isp)                              |    |

|     | A.2 The Memory Module (timem.isp)                                    |    |

|     | APPENDIX B: The Topology File (test.t)                               |    |

|     | APPENDIX C: The Linking Loader Description (t9989.i)                 |    |

|     | APPENDIX D: The "Meta-Micro" Assembler Description (t9989.m)         |    |

|     | APPENDIX E: A Test Program (test.m; test.1; test.L)                  |    |

|     | ADDENDIY F. A Test Simulation                                        |    |

# TABLE OF FIGURES

| 1.1 | Main Components of the N.mPc System                                              | 4  |

|-----|----------------------------------------------------------------------------------|----|

| 2.1 | Memory Formats of the TMS 9900 (from TI Data manual)                             | 6  |

| 2.2 | The TMS 9900 Workspace Concept (from TI Data manual)                             | 7  |

| 2.3 | TMS 9900 Addressing Modes (from TI Data Manual)                                  | 9  |

| 2.4 | Hardware Block Diagram of the SBP 9989 (from TI Data Manual)                     | 12 |

| 3.1 | File Naming Conventions in the N.mPc System                                      | 13 |

| 3.2 | Workspace Register Indirect Auto-increment Addressing                            | 16 |

| 3.3 | The Debugged "op 5" Procedure                                                    | 17 |

| 3.4 | Different Address Formats (incorrectly) used in the TMS 9900 Library Description | 19 |

| 3.5 | The Debugged "src opr" Procedure                                                 | 20 |

### 1.0 INTRODUCTION

# 1.1 Background

The Texas Instruments TMS 9900 was one of the first 16-bit microprocessors. Introduced in 1977, the TMS 9900 is produced using NMOS technology. Its "memory-to-memory" architecture uses blocks of external memory, designated as "workspace", instead of internal hardware registers; this speeds up context switches associated with interrupts, subroutine calls, etc. The TMS 9900 has 69 instructions and 64K bytes of memory addressed as 32K 16-bit words.

The SBP 9989 is an upgraded military version of the TMS 9900 microprocessor. The SBP9989 differs from its civilian version mainly in the use of Integrated Injection Logic (I<sup>2</sup>L) technology which provides better reliability in extreme temperature conditions and in radiation environments. The instruction set of the SBP 9989 includes all of the TMS 9900 instructions plus four additional instructions which improve performance in numerical applications and multiprocessor configurations.

Because I<sup>2</sup>L based components are inherently radiation hard the SBP 9989 not only conforms to military standards (MIL 883B) but also is space qualified. It is the main processing unit in the "Attitude and Orbit Control System (AOCS) of the European Space Agency (ESA) Large Satellite (LSAT) developed by British Aerospace.

Initially the Ferranti F100L processor had been chosen for the LSAT AOCS. The need for additional processing capacity led to the decision to switch to the SBP 9989 processor for the LSAT program. An independent investigation [2] carried out by Intellitech Canada Limited in the fall of 1983, for the Analysis and Simulation Laboratory of the Communications Research Centre, came to the same conclusions with regard, to the relative performance of the two processors.

# 1.2 Simulation - The Modern Approach To Microcomputer System Design

The traditional approach to microcomputer system design usually tries to build a prototype of the system to be developed. This prototype will consist of a number of hardware boards assembled using wire wrap techniques. This approach makes design changes difficult and becomes costly for the case of large, complex systems (e.g. multiprocessor systems). The designer also faces problems related to the implementation of his hardware design while he is, at the same time, trying to debug the system software. The traditional approach makes it difficult to determine whether the software design or the hardware design are responsible for certain failures and/or inadequacies in the system.

The modern approach attempts first to simulate a design on a host computer using a "computer aided engineering (CAE) tool such as N.mPc. This allows easy development and verification of both hardware and software designs because the simulation is easy to change. Complex systems are handled by using modular simulation software. Once the new design is verified, the hardware is built and the software that previously ran on the simulated hardware can now be reassembled and loaded to be run on the actual hardware.

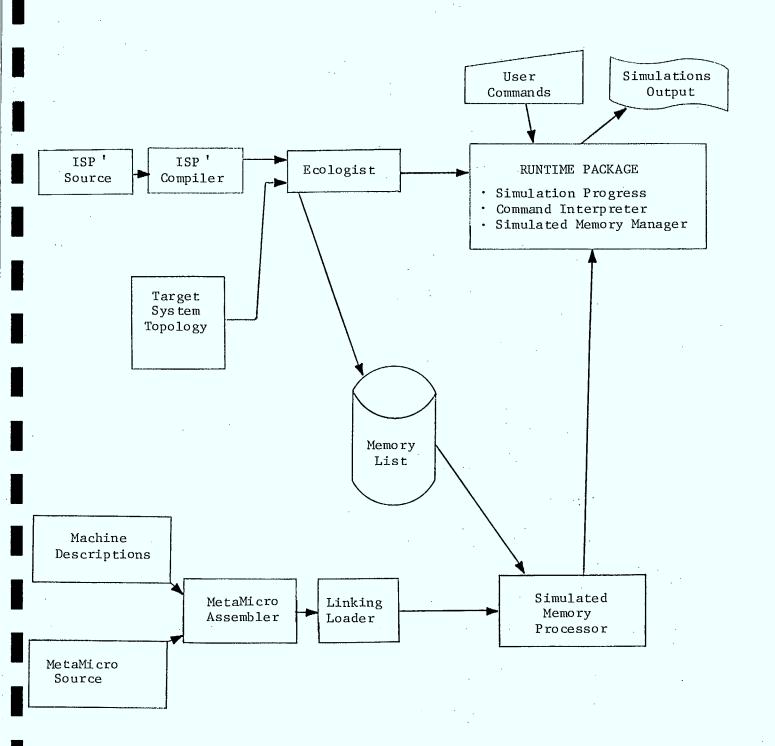

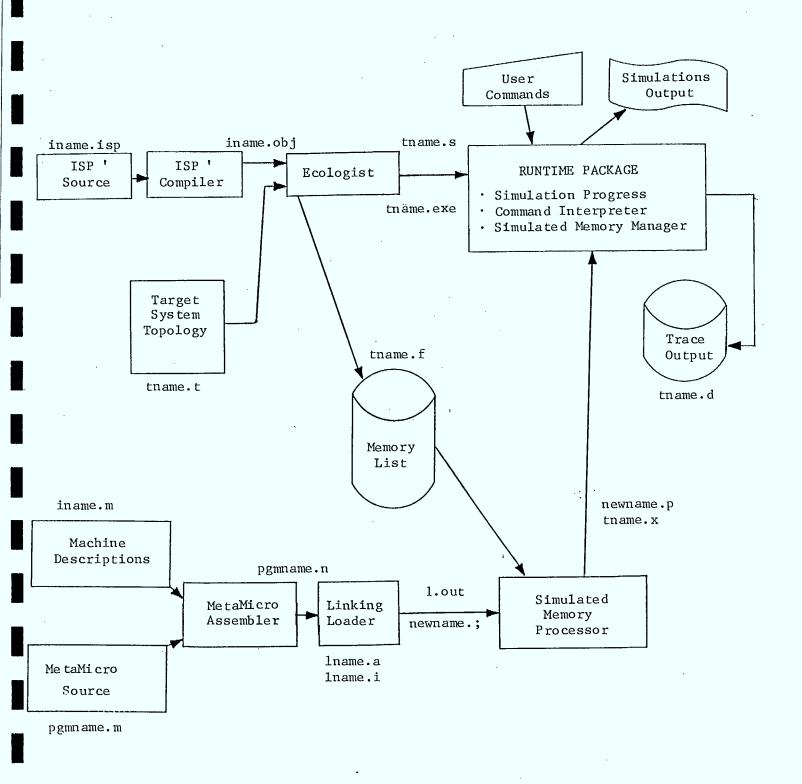

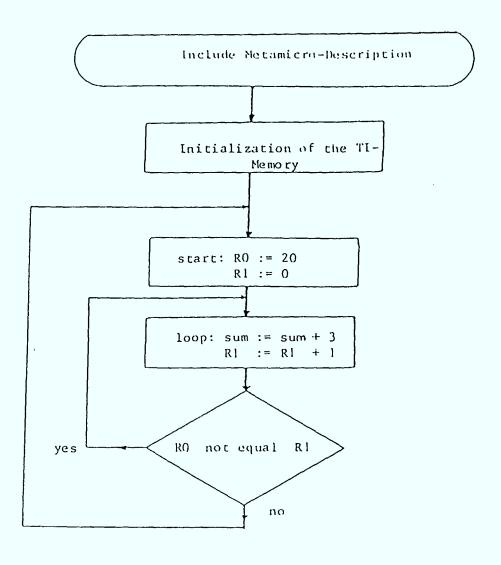

Figure 1.1 shows the main components of N.mPc, a CAE tool capable of simulating complex systems by modelling the hardware at the register transfer level. The user defines the hardware modules of his system (in ISP' source) and their configuration (Topology) and then assembles, links and loads the microprocessor software to be run. The N.mPc system processes all this information and forms a simulation that is easily controlled by the user. Changes and reconfiguration of the hardware modules is a matter of executing a few commands. Fault insertion,

mathematical and graphical post processing of the simulation results are also features of N.mPc. The N.mPc system used for this work ran on a VAX 11/780 under the VMS operating system.

This work started with a description of the TMS 9900 from the N.mPc library. Although this 9900 module did compile correctly, a fair amount of work had to be done to check, verify and debug the 9900 module in order to get a test simulation running properly. As the SBP 9989 constitutes a superset of instructions and signals of the TMS 9900, an SBP 9989 implementation in N.mPc was created by adding the appropriate instructions and signals to the 9900 module. Finally the SBP 9989 module was also checked in a test simulation.

# 1.3 Structure of the Report

Following this introduction, section 2 presents the salient features of TMS 9900 and the SBP 9989 architectures.

Section 3 gives some general information about the CAE tool N.mPc, making references to previous work and the existing N.mPc documentation. The main part of Section 3 outlines the debugging of the TMS 9900 hardware description provided in the N.mPc library, its upgrading to an SBP 9989 module and the addition of the new SBP 9989 instructions to the Metamicro assembler. Section 4 contains a discussion of the results obtained and conclusions reached concerning the 9900 and 9989. The appendices contain listings of an N.mPc test simulation and of various files needed to run it, as well as the protocol of a test simulation.

Figure 1.1 Main Components of the N.mPc System

### 2.0 TMS 9900 AND SBP 9989 MICROPROCESSORS

### 2.1 Architecture of the TMS 9900

The main features of the TMS 9900 are:

- 16 bit Instruction Word

- 64k Bytes of memory (on two pages to be swapped)

- 3.3 MHz speed

- Memory to Memory Architecture (Blocks of external memory designated as "work spaces" replace internal hardware registers)

- 16 general registers

- 16 prioritized interrupts

- DMA and programmed I/O facilities

- N-Channel Silicon-Gate Technology (NMOS)

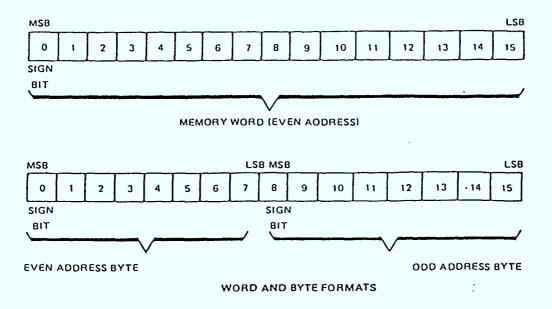

The architecture of the 9900 relies on a 16 bit long memory word, thus consisting of two bytes which may be individually addressed by instructions. This situation is shown in Figure 2.1.

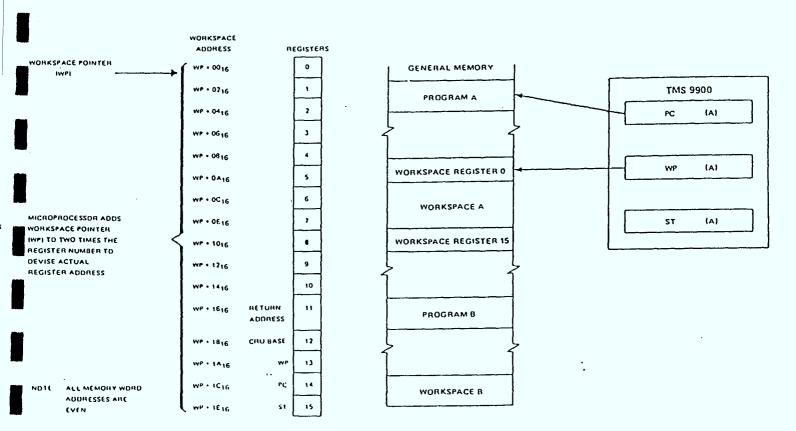

The 32K memory words (16 bits) are always addressed by even addresses while the 64K bytes may have odd or even addresses. The TMS 9900 and the SBP 9989 perform task switching very efficiently. This is due, in part, to their "memory-to-memory" architecture which dispenses with on-chip hardware registers and, instead, uses a contiguous block of 16 memory words. A workspace pointer is always pointing to the first of the 16 workspace registers which replace the processor internal hardware A context switch, generated either by a program request or registers. an interrupt, can be done quickly and easily since it is only a matter of exchanging the workspace pointer, the on-chip program counter and the This feature of the 9900/9989 processors is on-chip status register. depicted in Figure 2.2.

Figure 2.1 Memory Formats of the TMS 9900 (from TI Data Manual)

WORKSPACE POINTER AND REGISTERS

Figure 2.2 The TMS 9900 Workspace Concept (from TI Data Manual)

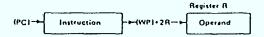

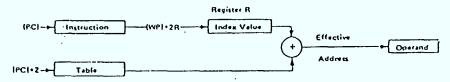

The first 64 words of the TMS 9900 memory space are reserved for interrupt and extended operation trap vectors. The rest of the 32K word general memory area is free for programs and "workspaces". The TMS 9900 can service up to sixteen different interrupts according to their priorities and supports direct memory access via extended operation instructions. A command driven, serial I/O unit (CRU) is also provided. Many of the TMS 9900's 69 instructions have the choice of five main addressing modes for their source and destination operands. Figure 2.3 shows the different ways the 9900's instructions access their operands.

# 2.2 Architecture of the SBP 9989

The SBP 9989 microprocessor is a military standard, upgraded version of the TI9900. The SBP 9989 has all the features of the 9900 plus four more instructions, 4 new signals, higher speed and is implemented in "integrated -injection circuit logic" technology. This "I<sup>2</sup>L" technology gives the 9989 its high reliability, radiation hardness, temperature range and the low power consumption which make it suitable for spacecraft applications. The new features of the SBP 9989 as compared to the 9900 are listed below:

- 1) An instruction set that includes all the 69 instructions of the 9900 plus signed multiply, signed divide, load workspace pointer (LWP) and load stack pointer (LST).

LWP and LST allow the 9989 to load a complete software context from an external source.

- 2) A new output signal on the SBP 9989 called "Memory Map Enable" (MPEN) can be used to double the effective address space. The SBP 9989 can therefore address 128 Kbytes of memory using MPEN in a bank switching mode.

#### WORKSPACE REGISTER ADDRESSING R

Workspace Register R contains the operand

#### WORKSPACE REGISTER INDIRECT ADDRESSING 'R

Workspace Register R contains the address of the operand.

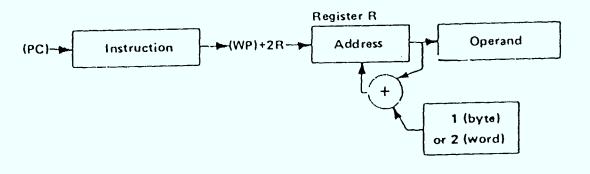

#### WORKSPACE REGISTER INDIRECT AUTO INCREMENT ADDRESSING \*R+

Workspace Register R contains the address of the operand. After acquiring the operand, the contents of workspace register R are incremented.

#### SYMBOLIC (OIRECT) ADDRESSING @ LABEL

The word following the instruction contains the address of the operand.

### INDEXED ADDRESSING @ TABLE (R)

The word following the instruction contains the base address. Workspace register R contains the index value. The sum of the base address and the index value results in the effective address of the operand.

This arrangement is not as convenient as a single linear space of the same size.

- 3) A "Multiprocessor Interlock" (MPILCK) allows coordination of the use of system resources by several processors.

- 4) "Interrupt Acknowledge" (INTACK) allows the 9989 to acknowledge an interrupt signal even at times when it does not have control of the system resources (bus, memory, etc.).

- 5) The "Extended Instruction Processor Present" (XIPP) Input

Signal establishes a protocol for transfer of bus control

between "host" and "slave" processors sharing the same

memory.

- 6) The SBP 9989 may be driven by a 4.4 MHz clock (compared to 3.3 MHz of the 9900) and its instructions use 15-20% less microcycles than its "civilian" version. Texas Instruments claims that the throughput of the 9989 is twice that of the 9900. In view of the previous comments, that claim would appear quite optimistic.

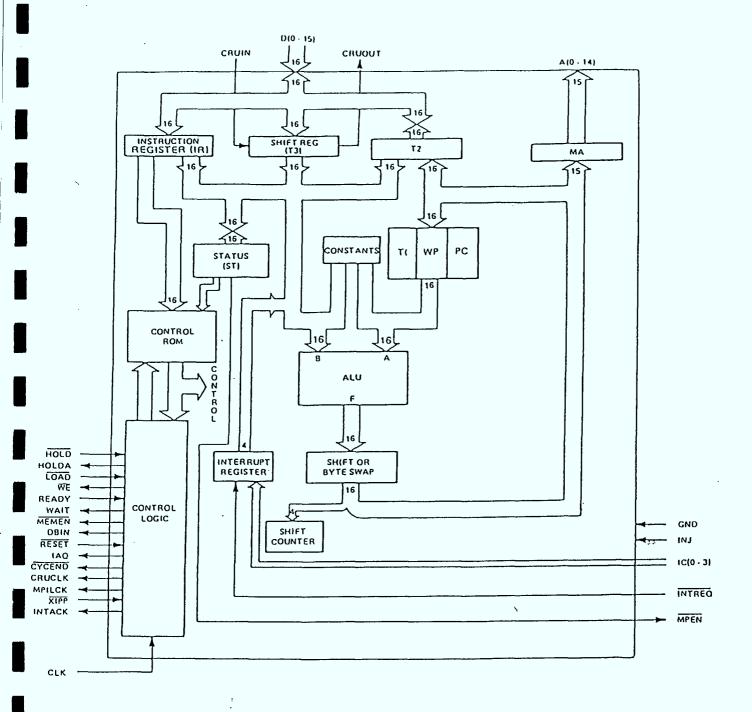

The hardware block diagram in Figure 2.4 presents the MPEN, MPILCK, XIPP and INTACK signals. Memory architecture, addressing modes, I/O facilities, interrupt structure and memory map are identical in the TMS 9900 and SBP 9989 microprocessors. The SBP 9989 is a fully compatible version of the TMS 9900. It is faster, more reliable and better at number crunching and multiprocessing than the TMS 9900.

Figure 2.4 Hardware Block Diagram of the SBP 9989 (from TI Data Manual)

#### 3.0 IMPLEMENTATION OF TMS 9900 AND SBP 9989 ON N.mPc

## 3.1 N.mPc File Naming Conventions

This section will be a brief reminder of the naming conventions in the N.mPc System. The files used in an N.mPc simulation are identified by a name which is chosen by the user and a compulsory suffix. Figure 3.1 shows the N.mPc System and the names of the files produced by the various elements of N.mPc. The following list describes the function of each file.

pgmname.m: A ".m" file is the source input file (= user program) to the metamicro assembler. A successful assembly produces a corresponding "pgmname.n" file.

pgmname.n: The intermediate file produced by the Metamicro assembler. Used by the Linking/Loader Allocator.

Lname.i: The source input to the Linking/Loader Interpreter.

Contains the specification of the address resolution process for a given machine (stored in [.nmpc.softgen.llcf]).

Lname.a: The output of the Linking/Loader Interpreter. This file is used by the Allocator to direct the address resolution process.

1.out The output of the Allocator. Contains a real machine core image, suitable for simulation after processing by the "Simulated Memory Processor".

iname.isp The input of the ISP compiler, contains ISP source code describing a simulated piece of hardware.

<u>iname.obj</u> The output of the ISP compiler, corresponds to the iname.isp source input.

tname.t The topology file, the ecologist will build a program called "tname", which will be the executable simulation.

tname.s A symbol table file created by the ecologist, used by the runtime package. "tname" is the simulation name.

tname.f The memory list file, produced by the ecologist, and used by the simulated memory processor. Contains the names of all memories used in a simulation.

Figure 3.1 File Naming Conventions in the N.mPc System

newname.P A processed file created by "smp". Corresponds to a previous Linking/Loader output file which has been renamed. Used by the simulation program and the Simulated Memory Editor.

The contents of L.out are overwritten by each creation of a simulation. To share a "ready to run" set of files without going through the whole creation process the contents of 1.out have to be saved into another file (e.g. by doing Rename 1.out newname). The new file has to be declared in the topology file.

tname.x Another smp output, containing global symbols from the Meta Micro; one per simulation.

tname.d The simulation data file contains data to be processed by the post processor. This is a new feature of the VAX/VMS version of N.mPc.

tname.exe The executable simulation program.

iname.m The user programmed description of the (meta micro) assembler for the microprocessor being simulated; it has to be stored in the usual N.mPc directory structure (and can be reached by the path [.nmpc.softgen.mmpd]).

The N.mPc system seems quite complicated at first sight but all that is necessary to build a simulation is a hardware description (iname.isp), a topology file (tname.t), an assembler description (iname.m), the linking loader description (Lname.i) and some user program (pgnmname.m). These inputs are processed to form an executable simulation, which is controlled by "user commands". The N.mPc system has been used extensively by Intellitech, at first on PDP-11/UNIX and later on VAX/VMS. Interested readers are referred to the relevant reports [2,3], and the original N.mPc documentation [1, 8-16].

## 3.2 Implementation of the TMS 9900 on N.mPc

The success of an N.mPc simulation depends to a great extent on the quality of the descriptions of the various hardware modules required by the simulation. Ideally, one should be able to use existing hardware descriptions from an N.mPc library and concentrate on the simulation

building aspects.

The starting point for the implementation of the TMS 9900 on N.mPc was an ISP' library description of that microprocessor provided with the N.mPc package. Several bugs, some of them of a subtle nature, existed in the ISP' description and had to be corrected. The following paragraphs describe the nature of some of those bugs and the corrections that were subsequently made.

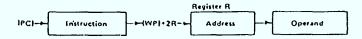

A test program designed to check the correct execution of the add instruction using all the five different addressing modes for source and destination operand showed a malfunction of the autoincrement indirect addressing mode. Instead of acquiring the source operand, the add procedure only took the address of the source operand in the addressing mode depicted in Figure 3.2.

The problem was clearly a logical bug in the corresponding procedure (op\_5) mixing up the destination operand and its address in the case of auto increment addressing. Figure 3.3 shows the procedure "op 5", a part of the TMS 9900 description. The missing "read from memory" operation had to be added not only in the A (=add opcodes) instruction but also in the SZC (set zeroes corresponding; opcode 2) the S(=subtrack, opcode 3), the MOV (=move, opcode 6) and SOC (= set ones corresponding) instructions.

On the third line, only the <u>address</u> of the destination operand is read from a register (rreg) which was specified in the instruction. The reading of the operand from memory (using its address) is omitted. The improved "op 5" procedure now performs correct additions because (the changed) line 3 and (the new) line 4 read the destination operand from memory.

Figure 3.2 Workspace Register Indirect Auto-increment Addressing

```

*/

*/

/* Executes orcode 5 group of instructions.

*/

/* Instructions : A,AB src,dst

*/

/************************

or_5 :=

(

S1 = src_opr(Sn,Smode,Size) . !set first operand

if Dmode eal 3 ! auto increment

D2 = 2*rres(Da,Size) .;

D1 = bus_read(D2,Size)

else

D1 = src_opr(Dn,Dmode,Size) . ! Also dest.addr.,

! so read last

if Dmode eal 2

PC = PC - 2.

D2' = RC(D1,S1,add,Size) . !compute the sum dst_opr(D2,Un,Dmode,Size,se_fl) . !store in dst

0 = (S1<0) eal D1<0>) and (D2<0> nea D1<0>).

!set

delay(2) .

!ALU cycles

if Size eal B

F = parity(D2<oste>)

)

```

Figure 3.3 The Debugged "op 5" Procedure

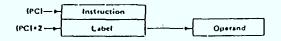

The second major error in the TMS 9900 library description was the reading/writing to/from incorrect addresses in memory. In depth analysis of the problem showed that there was a difference in the address format generated by the "effective address calculation" procedure and the one assumed by the memory read/write procedures. Figure 3.4 shows the difference between these two address formats.

Once aware of this situation, corrective action was taken by changing the address recognition for source and destination operands. The stripping of the "least significant bit" of an address by the bus read/write procedures (assuming that the LSB is always zero) produced wrong addresses as the effective address provided was not in the assumed format.

To put the operand addresses in the appropriate format they are multiplied by two (equivalent to a "shift left" for binary numbers) prior to bus reading /writing of operands. To achieve this, only the address recognition in the "src-opr" and "dst-opr" procedures had to be changed by introducing a factor of two into the address recognition ("eff-addr" becomes "2\* eff-addr"), as it is shown in Figure 3.5. The same problem as above was fixed in a similar fashion for the BWLP instruction. After the changes to the TMS 9900 library descriptions mentioned above, the test program documented in Appendix F began to execute properly.

memory read/write procedures effective address calculation of the TMS 9900 procedure of the TMS 9900 MSB LSB LSB MSB 15 ....14 15 interpreted as: interpreted as: word-address(decimal) word-address(decimal) 0 0 1 2 2 3 6

address format provided by the

address format expected by the

Figure 3.4 Different Address Formats (incorrectly) used in the TMS 9900 Library Description

(memory)

```

/*****************

*/

*/

/* Fetches source operand.

*/

/* Input parameters: register number nibble,

/*

addressing mode pair.

*/

*./

/*

operand size bit.

*/

/* Output parameters: source operand word.

*/

src_opr(rn<nib>,mode<pair>,size<bit>)<word> :=

(

case mode

0 : ! redister

src_opr = rres(rn,size)

1,2,3:/*

indirect resister,

direct address,

indexed,

autoincrement

*/

A2 = 2*eff_addr(rn,mode,size). !set the address

src_opr = bus_read(A2,size)

!read from memory

esac

)

```

Figure 3.5 The Debugged "src opr" Procedure

# 3.3 Implementation of the SBP 9989 on N.mPc

As the SBP 9989 is an upgraded TMS 9900 microprocessor, its implementation on N.mPc involved an upgrading of the TMS 9900 description mentioned in Section 3.2.

In programming design terms, four new instructions and four new signals ("ports") have to be added to the TMS 9900 description to make it an SBP 9989 module.

The added instructions are:

- signed multiply, performed by a procedure named "mpys"

- signed divide, performed by a procedure named "divs"

- load workspace pointer ("LWP") and load status register ("LST") enable the SBP 9989 to capture a complete software context from an external source

Three of the added system features ("ports") serve multiprocessing purposes:

- "multiprocessor interlock" (MPILCK), an output signal used to avoid access contention in resource sharing multiprocessing systems

- "interrupt acknowledge" (INTACK) enables the processor to acknowledge interrupts even while it is not in control of the system resources

- "Extended Instruction Processor Present" (XIPP) is an input signal needed for bus control transfer between the SBP 9989 and a co-processor.

The new output signal "MPEN" can either be manipulated to double the address space to 128 K bytes or be used (with a Memory Mapper) to allow access to 16 megabytes of memory. All these new signals and instructions are found in the listing of the SBP 9989 description in

Appendix A.1. Appendix A.2 contains the listing of the external memory description used with the SBP 9989. Appendices B, C, D contain listings of the topology, linking loader, and metamicro assembler description files needed to build an SBP 9989 simulation. Appendix E shows listings of the program (in different formats) used to test the SBP 9989 description. This test simulation is described in detail in Appendix F.

Following the conversion of the TMS 9900 ISP description into a workable SBP 9989, testing activities began. Instructions from all opcode-groups were executed in short test programs, checking for correct contents of memory and/or registers before and after the execution of the instruction being tested. The initial situation was that a test program (test.m) could not be run because of bugs in the initial 9900 description. Upgrading of the TMS9900 description to an SBP9989 description along with the debugging mentioned above finally resulted in an SBP 9989 simulation on which the test.m program could be run successfully.

At this point it is important to stress that a working description of the SBP 9989 has been obtained. This description coupled with the appropriate meta micro assembler command files enables the N.mPc system to be used as a TMS 9900/SBP9989 development system. N.mPc is truly a programmable microprocessor development system.

#### 4.0 DISCUSSION

The implementation of an SBP 9989 development system on N.mPc has been successfully accomplished and resulted in descriptions of the TMS 9900/SBP 9989 processors in the N.mPc hardware description language (ISP'), a programmable metamicro assembler for both processors and a test simulation.

Major portions of the SBP 9989 such as its decoding loop, its read/write procedures, and a number of its instructions were thoroughly checked, debugged and their functionality proven in actual test simulations. Due to lack of time however, not all the instructions of the SBP 9989 could be checked. In the event of future work with this processor description, further testing would have to be completed by checking the following components of the 9989 ISP description.

- a) the "INTERRUPT" procedure;

- b) the I/O procedures ("CRU CLOCK,""CRU TRANSFER");

- c) the "LOAD", "RESET", "OVERFLOW TRAF", "SHIFT", "MPYS" and "DIVS" procedures;

- d) most of the opcode 0 and opcode 1 instructions.

As in all N.mPc implementation activities, there is an extra benefit resulting from the careful study of the hardware to be implemented. In this case, the benefit is a thorough understanding of the workings of the SBP 9989 microprocessor. Based upon that understanding, the SBP 9989 can be compared with other microprocessors that are likely to be used in space applications. Examples of such processors include the Ferranti FlOO-L and the CMOS version of the Intel 8086.

The Ferranti F100-L is a 16 bit microprocessor implemented in bipolar logic for a high immunity to noise and radiation. This is an essential characteristic of any space qualified microprocessor. The F100-L does suffer, however, from a relative lack of advanced architectural features and powerful instructions. The memory map of the F100-L is also fairly non-standard and its handling of pointers can lead to confusion. The Ferranti F100-L was the subject of earlier work at Intellitech and the interested reader is referred to reference [2].

Recently, Harris announced a CMOS version of the Intel 8086 microprocessor. This new version would be suitable for space qualification and would then open the way for the use of the 8086 in spacecraft applications. The 8086 is a 16 bit microprocessor with a powerful instruction set and is compatible with Intel's family of peripheral device controllers. The 8086 is capable of a high throughput due, in part, to its speed and also to its pipelined bus unit/execution unit architecture. Other co-processors can be incorporated in an 8086 based system easily and they operate concurrently with the 8086. More information can be obtained from the relevant Intel literature and product description.

The SBP 9989 is also a 16 bit processor with a somewhat smaller address space than the 8086 (128 Kbytes vs 1Mbyte). In terms of instruction set, the 9989 fares better than the F100-L but does not offer the same versatility as the 8086. Furthermore, it does not feature a separate bus unit and execution unit architecture as the 8086. Speedwise, however, the 9989, although not as fast as the 8086, outperforms the Ferranti F100-L. This fact is substantiated by the recent switch of processors (i.e. from the F100-L to the 9989) in the British Aerospace L-Sat AOCS design. British Aerospace apparently found that the throughput of the F100-L was not sufficient to handle the load of a Spacecraft Microcomputer Module (SMM).

Having established the 9989 as a better alternative to the F100-L one may wish to compare the 9989 to the 8086. Apart from the fact that those two processors are of a 16 bit design, their respective architectures are quite different. Some of those differences are outlined in the four points below:

The SBP 9989 does not have on-chip general purpose registers. This slows down operations but facilitates task switching. Both the 9989 and the 8086 have flexible interrupt facilities reminiscent of those of the PDP-11. Interrupt service routines can be linked easily and priorities can be assigned with relative ease. (An 8086 would require a 8259 programmable interrupt controller). In the final analysis, the task switching advantage of the 9989 over the 8086 is offset by the latter's greater speed and by the fact that most interrupt service routines only save one or two on-chip registers in any case.

- 2. The Intel 8086 supports a segmented 1 Mbyte address space and a separate 64 Kbyte I/O space. This is vastly superior to the 9989's 128 Kbyte combined address and I/O space. To the 9989 defence, however, it must be added that in typical satellite applications, only a fraction of the 8086 address space would be used. Nevertheless, the large address space is there should modifications and enhancements be required at a later date.

- 3. Both processors provide mechanisms for the smooth integration of co-processors. An arithmetic co-processor is available for the SBP 9989; a wider choice of co-processors exists for the 8086 such as a numeric co-processor (8087), and an I/O co-processor (8089). Those co-processors are not currently space qualified but their usefulness in future spacecraft missions is easy to visualize.

- 4. The number and type of available support chips is much greater for the 8086 processor. This is due in part to the existing support chips for the 8 bit processors from Intel and to the greater popularity that the 8086 has enjoyed commercially.

While the SBP 9989 is a good processor in its own right, it appears that the coming availability of the 8086 in a CMOS version will make the 8086 the preferred choice in future implementations of on-board spacecraft control systems. In addition, software development utilities and packages are far more numerous for the 8086 than for the 9989. This software factor should be weighed very carefully when evaluating a given microprocessor.

It should be clear that due to rapid technology advances better processors are continually emerging. Therein lies the real advantage of using N.mPc in a design environment. Re-designs are easier and new processors can be incorporated and tested with greater ease than with traditional bread-boarding approaches. The development system for the SBP 9989 created using N.mPc is in keeping with that philosophy.

## REFERENCES

- [1] C.W. Rose, F.I. Parke, G.M. Ordy; "N.mPc: A Retrospective" and "The N.2 System" Case Western Reserve University, Cleveland, Ohio, June 1983.

- [2] C. Laferriere, A. Lam; "N.mPc and its Utility for Spacecraft Applications" Report No. INT-83-47/1, Intellitech Canada Limited, January 1983.

- [3] C. Laferriere, W.T. Brown, J.G. Ouimet, S.A. Mahmoud, "The Definition and Specification of an Integrated Set of CAE Tools for Spacecraft Multiprocessor System Design", Report No. INT-82-16, Intellitech Canada Limited, March 1982.

- [4] Texas Instruments Semiconductor Products; Master Selection Guide, 1982.

- [5] TMS 9900 Microprocessor; Data Manual; August 1982.

- [6] SBP 9989 Microprocessor, Data Manual, 1982.

- [7] Texas Instruments; Software Development Handbook; 1981.

- [8] G.M. Ordy, "N.mPc Release 2 Installation", Department of Computer Engineering, Case Western Reserve University, Cleveland, Ohio, November 1980.

- [9] L.R. Rogers and G.M. Ordy, "N.mPc Metamicro User's Manual, version 3.1, Department of Computer engineering, Case Western Reserve University, Cleveland, Ohio, July 1980.

- [10] C.W. Rose et al., "The N.mPc System Description Facility", Procedings of the 16th Design Automation conference (IEEE), pp. 520-528, June 1979.

- [11] F.I. Parke et al., "The N.mPc Runtime Environment", Procedings of the 16th Design Automation Conference, (IEEE), pp. 529-536, June 1979.

- [12] F.I. Parke , "An Introduction to the N.mPc Design Environment", Proceedings of the 16th Design Automation Conference (IEEE), pp. 513-519, June 1979.

- [13] G.M. Ordy, "N.mPc Runtime User's Manual" Dep't of Computer Engineering, Case Western Reserve University, Cleveland, Ohio, Spring 1979.

- [14] G.M. Ordy and F.I. Parke, "An Evaluation of the N.mPc Design System" Proceedings of the 16th Design Automation Conference (IEEE), pp. 537-541, June 1979.

- [15] G.M. Ordy, "N.mPc Ecologist User's Manual", Dep't of Computer Engineering, Case Western Reserve University, Cleveland, Ohio, Spring 1978.

- [16] R. Straubs, "N.mPc ISP' User's Manual", Dep't of Computer Engineering, Case Western Reserve University, Cleveland, Ohio, 1978.

APPENDIX A: The Hardware Modules

A.1 The SBP9989 - Description (t9989.isp)

```

Dec 31 15:52 1983 t9989.isp Page 1

```

```

ૠ

TEXAS

INSTRUMENT

%

જ

%

%

%

SBP-9989

%

%

જ

Version 2.0

%

%

જ

This ISP description is obtained by upgrading

the description for the TMS 9900. It includes

%

ૠ

all port definitions, external memory and bus

ૠ

interface, full DMA and interrupt capabilities.

%

To make read/write-operations of words from/to

memory function src_opr, dst_opr and the BLWP-

%

instruction had to be changed (factor 2 in front

%

%

ૠ

%

of "eff_addr").Proper execution of the auto-in-

%

crement addressing-mode was achieved by correc-

%

%

ting op_2, op_3, op_5, op_6 and op_7.

%

જ

ૠ

જ

Max Streit

%

જ

December 83

%

ૠ

Intellitech Canada Limited

macro

/***********************

*/

/*

*/

/* Symbolic names for register lengths.

*/

/ ********************

0:0 &,

bit =

pair =

0:1 &.

nib =

0:3 &,

byte =

0:7 &,

word = 0:15 \&,

lobyte = 8:15 \&,

addr = 0:14 &,

/*********************

*/

/*

*/

/* Constants for size of operands.

*/

/大

/*********************

W = 0 \&, ! Word

B = 1 \&, ! Byte

/**********************

*/

*/

/* Constants for addressing modes.

*/

/*

```

```

Dec 31 15:52 1983 t9989.isp Page 2

/******************

= 0 &, ! register

ir = 1 &, ! indirect register

da = 2 &, ! direct address

x = 2 \&, ! indexed

/*********************

/+

★/

/* Logic levels to select an option in a procedure.

大/

★/

/**********************

= 0 &, ! operation was a subtraction

add

= 1 &, ! operation was an addition

de_f1 = 0 &, ! deselect changing flags

se_fl = 1 &, ! select changing flags

大/

/* Symbolic names for logic levels.

*/

大/

/*

false = 0 \&,

true = 1 &,

clear = 0 &,

set = 1 \&,

high = 1&,

low = 0

/*************************************

/+

*/

/*

Delay units for clock and timing.

*/

/+

*/

clk = 1&,

pulse = 2\&,

phase = 1&,

/**********************

*/

*/

/* Enforces sequential execution.

/*********************

. = ;next &;

state

/********************************

*/

/* Declaration of registers.

*/

*/

```

/\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

```

! Program Counter

PC(word),

WP(word),

! Workspace Pointer

ST(word)(0x0000), ! STatus register

*/

/★

*/

/* Temporary registers.

*/

/*********************

Al(word), ! Address register 1

A2(word), ! Address register 2

Dl(word), ! Destination register 1

D2(word), ! Destination register 2

Il(word), ! Instruction register 1

I2(word), ! Instruction register 2

XR(word), ! Extra Instr. register for X Remote instr.

Sl(word), ! Source register 1

mbr(word),! Holds word last read from memory.

in_vec(word),! Holds addr. vect. for interrupt routin

Load(bit), ! Flag set on load function

Reset(bit), ! Flag set on reset function

Xipp(bit), ! Flag set on extended processor function

Illop(bit); ! Flag set on illegal opcode fetch

format

*/

*/

/* Instruction register subfields.

*/

/**********************

Opcode = I1(0:2), ! instruction set Opcode

Size

= I1\langle 3 \rangle,

! operand Size

Dmode

= I1\langle 4:5\rangle,

! Destination mode

! Destination register number

= I1\langle 6:9\rangle,

Smode

= I1(10:11), ! Source mode

= Il(12:15), ! Source register number

/*********************

/*

*/

*/

/* Status register subfields.

LGT = ST(0),

! Logical Greater Than

! Arithmatic Greater Than

AGT = ST(1),

EQL = ST(2)

! EOuaL

С

= ST(3),

! Carry

= ST(4),

! Overflow

0

Р

= ST(5),

! Parity

= ST(6),

! X0P

```

```

Dec 31 15:52 1983 t9989.isp Page 4

IM = ST(12:15); ! Interrupt Mask

port

/*********************

/*

/*

Chip pin description

*/

/*

*/

/*********************

! Data and address bus signals

abus<0:14>,

! address bus

dbus(0:15), ! data bus

! Bus control signals

! data bus in signal. high true

dbin,

memen(high), ! memory enable. low true.

we(high),

! write enable. low true

cruclk,

! CRU clock signal from processor

! CRU data in port for serial I/O

cruin,

! CRU data out port for serial I/O

cruout,

! Memory control signals

! low true hold signal ! hold acknowledge. high true

hold(high),

holda(low),

ready,

! ready signal from memory

! wait signal for memory operation

pwait(low),

mpen(high),

! memory map enable output signal. low true

! Timing and control signals

! instruction acquisition signal. high true

iaq,

load(high),

! low true load signal to processor

I reset signal to processor. low true

reset(high),

! multiprocessor interlock output signal

mpilck,

! extended instruction input signal. low true

xipp(high),

! Interrupt control signals

! low true interrupt request signal

intreq(high),

intcode(nib),

! interrupt priority code

! interrupt acknowledge output signal

intack:

/***********************

/*

*/

*/

/*

Reads addressed word from memory

*/

/ ★

Input parameters: 15 bit word address

/*

Output parameters: data word.

*/

/*

```

/ \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

```

Dec 31 15:52 1983 t9989.isp Page 5

M read(address(addr))(word) :=

!buses busy, ie. DMA active

if hold eql low

holda = high;

!processor in hold state

abus = clear; dbus = clear; !make sure buses are clean

!wait until buses become available

while hold eql low delay(clk);

delay(clk);

holda = low

!release from hold

) .

!load the address bus

abus = address(addr);

!data bus in and disable output

dbin = high .

!address bus valid

memen = low;

delay(clk);

!memory not ready

if not ready

.delay(phase);

!processor in wait state because of a

pwait = high;

!not ready condition from memory.

delay(3*phase);

while not ready delay(clk); !wait until memory is ready

delay(2*phase);

pwait = low

)

else delay(phase) .

!read data bus

M read = dbus .

wait(ready:trail)

!clear output signals

dbin = low .

abus = low .

laddress bus idle

memen = high

)

/ *********************************

*/

*/

/*

Writes a word to memory

Input parameters: 15 bit word address,

*/

/ ★

*/

/*

data word

大/

/*********************

M write(data(word),address(addr)) :=

!bus not available

if hold eql low

(

holda = high; !processor in hold state

abus = clear; dbus = clear; !make sure buses are clean

while hold eql low delay(clk); !wait until buses available

delay(c1k);

holda = low

) .

dbus = data;

!load data bus

!load address bus

abus = address;

!enable output

dbin = low .

!address bus valid

memen = low;

```

!write mode

delay(clk);

we = low;

```

Dec 31 15:52 1983 t9989.isp Page 6

if not ready

!memory not ready

delay(phase);

pwait = high;

!processor in wait state

delay(3*phase);

while not ready delay(clk); !until memory becomes ready

delay(2*phase);

pwait = low

else delay(phase)

we = high;

!clean output signals

wait(ready:trail)

abus = low;

dbus = low .

memen = high

!address bus idle

/*********************

*/

/* Handles bus interface to read from memory.

*/

*/

/* Input parameters: address word,

data size bit.

★/

/* Output parameters: data word.

*/

/**********************

bus_read(address(word),size(bit))(word) :=

(

mbr = M_read(address(addr)). !last bit of address is striped

case size

W :

! Word operation

bus_read = mbr(word) !return the word

B :

! Byte operation

case address(15)

0 : ! even address

bus read(byte) = mbr(byte)

!return <0:7> of word

l : ! odd address

bus_read(byte) = mbr(lobyte)

!return (8:15) of word

esac

)

esac

)

/**********************************

/+

*/

*/

/* Handles bus interface to write to memory.

/* Input parameters: data word,

*/ -

```

address word,

**\***/

/\*

```

Dec 31 15:52 1983

t9989.isp Page 7

*/

/*

data size bit.

*/

/*

bus_write(data(word),address(word),size(bit)) :=

case size

W : ! Word operation

M_write(data,address(addr))

!write to memory. Last bit striped

B: ! Byte operation

!check the striped bit

case address(15)

0 : ! even address

mbr(byte) = data(byte). !write only (0:7) of data word

M_write(mbr,address(addr))

!will overwrite <8:15> of word

1 : ! odd address

mbr(lobyte) = data(byte). !write only (8:15) of data word

!will overwrite <0:7> of word

M write(mbr,address(addr))

esac

)

esac

)

*/

*/

/* Reads a register.

*/

/* Input parameters: register number nibble,

data size bit.

*/

/* Output parameter: register value word.

*/

*/

/********************

rreg(rn(nib),size(bit))(word) :=

state mar(word); ! temp reg. for address

mar = WP + (2*(rn ext 8)) . !get address of register

mbr = M_read(mar(addr)) . !read from memory and store temporarily

case size

W:! Word

rreg = mbr

B : ! Byte

rreg(byte) = mbr(byte)

!return only bit <0:7>

```

esac

```

Dec 31 15:52 1983 t9989.isp Page 8

( ) .

/*********************

*/

/* Writes a register.

大/

/* Input parameters: data word,

*/

register number nibble,

*/

/*

data size bit.

*/

/+

/**********************

wreq(data(word),rn(nib),size(bit)) :=

state mar(word); ! temp. reg. for address

mar = WP + (2*(rn ext 8)) . !qet address of reg in memory

case size

W:! Word

M write(data, mar(addr)) !write into memory

)

B : ! Byte

mbr(byte) = data(byte) . !write byte into memory

M_write(mbr,mar(addr))

esac;

)

/*********************

/★

*/

*/

/* Calculates effective address.

*/

/* Effective address is derived depending on the

/* the addressing modes : indirect, direct, indexed

*/

*/

/* and autoincrement.

*/

/* Input parameters: register number nibble,

*/

/★

addressing mode pair,

*/

/★

data size bit.

*/

/* Output parameters: effective address word.

大 /

/********************

eff_addr(rn(nib),mode(pair),size(bit))(word) :=

delay(clk) .

!addressing modes

case mode

1 : ! indirect register

eff_addr = rreg(rn,W) !rn contains the address

2 : ! direct address, indexed

!get address pointed by PC

Al = bus_read(PC,W) .

```

!increment PC

!indexed registers

PC = PC + 2.

case rn

```

Dec 31 15:52 1983 t9989.isp Page 9

!zero means direct address

eff_addr = Al

default: !any register can be used as index

eff_addr = rreg(rn,W) + Al.

delay(clk)

esac

)

3 : ! autoincrement

Al = rreg(rn,W).

!register contains the address

eff addr = Al.

Ireturn the address

delay(clk) .

A1 = size = >

!increment by one for byte operation

A1 + 1

else

A1 + 2.

!by two for word operation.

wreq(Al,rn,W)

!restore the new value of register

esac

)

/***********************

*/

/* Fetches source operand.

*/

*/

/* Input parameters: register number nibble,

/*

addressing mode pair,

*/

/ 大

*/

operand size bit.

/* Output parameters: source operand word.

*/

*/

/**********************

src_opr(rn(nib),mode(pair),size(bit))(word) :=

case mode

0

: ! register

src_opr = rreg(rn,size)

)

1,2,3:/*

indirect register,

direct address,

indexed,

autoincrement

*/

A2 = 2*eff_addr(rn,mode,size). !get the address

src_opr = bus_read(A2,size)

!read from memory

)

esac

```

)

```

Dec 31 15:52 1983 t9989.isp Page 10

```

```

/***********************

/* Changes LGT, AGT and EQL flags.

*/

*/

/* Input parameters: data word,

data size bit.

*/

/*

/ <del>*</del> .

*/

/*********************

LAE(data(word), size(bit)) :=

case size

W : ! Word

!ST(0)

LGT = data(word) neq 0 .

AGT = (data(0) eql 0) and (data(word) neq 0).

!ST(1)

EQL = data(word) eql 0 .

!ST(2)

B: ! Byte

!ST<0>

LGT = data(byte) neq 0.

AGT = (data(0) eql 0) and (data(byte) neq 0).

!ST(1)

EQL = data(byte) eql 0 .

esac

)

/********************

*/

/*

/* Stores destination operand. Optionally changes

*/

*/

/* LGT,AGT and EQL flags.

*/

/* Input parameters: destination operand word,

*/

register number nibble,

*/

/*

addressing mode pair,

*/

/ +

operand size bit,

flag changing selection bit.

*/

/+

*/·

/*********************

dst_opr(data(word),rn(nib),mode(pair),

size(bit),fl_chang(bit)) :=

(

if fl_chang eql se_fl

LAE(data, size)

) .

case mode

0

: ! register

wreg(data,rn,size) .

1,2,3 : /* indirect register,

direct address,

indexed.

autoincrement

*/

(

```

```

Dec 31 15:52 1983

t9989.isp Page 11

A2 = 2 \times eff \ addr(rn, mode, size).

bus_write(data,A2,size)

esac;

)

/*********************

*/

/* Fetches second instruction word.

*/

/*********************

fetch_2 :=

(

I2 = bus_{read(PC,W)}.

PC = PC + 2

/***********************

*/

/* Determines truth of a condition code.

*/

/* Input parameters: condition code nibble.

/* Output parameters: condition code true/false bit. */

/*************************************

condi_code(rn(nib))(bit) :=

condi_code = case rn

: true

0

: (not AGT) and (not EQL)

: (not LGT) or (EQL)

3

: EQL

: (LGT) or (EQL)

4

5

: AGT

6

: not EOL

7

: not C

8

: C

: not 0

9

10 : (not LGT) and (not EQL)

11: (LGT) and (not EQL)

12 : P

esac

)

/********************

*/

/*

*/

/* Gets Result of an operation and changes C flag.

*/

/* Handles two operation : add & sub.

*/

/* Input parameters: operandl word,

*/

/+

operand2 word,

*/

/*

add/sub mode selection bit.

/* Output parameter: result word.

*/

```

```

Dec 31 15:52 1983 t9989.isp Page 12

RC(opl(word),op2(word),operation(bit),

size(bit))(word) :=

state 0P1<0:16>,

OP2<0:16>,

RESULT(0:16);

OP1\langle 0:16\rangle = op1\langle 0:15\rangle ext 17.

0P2(0:16) = op2(0:15) ext 17.

case operation

sub : ! subtraction

case size

B:! Byte

RESULT(0:8) = OP1(0:8) - OP2(0:8)

)

W:! Word

RESULT\langle 0:16 \rangle = OP1\langle 0:16 \rangle - OP2\langle 0:16 \rangle

esac

)

add: ! addition

case size

B: ! Byte

RESULT\langle 0:8 \rangle = OP1 \langle 0:8 \rangle + OP2 \langle 0:8 \rangle

)

W:! Word

RESULT\langle 0:16 \rangle = OP1\langle 0:16 \rangle + OP2\langle 0:16 \rangle

)

esac

)

esac .

RC = RESULT(1:16).

C = RESULT(0)

/ * *********************************

*/

/*

Does a context switch by fetching new WP and PC

*/

while saving the present WP, PC, and status (ST)

/大

*/

in the new workspace.

*/

/*

Input parameters: Address for context switch

*/

/大

/*********************

context_switch(address(word)) :=

!ALU cycles

delay(5).

!store temporarily

D1 = WP ; S1 = PC ; D2 = ST .

lassign new values

WP = bus_read(address,W) .

```

```

Dec 31 15:52 1983 t9989.isp Page 13

PC = bus read(address+2,W).

wreg(D1,13,W) .

!store in memory

wreg(S1,14,W).

wreg(D2,15,W).

/***********************

*/

/*

*/

/*

Executes the context switch on a load signal

大/

by loading WP with vector FFFC and PC with

FFFE.Also sets interrupt mask in ST to zero,

*/

/*

*/

clears status bit 7 to 11

*/

/*

and clears the load signal flag(Load).

*/

LOAD :=

(

!ALU cycles

delay(5).

!disable interrupt before context switch

intack=set .

context switch(0xfffc) .

intack=low .

!enable

IM = 0 .

!4 bit interrupt mask

ST\langle 7:11\rangle = 0.

mpen = not ST(8).

!reset load indicator

Load = clear;

)

/************************

大 /

/*

*/

/+

Executes reset signal context switch using

*/

vectors 0000 for WP and 0002 for PC

/*

Interrupt mask in ST set to zero. The reset

*/

/*

*/

/⊁

signal flag(Reset) is also cleared.

*/

/**********************

RESET :=

(

!ALU cycles

delay(5).

!disable interrupt

intack = set .

context_switch(0x0000) .

!enable

intack = low .

ST=0.

!clear interrupt mask

mpen = not ST(8).

!clear reset indicator

Reset = clear

/*********************

*/

/*

*/

Executes overflow trap context switch using

/*

*/

/*

vectors 0008 for WP and 000a.

*/

Interrupt mask in ST set to one.

/*

```

**\***/

/+

ST<7:11> is also cleared.

```

Dec 31 15:52 1983 t9989.isp Page 14

14

*/

/************************

OVERFLOW_TRAP :=

(

!enable interrupt

intack=set .

context_switch(0x0008)

intack=low .

!disable interrupt

IM=1.

!set interrupt mask to 1

ST(7:11)=0.

mpen=not ST(8)

)

/*

*/

/*

*/

This is the context switch at the start of

/★

interrupt service by the processor. The service

*/

火/

/★

routine vectors are calculated using the value

of the interrupt code at the intcode port.

*/

/★

/★

火/

INTERRUPT :=

in vec = (4 * (intcode ext 16)).

intack=set .

context_switch(in_vec) .

intack = low .

ST(7:11)=0.

mpen=not ST(8) .

if intcode eql 0

IM = 0

else

!set interrupt mask

IM = intcode - 1

)

/⊁

*/

/大

Provides clock pulses from processor for all

*/

/+

★/

required CRU operations and for user defined

/大

instructions like CKON, CKOFF, LREX etc

*/

/*

*/

Clock pulse output is from cruclk port

*/

/**********************

CRU_CLOCK :=

delay(clk) .

cruclk = high .

delay(pulse) .

cruclk = low .

delay(clk-pulse)

```

```

Dec 31 15:52 1983 t9989.isp Page 15

```

```

/*

/*

*/

Transfers one bit of data from processor

/*

through cruout line for serial transfer

*/

/⊁

of data. Input parameters: Register with,

*/

/ ★

*/

bit count

/ <del>k</del>

shift start loc.

★/

/*

Data assumed to be in register Dl

*/

/*

*/

/*******************

cru_transfer(bicnt reg(nib),start(nib)) :=

do

memen = high;

if (start ext 8) eql 7 ! byte transfer

cruout = D1<7>

)

else

! word transfer

cruout = D1(15)

)

CRU CLOCK .

bicnt_reg = bicnt_reg - 1;

delay(clk)

if bicnt_reg neq 0

D1 = D1 /: logical 1;

abus = abus + 1

until (bicnt_reg eql 0) .

cruout = low

*/

★/

/*

Procedure to perform shift operations of

*/

/+

processor.

*/

Input parameters: Data to be shifted must

be in register D1.

*/

/*

*/

Register with shift cnt.

/ ★

Shift function code.

*/

*/

/************************

SHIFT(count_reg(nib),functn(pair)) :=

case functn

```

/\*

```

0:

! SRA src, count

(

do

C = D1\langle 15 \rangle.

Dl = Dl /: arith l.

count_reg = count_reg - 1

until (count_reg eql 0) .

dst_opr(D1,Sn,r,W,se_f1)

1: ! SRL src, count

do

C = D1\langle 15 \rangle.

Dl = Dl /: logical l.

count_reg = count_reg - 1 .

until (count_reg eq1 0) .

dst_opr(D1,Sn,r,W,se_f1)

! SLA src, count

do

C = D1(0).

D1 = D1 *: arith 1 .

count_reg = count_reg - 1

until (count_reg eql 0) .

dst_opr(D1,Sn,r,W,se_f1)

3:

! SRC src,count

if count_reg eql 0

D2 = D1 /: rotate 16

else

D2 = D1 /: rotate (count_reg ext 8) .

C = D1(0)

dst_opr(D2,Sn,r,W,se_f1)

)

esac .

!ALU cycles

delay(3).

/**********************

*/

*/

/* Signed multiplication of two 16 bit integers

*/

req 0.1 = req 0 * S1

```

```

Dec 31 15:52 1983 t9989.isp Page 17

/***********************

mpys :=

(

state temp32\langle 0:31 \rangle, temp16\langle 0:15 \rangle;

Sl= src opr(Sn, Smode, W) .

templ6=rreg(0,W) .

temp32 = S1 * temp16.

!reg 0 contains MSD

wreg(temp32(0:15), 0 , W ) .

!reg l contains LSD

wreg(temp32\langle 16:31 \rangle, 1, W).

if temp32 eq1 0 ST\langle 2 \rangle=set.

if temp32 gtr 0 ST(1)=set .

if temp32 neq 0 ST\langle 0 \rangle = set.

!ALU cycles

delay(23).

)

/********************

*/

/* Signed division of two integers

*/

Dividen is in reg 0,1 and is 32 bits

/*

1*

Divisor is in any of the reg, 16 bits

*/

*/

/*

quotient is stored in reg 0

*/

/*

remainder is stored in reg 1

divs :=

(

state temp32(0:31), temp16(0:15);

S1 = src_opr(Sn, Smode, W) . !get the divisor

temp32\langle 0:15\rangle = rreg(0,W). !reg 0 contains MSD of dividend temp32\langle 16:31\rangle = rreg(1,W). !reg 1 contains LSD of dividend

temp32\langle 16:31 \rangle = rreg(1,W).

if (\text{temp32}\langle 0 \rangle \text{ neq S1}\langle 0 \rangle) and (\text{abs }(\text{S1} \star 32767) \cdot \text{leq temp32})

ST(4) = set.

if Sl eql 0

(

ST(4) = set.

!ALU cycles

delay(6).

) .

if ST(4) eql 0

(

templ6=temp32/S1.

!Quotient

wreg(templ6,0,W) .

if temp16 eq1 0 ST(2)=set.

if templ6 gtr 0 ST(1)=set .

if templ6 neq 0 ST(0)=set .

temp16 = temp32 \mod S1.

wreg(templ6, 1, W) .

!remiander

IALU cycles

delay(23).

)

```

)

```

/***********************

大/

*/

/* Executes opcode 0 group of instructions.

*/

/* Instructions : LI r, const

BLWP src

AI r, const

В

*/

/*

src

/*

X

src

*/

ANDI r, const

/+

CLR

*/

src

ORI r, const

/*

NEG

大/

CI r, const

src

*/

/*

STWP r

INV

src

STST r

*/

/大

INC

src

INCT src

大/

/*

LWPI const

LIMI const

DEC

大/

/*

src

DECT src

*/

/*

IDLE

BL

*/

/大

src

RSET

大/

/ +

RTWP

SWPB src

*/

/*

CKON

SETO src

*/

ABS

/*

CKOF

src

/ 大

LREX

TB

disp

★/

*/

/ \

SBO disp

SBZ

disp

*/

Static and dynamic shifts:

/大

*/

/*

src, count

SLA

src, count

SRA

*/

/ *

SRC

src, count

SRL

src, count

All Jump instructions

*/

/ 大

/+

大/

/***********************

op_0 :=

state cnt(0:3); ! counter for shift count

case Size

0:

case Dmode

0:

(

case I1<7:10>

: ! LI r, const

fetch 2.

dst_opr(I2,Sn,r,W,se_fl).

!ALU cycles

delay(3).

)

1 : ! AI r, const

fetch_2 .

D1 = src\_opr(Sn,r,W).

D2 = RC(D1, I2, add, W).

0 = (D1(0) \text{ eql } I2(0)) and

(D2\langle 0 \rangle \text{ neq } D1\langle 0 \rangle);

!ALU cycles

delay(3).

dst_opr(D2,Sn,r,W,se_f1)

)

: ! ANDI r, const

```

```

Dec 31 15:52 1983 t9989.isp Page 19

fetch_2 .

Dl = src\_opr(Sn,r,W).

D2 = D1 and I2.

IALU cycles

delay(3)

dst_opr(D2,Sn,r,W,se_f1)

:! ORI r,const

3

fetch_2.

Dl = src_opr(Sn,r,W).

D2 = D1 or I2.

!ALU cycles

delay(3).

dst_opr(D2,Sn,r,W,se_f1)

)

LWP r

: ! CI r,const

LST r

case Il(6)

! CI r, const

0:

fetch_2 .

Dl = src_opr(Sn,r,W).

D2 = D1 - I2.

!ALU cycles

delay(3).

LGT = ((D1\langle 0\rangle eq1 1) and (I2\langle 0\rangle eq1 0)) or

((D1\langle 0 \rangle \text{ eql } 12\langle 0 \rangle) \text{ and } (D2\langle 0 \rangle \text{ eql } 1)).

AGT = ((D1\langle 0 \rangle eq1 0) \text{ and } (I2\langle 0 \rangle eq1 1)) \text{ or }

((D1\langle 0 \rangle \text{ eql } 12\langle 0 \rangle) \text{ and } (D2\langle 0 \rangle \text{ eql } 1)).

EQL = (D2 eql 0)

1:

! LST r and LWP r

case Il(ll)

0 : ! LST r

ST = rreg(Sn,W).

mpen=not ST(8) .

!ALU cycles

delay(3).

)

1:

! LWP r

!ALU cycles

delay(3).

WP = rreg(Sn,W)

esac

)

esac

)

: ! STWP r

!ALU cycles

delay(2).

dst_opr(WP,Sn,r,W,de_fl)

: ! STST r

!ALU cycles

delay(2).

```

dst\_opr(ST,Sn,r,W,de\_fl)

```

7

: ! LWPI

fetch_2 .

delay(4).

!ALU cycles

WP = I2

: ! LIMI

fetch_2 .

delay(4).

!ALU cycles

IM = I2\langle 12:15\rangle

10 : ! IDLE

abus(0:2) = 2.

!ALU cycles

delay(3).

CRU_CLOCK

11 : ! RSET

IM = 0;

abus(0:2) = 3.

CRU CLOCK

12: ! RTWP and DIVS

case Il(6)

0:

(

divs

1 : ! RTWP

ST = src_opr(15,r,W).

mpen=not ST(8) .

!ALU cycles

delay(4).

PC = src_opr(14,r,W).

WP = src\_opr(13,r,W)

)

esac

13 : ! CKON and DIVS

case Il(6)

0:

divs

1:

abus(0:2) = 5.

!ALU cycles

delay(3).

CRU CLOCK

)

esac ·

```

```

Dec 31 15:52 1983 t9989.isp Page 21

14 : ! CKOF and MPYS

case Il(6)

0:

(

mpys

)

1:

abus(0:2) = 6.

!ALU cycles

delay(3).

CRU_CLOCK

esac

15 : ! LREX and MPYS

case Il(6)

0:

(

mpys

1:

abus(0:2) = 7.

delay(3).

!ALU cycles

CRU_CLOCK

esac

)

esac

)

1:

(

case Dn

0 : ! BLWP src

A2 = 2 * eff_addr(Sn,Smode,W).

!ALU cycles

delay(6).

context_switch(A2)

: ! B src

if Smode eql 0 ! register addressing

PC = WP + (2 * (Sn ext 8))

PC = 2 * eff_addr(Sn,Smode,W);

!ALU cycles

delay(3).

2 : ! X src

XR = src\_opr(Sn, Smode, W).

I1 = XR ; XR = I1 .

!ALU cycles

delay(1).

```

```

: ! CLR src

3

!ALU cycles

delay(2).

dst_opr(0,Sn,Smode,W,de_fl)

: ! NEG src

D1 = src_opr(Sn,Smode,W) .

D2 = RC(0,D1,sub,W)

dst_opr(D2,Sn,Smode,W,se_fl) .

!ALU cycles

delay(3).

0 = (D2 eql 0x8000)

: ! INV src

D2 = src\_opr(Sn, Smode, W).

!ALU cycles

delay(2)

dst_opr(not D2,Sn,Smode,W,se_f1)

: ! INC src

Dl = src_opr(Sn,Smode,W) .

D2 = RC(D1,1,add,W)

dst_opr(D2,Sn,Smode,W,se_fl) .

!ALU cycles

delay(2)

0 = (D1\langle 0 \rangle \text{ eql } 0) \text{ and } (D2\langle 0 \rangle \text{ eql } 1)

7 : ! INCT src

Dl = src_opr(Sn,Smode,W) .

D2 = RC(D1, 2, add, W)

dst opr(D2,Sn,Smode,W,se_fl) .

!ALU cycles

delay(2).

0 = (D1\langle 0 \rangle \text{ eql } 0) \text{ and } (D2\langle 0 \rangle \text{ eql } 1)

: ! DEC src

D1 = src_opr(Sn,Smode,W) .

D2 = RC(D1,1,sub,W)

dst_opr(D2,Sn,Smode,W,se_f1) .

!ALU cycles

delay(2)

0 = (D1\langle 0 \rangle \text{ eql } 1) \text{ and } (D2\langle 0 \rangle \text{ eql } 0)

: ! DECT src

Dl = src_opr(Sn,Smode,W) .

D2 = RC(D2, 2, sub, W)

dst_opr(D2,Sn,Smode,W,se_f1)

!ALU cycles

delay(2)

0 = (D1\langle 0 \rangle \text{ eql } 1) \text{ and } (D2\langle 0 \rangle \text{ eql } 0)

10 : ! BL src

dst_opr(PC,ll,r,W,de_fl) .

if Smode eql 0 ! register addressing

PC = WP + (2 * (Sn ext 8))

```

```

Dec 31 15:52 1983 t9989.isp Page 23

PC = eff_addr(Sn,Smode,W) ;

!ALU cycles

delay(3).

11 : ! SWPB src.

D1 = src_opr(Sn,Smode,W) .

D2\langle 0:7\rangle = D1\langle 8:15\rangle.

D2\langle 7:15\rangle = D1\langle 0:7\rangle.

IALU cycles

delay(2).

dst_opr(D2,Sn,Smode,W,de_f1)

12 : ! SETO src

!ALU cycles

delay(2).

dst_opr(0xffff,Sn,Smode,W,de_fl)

13 : ! ABS src

mpilck= set .

D1 = src opr(Sn, Smode, W).

D2 = case D1(0)

0 : RC(0,D1,add,W)

1 : RC(0,D1,sub,W)

esac .

dst_opr(D2,Sn,Smode,W,de_f1) .

LGT = (Dl neq 0)

AGT = (D1(0) eq1 0) and (D1 neq 0).

EQL = (Dl eql 0).

mpilck = low .

0 = (D1 \text{ eql } 0x8000);

!ALU cycles

if D1(0) eql 1 delay(4)

else delay(3);

esac

)

2:

case I1(8:11)

: ! dynamic shifts

0

S1 = rreg(0,W).

cnt = S1\langle 12:15\rangle.

D1 = src\_opr(Sn,r,W).

!ALU cycles

delay(3).

SHIFT(cnt, I1(6:7))

default : ! static shifts

cnt = I1\langle 8:11\rangle.

D1 = src_opr(Sn,r,W).

SHIFT(cnt, I1(6:7))

```

esac

```

Dec 31 15:52 1983 t9989.isp Page 24

)

esac

)

1:

case Il(4:7)

: ! SBO disp

13

Dl = rreg(12,W).

D2\langle 0:2\rangle = 0;

D2\langle 3:14\rangle = D1\langle 3:14\rangle + I1\langle 8:15\rangle.

cruout = high; memen = high;

abus = D2\langle addr \rangle.

CRU CLOCK;

abus = low;

!ALU cycles

delay(3).

cruout = low

14

: ! SBZ disp

Dl = rreg(12,W).

D2\langle 0:2\rangle = 0;

D2\langle 3:14\rangle = D1\langle 3:14\rangle + I1\langle 8:15\rangle.

cruout = low; memen = high;

abus = D2\langle addr \rangle.

CRU_CLOCK;

abus = low;

delay(3).

!ALU cycles

15

: ! TB disp

Dl = rreg(12,W).

D2\langle 0:2\rangle = 0;

D2\langle 3:14\rangle = D1\langle 3:14\rangle + I1\langle 8:15\rangle.

memen = high;

abus = D2\langle addr \rangle.

delay(clk + (3*phase));

ST(2) = cruin.

!ALU cycles

delay(3).

abus = low

default : ! Jcond disp

if condi code(Il(4:7))

PC = PC + (2*(I1(8:15) sxt 16));

!ALU cycles

delay(3).

)

esac

)

esac

)

/*************************************

*/

/ *

*/

/* Executes opcode 1 group of instructions.

```

/\* Instructions : COC src,r

**\***/

```

Dec 31 15:52 1983 t9989.isp Page 25

★/

14

CZC src,r

*/

/*

XOR src,r

*/

/*

XOP src,r

*/

/*

LDCR src, count

1*

STCR src, count

*/

*/

/*

MPY src,r

1*

*/

DIV src,r

*/

/*

op_1 :=

(

state temp(0:15),temp1(0:32),temp2(0:16),temp3(0:16),

cnt(0:3);

case (Size concat Dmode)

0 : ! COC src,r

(

Dl = src\_opr(Dn,r,W).

Sl = src\_opr(Sn,r,W).

!ALU cycles

delay(3).

EQL = ((Dl and Sl) eql Dl)

)

1 : ! CZC src,r

D1 = src\_opr(Dn,r,W).

S1 = src\_opr(Sn,r,W).

!ALU cycles

delay(3).

EQL = ((Dl and Sl) eql Sl)

)

2 : ! XOR src,r

D1 = src_opr(Dn,r,W).

Sl = src_opr(Sn,r,W).

D2 = D1 \text{ xor } S1.

delay(2)

!ALU cycles

dst_opr(D2,Dn,r,W,se_f1)

)

3 : ! XOP src,r

(

ST(6) = high;

temp = (4 \times Dn + 0 \times 40) .

context_switch(temp) .

!ALU cycles

delay(7).

wreg((eff_addr(Sn,Smode,W)),ll,W)

4 : ! LDCR src,count

temp = rreg(12,W) . temp(0:2) = low.

cnt = I1\langle 6:9 \rangle.

if ((cnt ext 8) leq 8) and ((cnt ext 8) gtr 0)

D2 = eff_addr(Sn, Smode, B).

Al = src_opr(Sn, Smode, B).

```

```

Dec 31 15:52 1983 t9989.isp Page 26

if D2\langle 15\rangle eql 1

(

D1\langle lobyte \rangle = Al\langle byte \rangle.

LAE(Al,B); P = parity(Al(byte)).

abus = temp(0:14).

cru transfer(cnt,15)

else

(

D1\langle byte \rangle = A1\langle byte \rangle.

LAE(A1,B); P = parity(A1\langle byte \rangle).

abus = temp(0:14).

cru transfer(cnt,7)

)

else

(

D2 = eff_addr(Sn,Smode,W).

D1 = src_opr(Sn,Smode,W).

LAE(D1,W).

abus = temp(0:14).

cru_transfer(cnt, 15)

);

!ALU cycles

delay(5).

)

5 : ! STCR src, count

temp = rreg(12,W) . temp(0:2) = clear.

cnt = I1\langle6:9\rangle.

if ((cnt ext 8) leq 8) and ((cnt ext 8) gtr 0)

if Smode eql 3 ! auto increment

D2 = rreg(Sn, Size)

else

D2 = src_opr(Sn,Smode,W). ! read destination

if Smode eql 2

! before storing

PC = PC - 2.

abus = temp(0:14).

do

memen = high .

delay(clk +(3*phase));

D1(0) = cruin.

delay(phase)

cnt = cnt - 1.

delay(clk)

if cnt neq 0

D1 = D1 /: logical 1;

abus = abus + 1

```

```

Dec 31 15:52 1983 t9989.isp Page 27

until (cnt eql 0).

if (I1(6:9) \text{ ext } 8) \text{ neq } 8

D1 = D1 /: logical (8 - (II(6:9) ext 8)).

dst_opr(D1,Sn,Smode,B,se_f1);

P = parity(Dl(byte))

else

abus = temp(0:14).

do

memen = high .

delay(clk+(3*phase));

D1(0) = cruin.

delay(phase)

cnt = cnt - 1.

delay(clk)

if cnt neq 0

D1 = D1 /: logical 1;

abus = abus + 1

until (cnt eql 0).

if (I1(6:9) \text{ neq } 0)

D1 = D1 /: logical (16 - (I1(6:9) ext 8)).

dst_opr(D1,Sn,Smode,W,se_f1)

);

delay(8) .