# intellite.ch

1

1

1

1

1

T

(

The Intelligent Use of Technology

2 VALIDATION OF N.mPc/N.2 MICROPROCESSOR SIMULATION

INT-84-38

91 C655 C66692 1984

$(\mathbf{z})$ VALIDATION OF N.mPc/N.2 MICROPROCESSOR SIMULATION

Industry Canada Librarv Queen JUL 2 0 1998 Industrie Canada Bibliothèque Queen

SEPTEMBER 1984

Max Streit Prepared By: Dr. S.A. Mahmoud Approved By: Dr. C. Laferriere

COMMUNICATIONS CANADA-MAY 10 1905 LIBRARY - BIBLIOTHÈQUÈ

# INTELLITECH CANADA LIMITED

352 MacLaren Street Ottawa, Ontario K2P OM6 Government Gouvernement of Canada du Canada

Department of Communications

# DOC CONTRACTOR REPORT

DOC-CR-SP - 84 - 04

DEPARTMENT OF COMMUNICATIONS - OTTAWA - CANADA

SPACE PROGRAM

TITLE: Validation of N.mPc/N.2 Microprocessor Simulation

AUTHOR(S): Max Streit Intellitech Canada Ltd. 352 MacLaren St. Ottawa, Ontario

ISSUED BY CONTRACTOR AS REPORT NO: INT-84-38

PREPARED BY: Max Streit

DEPARTMENT OF SUPPLY AND SERVICES CONTRACT NO: OER 83-05075

DOC SCIENTIFIC AUTHORITY: Michel Savoie Communications Research Centre Ottawa, Ontario

CLASSIFICATION: Unclassified

This report presents the views of the author(s). Publication of this report does not constitute DOC approval of the reports findings or conclusions. This report is available outside the department by special arrangement.

DATE: SEPTEMBER 1984

# Summary

This document describes the validation of a hardware simulation facility and a microprocessor software development environment. The hardware simulation facility is provided by the CAE tool N.mPc whereas the software development environment is provided by a commercial cross software development package.

The validation scenario first involves the development of target microprocessor software in a high level language. For comparison the target software is then cross compiled and run on a simulation of the target hardware (itself running on the VAX 11-780), the actual target hardware and directly on the VAX 11-780.

The target software used is a simple spacecraft attitude control algorithm and the target hardware is an Intel 8086 based single board computer. The cross software development environment, the target software, and the target hardware simulation are described. This report is part of the work done under DSS contract OER 83-05075 for the Communications Research Centre of the Department of Communications, Government of Canada.

# TABLE OF CONTENTS

| 1.    | INTRODUCTION1                                                                          |

|-------|----------------------------------------------------------------------------------------|

|       | 1.1. Background1                                                                       |

| × ,   | 1.2. Overview of N.mPc2                                                                |

|       | 1.3. Report Structure                                                                  |

|       | 1.4. Related Documentation                                                             |

|       |                                                                                        |

| 2.    | VALIDATION SCENARIO                                                                    |

|       |                                                                                        |

| 3.    | DESCRIPTION OF THE INTEL 86/12 SBC SIMULATION9                                         |

|       | 3.1. The Intel 8086 CPU12                                                              |

|       | 3.2. The ROM                                                                           |

|       | 3.3. The Multibus Interface                                                            |

|       | 3.4. The Global Memory18                                                               |

|       | 3.5. The Dualport RAM20                                                                |

|       | 3.6. The Programmable Interrupt Controller (PIC)20                                     |

|       | 3.7. The IO Facility                                                                   |

|       | 3.8. The Simulated iSBC 86/12 Single Board Computer27                                  |

| 4     | TEST SOFTWARE DEVELOPMENT FOR SIMULATED AND ACTUAL HARDWARE 31                         |

| 4+    |                                                                                        |

|       | 4.1. The Enhanced Software Development Environment for 8086<br>Based N.mPc Simulations |

|       |                                                                                        |

|       | 4.1.1. The "C"-Crosscompiler                                                           |

|       | •                                                                                      |

|       | 4.1.3. The "OTOL" Program                                                              |

|       | 4.1.4. Command Files For The Cross Software Tools40                                    |

|       | 4.2. Software Development for an actual Intel SBC41                                    |

|       | 4.3. Description of the Target Software for the Validation41                           |

| 5.    | VALIDATION/TEST PROCEDURES                                                             |

| 6.    | COMPARISON OF SIMULATION AND ACTUAL RESULTS                                            |

| •••   | 6.1. Interpretation of the Validation Results                                          |

|       | 6.2. Performance of Simulated and Real Hardware                                        |

|       | 0.2. reitormance of simulated and Kear nardware                                        |

| 7.    | SUMMARY AND CONCLUSIONS                                                                |

|       |                                                                                        |

| RE FI | CRENCES                                                                                |

APPENDIX A: Complete Directory of Intel :SBC 86/12 Files

- APPENDIX B: B.1

- B.1 Mathematical Basics of the "Simple Attitude Control Algorithm"

- B.2 The Validation Testprogram Running on the Actual Intel SBC Hardware (CMD.C, = CMVAL.C86)

- B.3 The Validation Testprogram Running on the Simulated Intel SBC Hardware ("VALCMD.C")

- B.4 The Benchmark Program Used for Performance Tests

APPENDIX C: Test Software Development and Execution Procedure for the actual Intel SBC Hardware

- APPENDIX D: D.1 Test Software Development and Execution Procedure for Simulated Intel SBC Hardware

- D.2 Performance Test Execution Procedure for Simulated Intel SBC Hardware

- APPENDIX E: Printouts from Running the Performance Testprogram on Simulated Intel SBC Hardware

- APPENDIX F: Listing of the Topology File for the Simulation of the 86/12 SBC

- APPENDIX G: The "OTOL" Program

- APPENDIX H: H.1 The Program Used To Test the Simulated 8086 CPU

- H.2 List of "Bugs" fixed in the initial 8086 CPU Descriptions

- APPENDIX I: Listing of the I/O Assembly Routines used in the Validation Simulation ("PRINT.S", "IN.S")

# LIST OF FIGURES

| 1-1: Elements of the N.mPc System4                                                                                                                                                                                                                      |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 2-1: The Validation of N.mPc as a CAE Tool8                                                                                                                                                                                                             |  |

| 3-1: The iSBC 86/12 Single-Board Computer103-2: The Simulated 86/12 Hardware113-3: The Simulated 8086 CPU143-4: The Simulated ROM163-5: The Multibus Interface193-6: The Global Memory213-7: The Simulated Dualport RAM22                               |  |

| <ul> <li>3-8: The Programmable Interrupt Controller</li></ul>                                                                                                                                                                                           |  |

| <ul> <li>4-1: Standard Software Development in N.mPc</li></ul>                                                                                                                                                                                          |  |

| <ul> <li>6-la:Running the Validation Program on the Simulated 86/1249</li> <li>6-lb:Running the Validation Program on the Simulated 86/1250</li> <li>6-2a:Running the Validation Program on the Actual Intel SBC<br/>Hardware (output in hex)</li></ul> |  |

| <ul> <li>6-2b:Running the Validation Program on the Actual Intel SBC<br/>Hardware (output in decimal</li></ul>                                                                                                                                          |  |

| 7-1: Fault Tolerant Computer Architecture                                                                                                                                                                                                               |  |

# 1. INTRODUCTION

# 1.1. Background

In recent years Computer Aided Engineering (CAE) tools have made it possible to choose a new, more flexible approach for the design of microcomputer systems. Traditionally, microcomputer based products are designed in the following fashion:

- The necessary hardware components are built. This usually includes the microprocessor itself as well as other peripheral components.

- 2. Software programs are written for the target machine.

- 3. Software and hardware components are integrated and tested. Very frequently, the software is produced on a host machine using a cross development package, if available.

The development process usually involves many time consuming and costly iterations. A CAE tool such as N.mPc improves the situation by providing a simulation environment which is suitable for testing many design alternatives in a short period of time. The implications of using N.mPc are as follows:

1. It is no longer necessary to build the hardware components at the beginning of the design work. Instead, N.mPc provides what amounts to a micro-programmable, register transfer level machine which can be programmed to emulate the target hardware completely. In other words, a designer working on a VAX host, for example, could create a VAX executable program which, when run, would emulate the target hardware.

2. N.mPc provides a totally programmable cross development package for the software to be written in assembly language. The work documented in this report introduces an enhanced software development environment permitting to write software in the C high level language.

3. The rationale for using a tool such as N.mPc is that programmability implies flexibility. Given that a base exists, i.e. most of the hardware emulation is available as well as the cross development package, a designer can alter the design parameters with ease and test various alternatives without committing to any hardware choice.

The new approach to microcomputer design is of particular importance in a field like space technology where fault tolerant onboard processing is a very urgent need. Fault tolerance implies redundant multi-processor architectures of considerable complexity. Thus the development of a fault tolerant computer architecture for space purposes looks like an ideal application of the CAE Tool N.mPc.

In order to get a reliable, independent indication for the potential of CAE tools in multiprocessor design, the validation of the hardware simulation facility N.mPc and of an enhanced software development environment were included in the objectives of this work done for the Communications Research Centre of the Department of Communications.

### 1.2. Overview of N.mPc

It is assumed that the reader, having read the "N.mPc Detailed System Description" document [16], is already familiar with the elements of the N.mPc system. A short overview of N.mPc is given here as a

reminder.

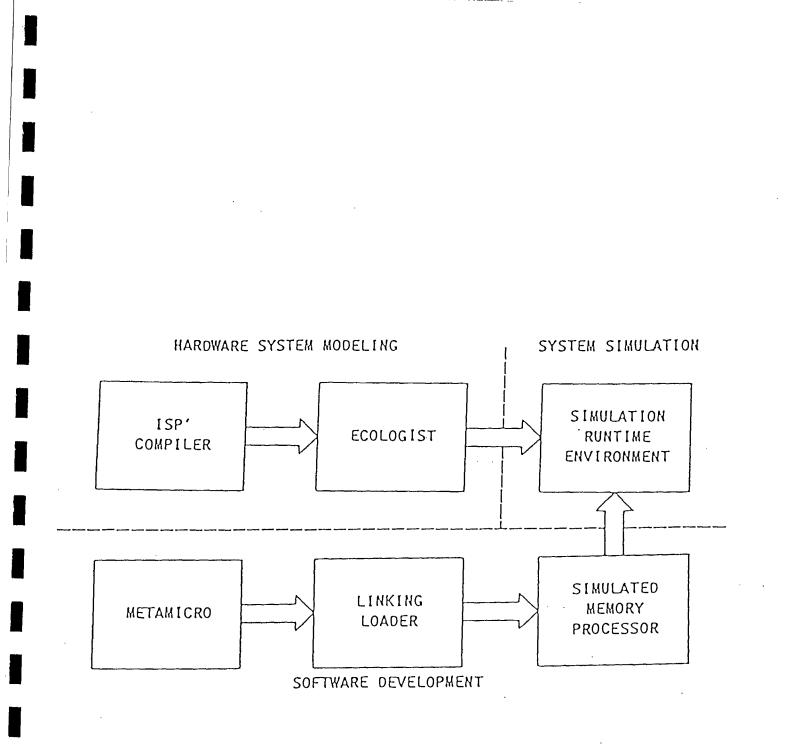

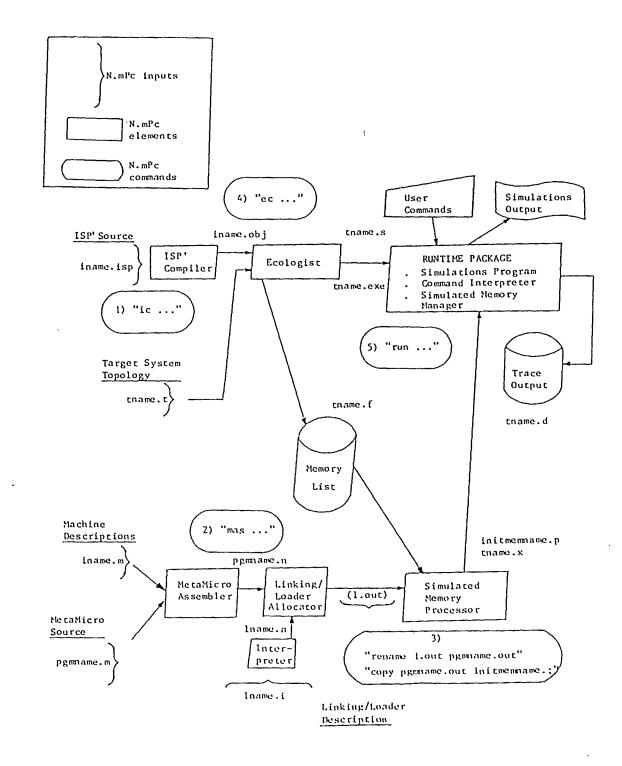

N.mPc consists of six components used either to describe the hardware behaviour of a target system, or to execute the simulation of that system. Figure 1-1 illustrates the components of N.mPc and their interaction.

The Meta-micro assembler and the linking loader are used to generate the software which is to be executed by the simulated hardware components if these are programmable. Both are driven by a description of the instruction set of a target machine and can be made to generate code for either vertically or horizontally programmed machines. The linking loader produces code which is executed by a simulated processor The ISP' compiler is used to produce or by an actual machine. modules for individual processors and other hardware simulation components of a system. The input language of the compiler is the ISP language which allows the specification of states for the implementation of processor registers and flags, memories for the simulation of memory, and ports which allow input to and output from simulated hardware.

The N.mPc ecologist and a simulated memory processor link the ISP processor modules with the linking loader outputs in order to form complete simulations. A run-time package is used to execute a simulation and to allow extensive interaction with the simulation.

# 1.3. Report Structure

Section 1 introduces the reader to background, motives and objectives of the work documented in this report. Section 2 outlines the approach chosen to validate an N.mPc microprocesor simulation. Section 3 describes the simulation of an Intel 86/12 SBC hardware on the N.mPc system. Section 4 covers the development of the test software run

Figure 1-1 Elements of the N.mPc System

~

on the simulated and the actual hardware to perform the validation of N.mPc for microprocessor simulations. Section 5 gives some detailed information about how to run the validation test program on the actual and the simulated hardware. Section 6 presents the results from the validation test program and the performance test. Section 7 gives a summary of accomplishments and makes conclusions regarding the strong points and the perceived shortcomings of the CAE tool N.mPc.

# 1.4. Related Documentation

This report is one of the deliverables identified under contract OER 83-05075. Other reports submitted under the same contract include an N.mPc detailed system description document [16], an N.mPc User Manual [7], a report on the simulation of the SBP 9989 microprocessor [8], and two reports on a Fault Tolerant Computer Architecture and a Fault Tolerant Operating System [14], [20]. References to the original N.mPc documentation, provided by the vendor of the N.mPc package, are also listed.

# 2. VALIDATION SCENARIO

The primary goal of this work was to validate N.mPc as a CAE tool This includes the investigation of for microprocessor simulations. N.mPc's potential as a hardware and software development tool. The idea was not only to develop a simulation of a fairly complex hardware module but also to introduce the enhanced software development environment for This 8086 based N.mPc simulations which is described in section 4.1. would allow to do software development in a high level language and was considered to be quite an achievement in the N.mPc context. Besides the validation of N.mPc as a CAE tool for microprocessor simulations, the validation activities would have some useful by-products, namely the development of a reliable, powerful microcomputer simulation of the 86/12 SBC and the introduction of the enhanced software development environment mentioned above.

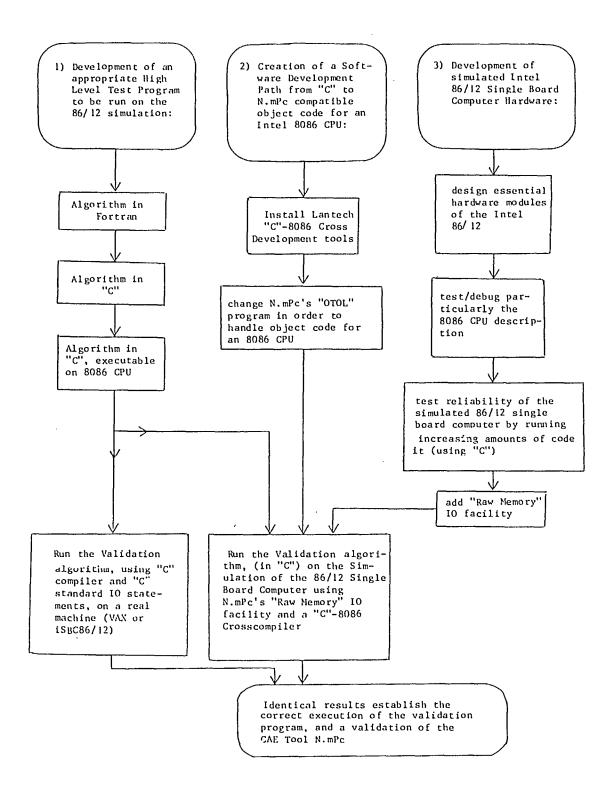

With the above goals in mind, the following activities were planned to validate N.mPc:

- The design of hardware modules simulating the Intel iSBC 86/12 single board computer.

- The use of an 8086 C cross software development package to develop software in C that could be run on the 86/12 simulation.

- The implementation of an algorithm, taken from a space attitude control system, on the simulated hardware using C as a high level programming language.

- Run a benchmark program on simulated and actual Intel SBC hardware in order to do a performance comparison.

The choice of simulating an 86/12 single board computer was made because its complexity represents a challenge in terms of N.mPc simulations and

because a description of the heart of the 86/12, the 8086 CPU, was contained in the N.mPc microprocessor description library. C was chosen for the use as a modern high level language as it allows for close interaction with the hardware.

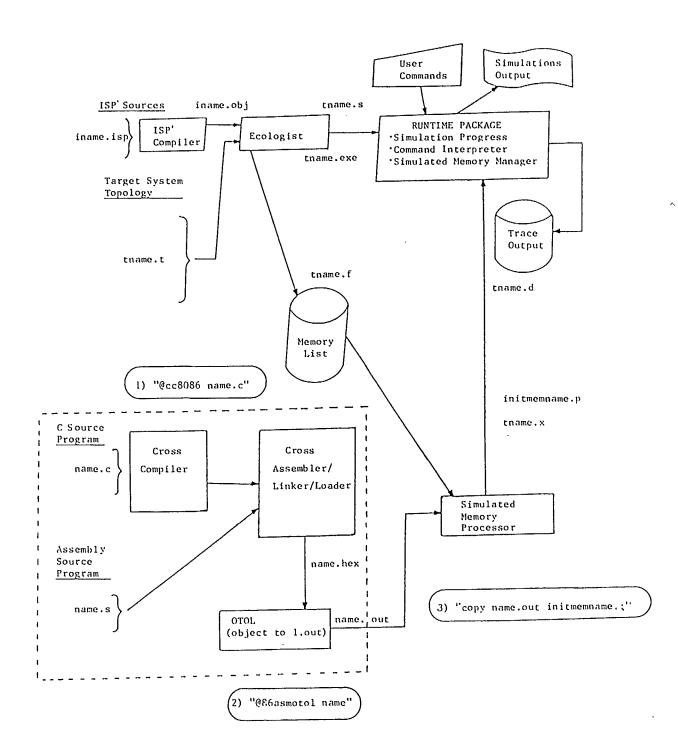

Figure 2-1 shows the activities carried out for the validation of N.mPc as a CAE Tool for microprocessor simulation. The activities denoted as 1), 2) and 3) in Figure 2-1 have been described in sections 3, 4 and 5.

As a result of the above mentioned activities the simulation of the 86/12 SBC and the enhanced software development environment were used to build the "Validation Simulation". The goal was to execute a simple spacecraft attitude control algorithm, implemented in "C", on both the simulated 86/12 SBC hardware as well as on an actual Intel SBC machine. Results and performance from these tests were to be used to determine the validity of the CAE tool N.mPc for a specific simulation.

Figure 2-1: The Validation of N.mPc as a CAE Tool

# 3. DESCRIPTION OF THE INTEL 86/12 SBC SIMULATION

The Intel 86/12 is a single board computer that is based on the Intel 8086 CPU. The 86/12 SBC was chosen for simulation, mainly because a description of the 8086 CPU was available in the N.mPc microprocessor library (see [7], section 3). The 8086 also is an interesting processor for space related research as it is to be space qualified soon.

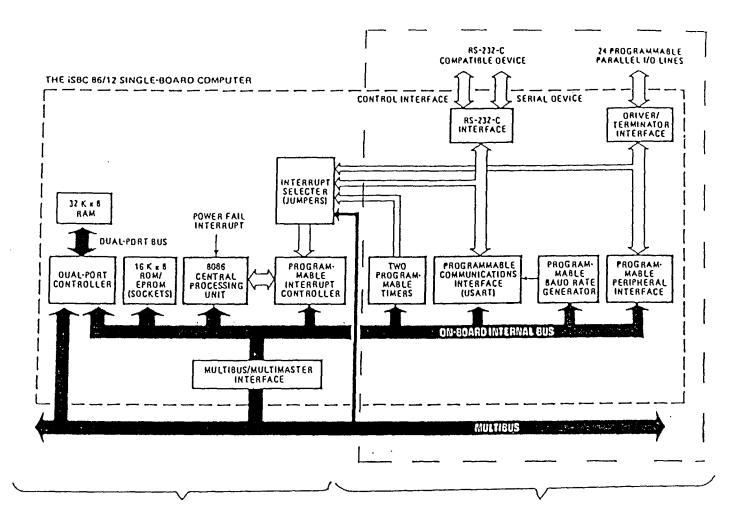

Figure 3-1 shows all the components of the 86/12 SBC. An 8086 CPU is the heart of the SBC structure. Other essential components are a programmable interrupt controller, memories (ROM, dual-port RAM) and the multibus interface. The Multibus allows the 86/12 SBC to communicate with other SBCs or with devices tied to the Multibus. Additional elements like the programmable communications interface, the baud rate generator, the peripheral interface, the RS-232-C interface and the driver/terminator interface provide various I/O functions. Programmable timers have also been included and may be used in certain applications.

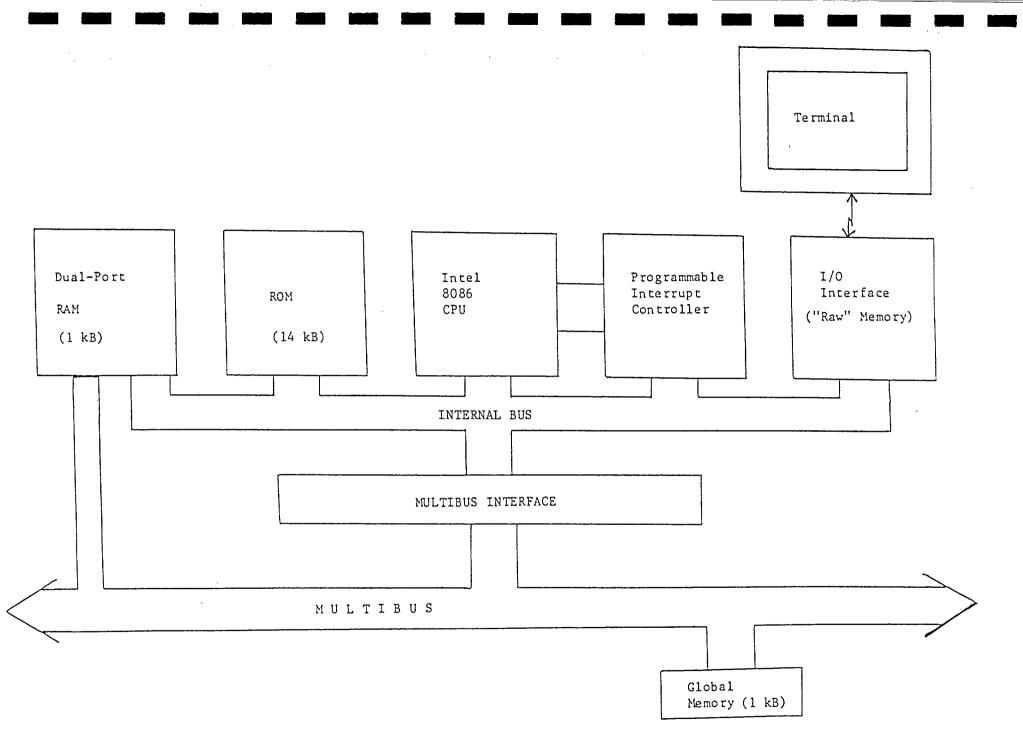

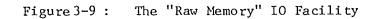

To reduce the cost and the duration of the development of the simulation, only the necessary 86/12 components will be simulated. The essential subset of 86/12 elements to be simulated is shown in the left The complex I/O interfaces depicted in the right half of Figure 3-1. half of figure 3-1 are not needed for the intended simulation. N.mPc's memory" feature will be used to do I/O operations. Figure 3-2 "raw the structure of the simulated 86/12 SBC. The remainder of this shows section will describe each component of the 86/12 SBC simulation.

to be simulated using N.mPc

not needed for simulation purposes; N.mPc's "raw memory" feature used for I/O

# Figure 3-1

The iSBC 86/12 Single-Board Computer (from Intel Application Handbook, Sept. 81)

# Figure 3-2: The Simulated 86/12 Hardware

•

1-

# 3.1. The Intel 8086 CPU

The starting point of the development of a hardware description for the Intel 8086 CPU was an ISP' description of this microprocessor written by Y. Trivedi, Case Western University, for the N.mPc library. A few initial tests showed that this description required considerable testing/debugging in order to obtain the reliability needed for Therefore, the simulations of fault tolerant computer architectures. first and most important step was a thorough testing and debugging of the 8086 CPU description, a program of well over 3000 lines of code in The test program used for this purpose (see Appendix H) included size. The instructions were tested by every single 8086 instruction. executing them in various addressing modes.

activities consisted of setting up the appropriate Testing registers and/or memory locations for a particular instruction and these registers/memory locations after execution for correct checking If an instruction was not executed the way the Intel 8086 results. Hardware Manual prescribed, the error had to be found through a time The usual errors found consisted in misuse consuming debugging effort. of the ISP language or misunderstanding of how the 8086 hardware really A list of the "bugs" found in the initial 8086 description is worked. part of Appendix H. One type of error resulting from a misuse of the hardware language deserves to be specially mentioned here. This ISP' error consists in wrongly determining the size of the operands of an instruction, for instance by testing a wrong bit. The result is a byte instruction trying to handle word operands (or the reverse), an ambiguity which cannot be properly handled by N.mPc and which causes the VMS operating system to halt operations. The fact that the simulation the runtime mode altogether disables the usual debugging tools. leaves

Only very thorough knowledge of the ISP' code in question, or iterative reduction of the user program until the fault-causing instruction is determined, can help. The N.2 system, which is to be released soon, should solve the above difficulty with VMS.

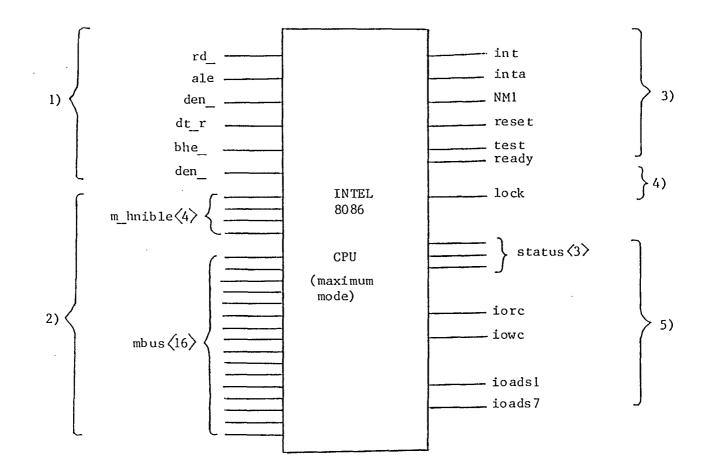

Figure 3-3 shows the communication ports used by the simulated 8086 CPU. The simulated 8086 is configured in "maximum mode" because the alternative "minimum mode" limits a CPU to standalone use. The "maximum mode" is therefore compulsory for multi-processor applications. As the goals of this work did not include the design of any co-processors (8087 Math Processor, 8089 IO Processor) for the 8086, the ports serving for this purpose were not implemented (request/grant lines, queue status lines). Some signals, which are usually generated on a separate bus controller chip because of lack of space on the 8086 chip, are part of the simulated 8086 (den , dt r, ale, inta).

Internally the simulated 8086 represents a very accurate model of the real 8086 chip. Like the "Bus Interface Unit" in the real 8086, a "BIU" constantly refills a queue of process called prefetched instructions which are to be executed by a second process called "EU (Execution Unit)". The "EU" process reacts to external events (interrupts, resets); fetches, decodes and executes instructions from At this point, it should be stressed that N.mPc the prefetch queue. hardware descriptions resemble black boxes behaving like real hardware when observed from the exterior but which are entirely different Hardware descriptions designed using the N.mPc system can, internally. and usually do, have an internal structure and complexity which is very similar to the actual hardware they model. In N.mPc this is true down to the register transfer level which strengthens N.mPc's potential in hardware design.

- 1) memory access signals

- 2) multiplexed address/data bus

- 3) control signals (interrupts etc.)

- 4) bus priority lock control

- 5) Multibus signals

Figure 3-3: The Simulated 8086 CPU

.:.

Another aspect of the simulated 8086 is that the user has to initialize segment registers, stackpointer and instruction pointer himself. In real applications an operating system usually takes care of such details. As there is no operating system on top of this hardware simulation, the user is responsible for the proper initialization of the 8086 before running a program. Section 5 provides the details concerning the initialization of the simulated 8086 CPU.

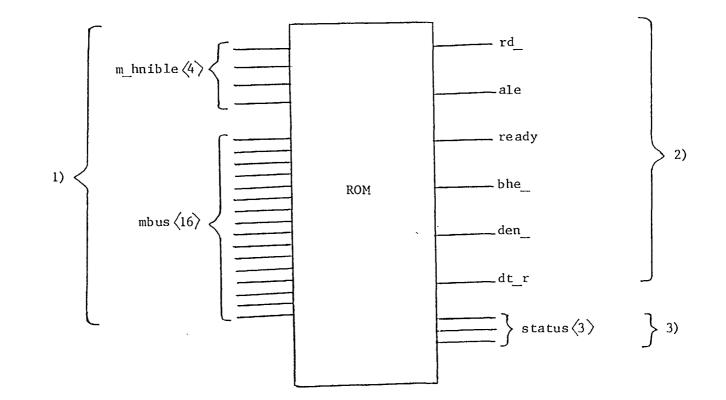

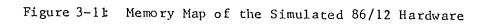

### 3.2. The ROM

Three simulated memories are part of the 86/12 single board computer simulation (as shown by the memory map in Figure 3-11). This section will concentrate on the Read Only Memory (ROM). Figure 3-4 shows the address data lines and signals that allow an 8086 to access It has to be added that for two reasons the "ROM" is not yet the ROM. in a read only mode in the context of the validation simulation used (see \*). Firstly, the N.2 system, which will soon fully supersede N.mPc, offers the possibility to declare ports that have attributes like "read only", "write only", "read/write" (see "N.2 ISP' User's Manual [15], page 13). Secondly, a ROM is not essential for the work described this document as N.mPc can be made to perform a complete in initialization of a RAM module at the beginning of the simulation. The fact that the RAM memory can still be accessed for write does not present any difficulty since such an operation can easily be disallowed.

(\*): Due to the flexibility inherent to N.mPc based simulations, certain liberties were taken with the Read Only Memory (ROM) module. In fact the ROM was used as RAM by the compiler for its stack and dynamic data area. This does not detract from the purpose and goals of the validation.

- 1) multiplexed address/data bus

- 2) memory access control signals

- 3) CPU status

The memory address range used by the ROM is determined by the numerical values assigned the macros "LOROM", "UPROM" in the ISP<sup>7</sup> description of the ROM. The address ranges of the other simulated memories in the 86/12 simulation are determined in a similar manner and it is therefore very easy to change the whole memory configuration. Currently, the ROM services the address range from 1024 (1k) to 14335 (14k-1) as shown in the memory map of Figure 3-11.

The name by which N.mPc's "Simulated Memory Processor (SMP)" identifies the ROM among the three simulated memories that are part of a simulation is "romcore.;". If a user wants his program to be loaded into the ROM as an initial content, he simply creates a new version of the "l.out" formatted object version of his program and renames it to "romcore.;". The SMP will then know that the destination of the program is the ROM. The name "romcore.;" is chosen by the user but has to be previously declared in the topology file.

The simulated ROM is accessed exactly the same way as the real 8086 accesses memory: Words starting at even addresses are accessed in one memory cycle, words located at odd addresses need two memory cycles to be read. The CPU indicates whether a memory access or an IO operation is to take place by a "status" signal (see Figure 3-4). A "ready" signal holds the CPU until a memory access is over.

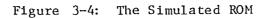

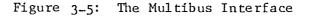

# 3.3. The Multibus Interface

In Figure 3-2 one can see that the simulated 8086 uses an "Internal Bus" to access memory directly. In multiprocessor configurations a bus like Intel's "Multibus" will be used for interprocessor communication and resource sharing. As the "Multibus" is part of the intended 86/12 single board computer simulation, an interface between the "Internal

Bus" and the "Multibus" is needed. Figures 3-5, 3-1, 3-2, and 3-10 illustrate the Multibus interface.

The Multibus interface will respond only to memory accesses in a range assigned to the Multibus. Like in the case of the ROM, two macros in the ISP<sup>-</sup> description of the Multibus interface determine the address range. In the 86/12 simulation, the Multibus address range is set from 14336 (14k) to 16383 (16k-1) as shown in Figure 3-11.

In a multiprocessor configuration, several processors may want to use the Multibus at the same time. The Multibus interface not only translates the usual memory access of an 8086 (via internal bus) into a memory access following the Multibus protocol but also implements an arbitration scheme for the different Multibus masters. The method used relied on a serial priority scheme in which every processor has to wait for a bus grant signal to be activated. After using the Multibus, a processor passes the bus grant "token" on to the next one and so on.

A few Multibus lines were not relevant for simulation purposes and were therefore not implemented; among these lines were the Initialization signal, RAM/ROM Inhibit, Bus, Constant clock, Common Bus Request, Power Supply lines, etc.. It should be pointed out that the Multibus interface is transparent from the standpoint of a processor. The only noticeable sign of a Multibus use might be a longer wait when different Multibus masters are competing for the Multibus.

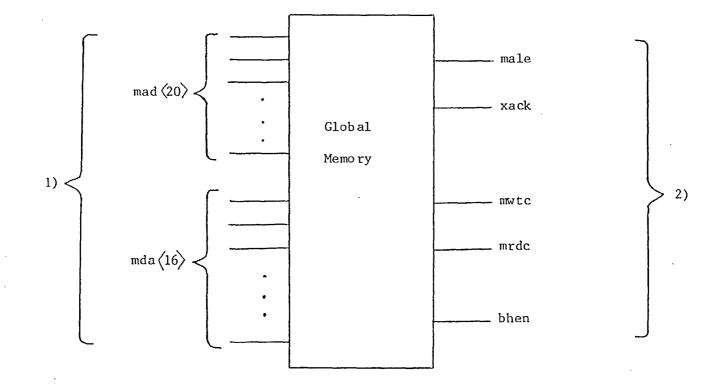

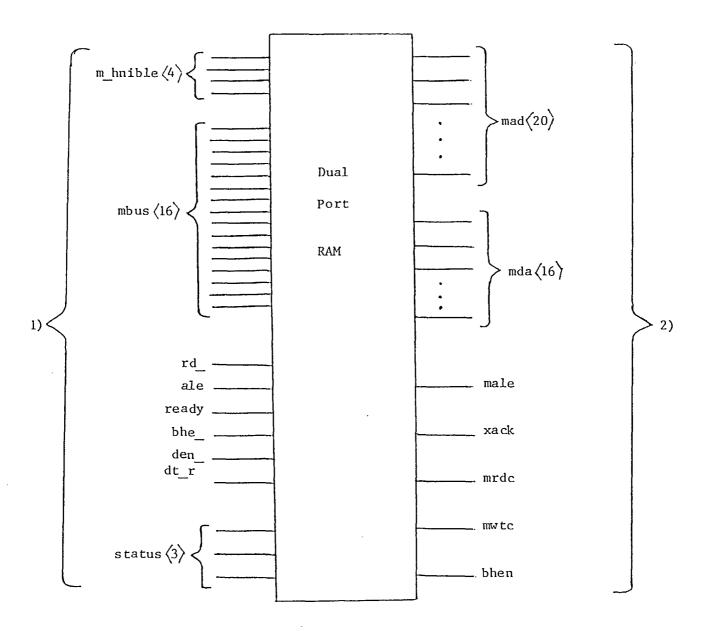

# 3.4. The Global Memory

The "Global Memory" is accessed exclusively via Multibus using the Multibus signals and protocols. A Multibus may have multiple masters thus making the global memory accessible to all processors tied to the Multibus. The global memory may be used for interprocessor

- l) Internal Bus Side

- 2) Multibus Address Lines (20) and Data Lines (16)

- 3) Multibus Signals

- 4) Multibus Arbitration Lines

communication (mailbox) or simply as a shared resource.

The address range of the global memory has to be within the address range assigned to the Multibus (see section 3.3). In the 86/12 simulation, the global memory is assigned the address range from 14336 (14k) to 15359 (15k-1) as shown in Figure 3-11. The signals, address lines and data lines used by the global memory are all part of the Multibus lines and are shown in Figure 3-6. The global memory is identified by N.mPc's "Simulated Memory Processor" by the name "gblcore.;".

## 3.5. The Dualport RAM

The Dualport RAM is a combination of a RAM and a global memory allowing to access a given set of memory locations either via the Multibus or directly via the Internal bus. In the 86/12 simulation, the CPU accesses its RAM directly via the internal bus using the address range from 0 to 1023 (1k-1). On the other hand, the CPU (or any other Multibus master) can also access the same memory locations using the (Multibus) address range from 15360 (15k) to 16383 (16k-1). The Multibus addresses of the RAM are translated down into the 0 to 1023 range.

The Dualport RAM delays access attempts via Multibus while it is being accessed via the internal bus and vice versa. The internal bus has priority over the Multibus. Figure 3-7 shows the two buses connected to the Dualport RAM and Figure 3-11 shows the two different address ranges used to access the Dualport RAM.

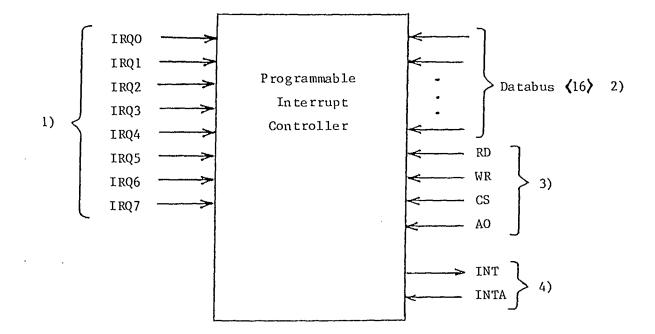

# 3.6. The Programmable Interrupt Controller (PIC)

The PIC designed for the 86/12 simulation represents a subset of the functionality of the real Intel 8259 chip. The full set of

1) Multibus Address and Data Lines

2) Multibus Control Signals

Figure 3-6: The Global Memory

- 1) ports for access of RAM by CPU

- 2) ports for access of RAM via Multibus

Figure 3-7: The Simulated Dualport RAM

different hardware functions and priority resolution schemes is not needed in a simulation context. The basic idea was to implement a fully functional PIC but only for the given 86/12 hardware and one single interrupt priority resolution scheme. The priority resolution scheme chosen scans the 8 interrupt request lines from line 0 to line 7 continuously. If an interrupt request line is scanned while being active the request is serviced, the request line is reset and the scanning restarts again at line 0. A request line is activated by the leading edge of a strobe on that line and stays activated until reset. It can be seen that the scanning is not cyclic and gives the lower numbered request lines a higher priority.

Figure 3-8 shows the simulated PIC and its ports. A "Signal Generator" was designed for convenient testing of the interrupt facilities in the 86/12 simulation. It periodically generates a "pulse" on each interrupt request line. This is an asynchronous way of triggering all the interrupts for testing purposes.

An interrupt is serviced in exactly the same manner as in the real 86/12 single board computer. The positive edge of a pulse on an interrupt request line sets the corresponding bit in the PIC's Interrupt Request Register (IRR). The interrupt may have to wait until it becomes the highest priority request when other interrupts have been activated as well. Once the interrupt has the highest priority, the PIC goes ahead and activates the CPU's "INT" line to signal the interrupt to the CPU. The CPU responds with a succession of two pulses on the "INTA" (interrupt acknowledge) signal, thereby reading the interrupt type which is put on the lower half of the data bus by the PIC. The 8086 then gets the interrupt vector (new instruction pointer, new CS register content) stored at the four memory locations starting at (4 \* interrupt type).

- 1) Eight interrupt request inputs.

- The lower half of the databus is used to send the interrupt type to the CPU.

- 3) Signals used for PIC programming via CPU.

- 4) Interrupt request lines.

Figure 3-8: The Programmable Interrupt Controller

The CPU then executes the interrupt service routine corresponding to the interrupt vector it acquired and, upon completion, returns to the execution of the interrupted program.

It is possible for the CPU to access the PIC's internal registers by doing IO operations using addresses assigned to the PIC by the designers of the 86/12. The following PIC register accesses may be carried out on the simulated PIC:

- Set Interrupt Mask Register:

MOV a1, OFh OUT OC2h, a1

These instructions mask interrupt lines 0 to 3.

Read Interrupt Mask Register:

IN al, OC2h

Read Interrupt Request Register:

MOV al, OAh OUT OOCOh, al IN al, OOCOh

Read In-Service Register:

MOV a1, OBh OUT OOCOh, a1 IN a1, OOCOh

It is also possible to have the CPU initialize the simulated PIC but this is in fact irrelevant as the simulated PIC has been dedicated to a single priority resolution mode and to the 86/12 hardware.

### 3.7. The IO Facility

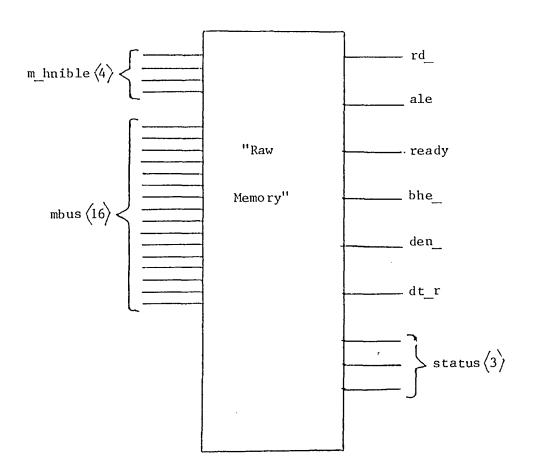

The IO module "terminal.isp", shown in Figure 3-9, makes it possible for N.mPc simulations to read and write directly from/to the working terminal. This "Raw Memory" has a structure almost identical to that of the ROM described in Section 3-4. The "Raw Memory", though, has

just one memory location and only responds to IO calls to address 0. In order to have the "Raw Memory" address the terminal driver, the name assigned to the working terminal under the VMS operating system has to be declared in the topology file. This name is "tt:" under VMS and is not compatible with the syntax used in the topology file. To resolve this situation a new logical name compatible with the topology file syntax has been defined ("wtty" for "tt:") in one of the login files (logsys.com). For details about "raw memories" refer to the "Ecologist User's Manual" ([4], Section 2.1.6). The following examples show how IO operations using the "terminal.isp" raw memory are carried out:

a) output to working terminal: MOV al, #97 OUT al, #0

These instructions write the letter "a" (=97 in ASCII) on the screen of the working terminal.

b) input a character from the working terminal: IN al, #0

NB: The ASCII code for the first character on the working terminal's screen will be put into al.

The "Raw Memory" feature provides N.mPc simulations with a simple IO mechanism that is sufficient for the needs of most simulations.

# 3.8. The Simulated iSBC 86/12 Single Board Computer

The components of the simulated 86/12 SBC as well as the interconnection of their communication ports is shown in great detail by Figure 3-10. For a simulation, the information about a set of simulated hardware modules and their interconnection is stored in a topology file. Appendix F contains the listing of the topology file for the simulation of the 86/12 SBC. Detailed information about how to write topology files is found in the "Ecologist User's Manual" [4]. Figure 3-11 is a memory map of the three contiguous, simulated memories used in the 86/12

| (16383)                                                              |  |  |

|----------------------------------------------------------------------|--|--|

| RAM (accessed via<br>Multibus, lk)                                   |  |  |

| (15360)<br>(15359)                                                   |  |  |

| Global Memory (1k):                                                  |  |  |

| initial memory name: "gblcore.;"<br>memory reference name: "gmem:me" |  |  |

| (14336)                                                              |  |  |

| (14335)                                                              |  |  |

| ROM (13 k):                                                          |  |  |

| initial memory name:"romcore.;"                                      |  |  |

| memory reference name:"rom:mem86"                                    |  |  |

|                                                                      |  |  |

|                                                                      |  |  |

| (1024)                                                               |  |  |

| (1023)                                                               |  |  |

| <u>RAM (1k):</u>                                                     |  |  |

| initial memoryname:"ramcore.;"                                       |  |  |

| memory reference name: "ram:me"                                      |  |  |

| (0)                                                                  |  |  |

simulation: RAM, ROM and Global Memory. For simulation of multiprocessor configurations one would simply have to tie multiple 86/12 modules onto the Multibus and set up the serial arbitration scheme for each processor's Multibus interface.

#### 4. TEST SOFTWARE DEVELOPMENT FOR SIMULATED AND ACTUAL HARDWARE

This section describes the development of the validation test software for the simulated and the actual Intel SBC hardware as well as the software development tools involved and their use. All test simulations involving the simulated 86/12 SBC hardware are also described in the N.mPc User's Manual [7] (section 2) and in textfiles in the corresponding directories.

# 4.1. The Enhanced Software Development Environment for 8086 Based N.mPc Simulations

Initially, the only way to develop software to be run on N.mPc simulated hardware involved the use of a programmable "Metamicro" assembler that was not entirely compatible with commercial 8086 assemblers. The use of this "standard" method of software development for N.mPc simulations is documented in Intellitech's N.mPc User Manual [7] and, as a reminder, is illustrated again in Figure 4-1.

Following current trends, a need was felt for using high level programming languages for more convenient software development. The use of this method for developing software to be run on simulated hardware is also documented by examples in Intellitech's N.mPc User Manual [7]. An overview of a simulation in the case of the "C" language and a simulated Intel 86/12 single board computer is given by Figure 4-2. The rest of section 4.1 will describe the use of "C" and commercial crossdevelopment tools in an N.mPc simulation context.

#### 4.1.1. The "C"-Crosscompiler

As mentioned above "C" was chosen to be the high level language in which a user would write programs. The 8086 "C" Cross Software Tools by Lantech Systems Inc. are described in the corresponding Lantech Manual

## Figure 4-1 : Standard

Software Development in N.mPc

2.

# Figure 4-2: High-Level Software Development In N.mPc

[19]. The package includes a "C" Cross Compiler and a "C" Cross Assembler/Linker/Librarian/Downline Loader for Intel 8086/8087/8088 processors.

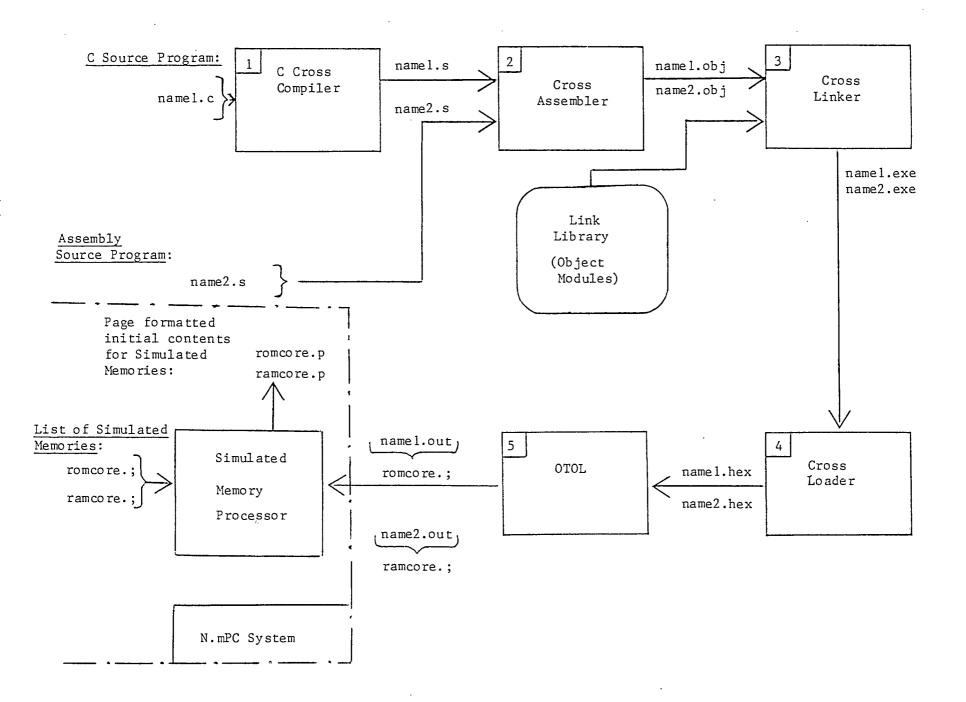

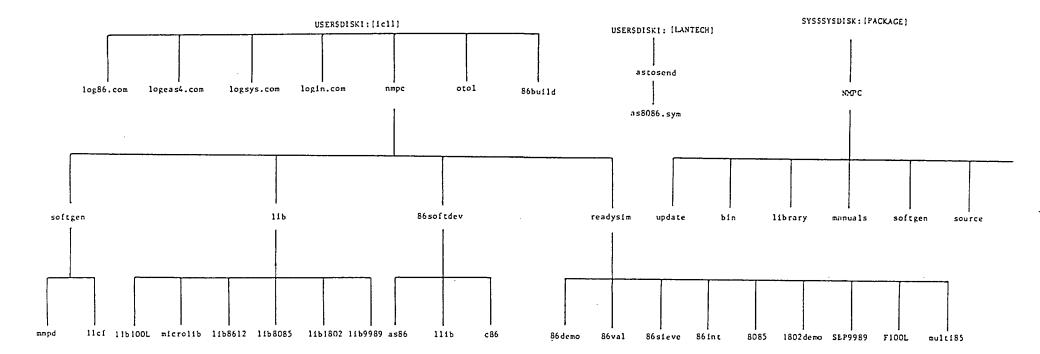

The steps necessary to run a program written in "C" on a simulated The situation 86/12 hardware are shown in detail in Figure 4-3. depicted in Figure 4-3 shows the path of a program written in "C" (namel.c) and a program written in Intel's ASM86 assembler (name2.s) through all the development stages. The two programs in the example are finally loaded into two different simulated memories of an N.mPc simulation by the "Simulated Memory Processor" (SMP). Figure 4-3 also shows how to do software development in an orderly manner. It is advisable to do the cross compiling of "C" programs in one directory ("c86") and the cross assembling/linking/loading plus the "otol" invocation in another ("as86"). The product of all software development (a ".out" file) is then copied into the actual simulation directory where it is loaded into some simulated memory. Doing software development in separate directories avoids having too many files in the simulation directory.

The Lantech Cross Development package was installed on the VAX/VMS environment which is host to the N.mPc system and is invoked using the commands declared in a login command file ("LOG86.COM", see User Manual [7], Appendix D).

Step 1 in Figure 4-2 shows how to invoke the cross compiler in order to create an 8086 assembly version of a C program. The operation involves several steps (preprocessor, parser, code generator, postprocessor) which are executed by a command file called "cc8086". This command file is located in the "C86" directory, which is reserved for high level software development. The command below is used to cross

Figure 4-3 : Detailed Look at High-Level Software Development in N.mPc

compile the C program "namel.c" in Figure 4-3:

" @cc8086 name1"

The output produced is a file with a ".s" extension and the same name as the input file: "namel.s".

It should be remembered that the Lantech cross assembler/linker/loader assumes that both an 8086 CPU and an 8087 math processor are to be found in the target system. It therefore relies on the floating point arithmetic instructions implemented by the 8087, whenever floating point operations are required in a C program.

The assembly programs produced by the C cross compiler are stack oriented. If one wants to write assembly routines that can be called by C programs, detailed knowledge of the use of the stack by the code produced by the cross compiler is required. The Lantech documentation [19, chapter 7] contains detailed information on this subject.

#### 4.1.2. The Cross Assembler/Linker/Loader

For details concerning the Lantech cross software development tools, the corresponding user guide [19] should be consulted. To illustrate briefly the application of the Lantech cross assembler/linker/loader, the steps 2 to 4 in Figure 4-3 will be explained using a cross compiled C program named "namel.c" as a general example.

Step 2 assembles assembly source programs written in a syntax which is very similar to the Intel ASM86 assembly language. Unfortunately, complete compatibility has not been achieved. The assembly source program may have been created either by the C cross compiler (Example: "namel.s") or directly by the user (Example: "name2.s"):

"asm86 -1 -o namel.obj namel.s"

- The option -1 generates a listing of the assembly program.

- The option -o is used to have the output named namel.obj

Step 3 in Figure 4-3 resolves references to library routines in the main program. For details on libraries refer to [19]. The cross linker links the main object module with other object modules stored in the link library to form a final object module:

"1kr86 -1 -o namel.exe namel.obj 11ib:1ib8086.a"

- The option -1 is used to list tables of external references.

- The option -o is used to have the output file named to "namel.exe".

- "namel.obj" is the object module of the main program.

- "llib" is the logical name for the library (directory) in which source and object modules of some assembly routines are stored; at present the library only contains the routines necessary to process doubleword operands (corresponds to "long integer" variables in C).

Step 4 in Figure 4-3 determines where in a (simulated) memory the linked object module is to be loaded. The loader reserves two areas in memory: A "Code Block" and a "Data Block". It is important to know that the "Data Block" is reserved for data (global labels, ...) and the stack. The following command invokes the Lantech cross loader:

"ldr86 -1 [-c ...] [-d...] -o namel.hex namel.exe"

- The option -1 generates a listing displaying information about starting addresses and sizes of reserved memory areas. This listing is important as it contains the necessary information for the initialization of the 8086 CPU.

- The -c and -d options allow the user to choose the starting addresses (=hex numbers after -c, -d) of the memory areas to be reserved for program code (-c) and data, stack (-d). If these options aren't used the loader by default loads the program code starting at memory location 1024 (400 hex) and starts the data block at the next paragraph location after the end of the code. A paragraph is an address that is a multiple of 16.

#### 4.1.3. The "OTOL" Program

The "OTOL" ("object to 1.out") program transfers object code from different formats (Motorola, Intel Hex, ...) into the "1.out" format used by N.mPc. For this application the "OTOL" program had to be enhanced as it could not handle the concept of "segmented" memory (see Intel 8086 documentation). The 8086 has four segment registers and addresses its megabyte of address space in 64k byte segments.

With reference to Step 5 of Figure 4-3, the "1.out" formatted files produced by "OTOL" have to be renamed so that the "Simulated Memory Processor" can direct their contents to the appropriate simulated memory. In the example of Figure 4-3, the object version of the "namel.c" program is to be made the initial content of the simulated ROM. Therefore "namel.out", the object version of "namel.c", is renamed "romcore.;" (the name "romcore.;" is declared in the topology file) and

similarly "name2.s" is directed to the simulated RAM by renaming

"name2.out" to "ramcore.;".

Step 5 in Figure 4-3 is executed by the following command:

"otol - id namel.hex namel.out [-a "initrecord"]"

- The i option tells "otol" that the object file to be transferred into "1.out" format is in Intel Hex format.

- The -d option produces a listing of starting addresses of data records.

- "namel.out" is the name assigned to the output file in "l.out" format. The ".out" extension reflects the fact that the file is in the "l.out" format required by N.mPc. The default name of the output file is "l.out".

The "initrecord" option may be used to initialize areas

of memory with certain values.

Other object code formats which can be handled by "OTOL" include:

- Tektronix Hexadecimal;

- RCA Cosmac;

MOS Technology;

- Signetics Absolute Object;

- Fairchild Fairbug.

A short documentation on "OTOL", written by the N.mPc developers is to be found in Appendix G.

Example: "-a2048-3000\$00" initializes the memory locations from 2048 to 3000 with the value 0.

MOTOROLA;

#### 4.1.4. Command Files For The Cross Software Tools

rarely necessary to invoke the As it is cross assembler/linker/loader in a step-by-step fashion, several command files have been created to make the use of the Lantech cross software development tools easier. The command files are located in the "AS86" directory, which is reserved for software development. The name and purpose of each of the two command files currently used with the cross assembler/linker/loader are listed below along with an example for their use:

- 1) "86asmotol.com": This command file invokes the cross assembler/linker/loader and the "OTOL" utility. It uses none of the -c, -d loader options so that the code is loaded starting at address 1024 and the data immediately after the code. Again, the input file is assumed to have a ".s" extension. The output file is given a ".out" extension as it is a file in N.mPc's "l.out" a format. Example: "@86asmotol namel"

- 2) "cOasmotol": This is exactly the same command file as the "86asmotol" but the -c option is used when invoking the loader in order to have the code loaded starting at address 0. (instead of the 1024 default).

Example: "@cOasmotol name1"

NB: If the reader at this point should want to add further to his knowledge of the use of the Lantech 8086 C cross software development tools, the reader is referred to the examples documented in section 6 of the N.mPc User Manual [7].

#### 4.2. Software Development for an actual Intel SBC

The actual hardware used was an Intel 86/30 SBC running iRMX86. The 86/30 SBC is essentially an 86/12 with additional on-board memory and for the purpose of this test can be considered identical to an 86/12 SBC. The test programs for the actual hardware, written in C, were compiled using Intel's C-86 compiler. Appendix C shows the steps to generate the code necessary to execute a test program on the actual Intel SBC hardware.

#### 4.3. Description of the Target Software for the Validation

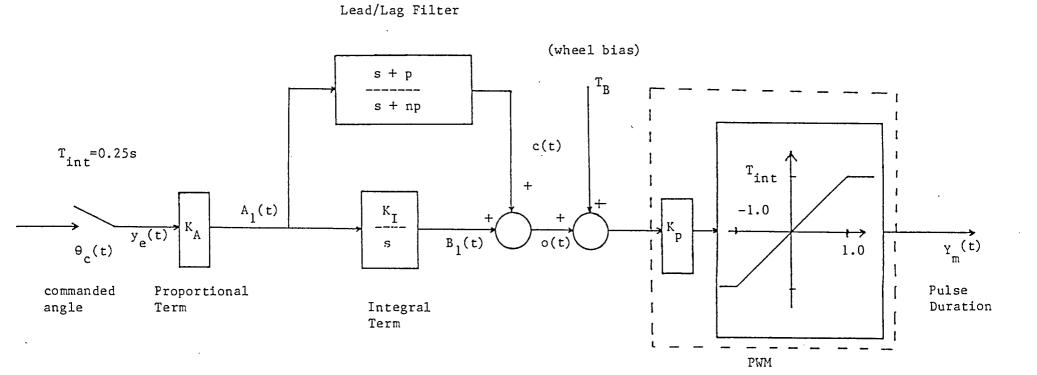

The previous two sections described the software development tools involved when developing test software for the actual and the simulated The test software was to be run on both the actual Intel SBC hardware. and the simulated Intel SBC hardware in order to validate N.mPc's The starting point was microprocessor simulation capabilities. the (SACL) Algorithm" "Simple Attitude Control for choice of а implementation as a test program. Appendix B contains a mathematical of the SACL algorithm and listings of the programs description The SACL algorithm was discretized using the Zimplementing it. transform and implemented as a Fortran program named "SACLZ.FOR". At this point, the fact that SACLZ.FOR used real (floating point) variables had to be taken into account. Floating point variables result in 8087 floating point arithmetic instructions as the C cross compiler assumes the presence of an 8087 math processor. The simulated 86/12 single board computer was not intended to include such mathematical convenience and the alternative was to use "integer" instead of the floating point variables in the SACLZ.FOR program. This resulted in an assembler

program with instructions that could be executed by an 8086 alone. By scaling some variables, an implementation of the SACL algorithm using only integer variables was produced and given the name "SACLZI.FOR". In order to produce a SACL version in C that could be developed on the Lantech cross software development package used with the simulated SBC hardware, SACLZI.FOR was translated into C and called "CMD.C". The fact the Lantech cross software development package did not include an that "ABS" (absolute value) routine in the link library was taken into account by adding an "ABS" subroutine to the "CMD.C" program. this In form, CMD.C can be run on the actual Intel SBC hardware.

It was stated earlier that N.mPc's raw memory feature was to be used in order to simplify I/O operations for simulations. I/0 Two procedures ("IN", "PRINT") have been written in assembly language and added to the link library of the Lantech cross development tools in order to replace the standard I/O procedures ("SCANF", "PRINTF") called The program using the new "IN" and "PRINT" procedures for I/O in CMD.C. simulations is called "VALCMD.C" and can be run on the in N.mPc simulated 86/12 hardware using the Lantech cross software development As VALCMD.C uses "long integer" variables, the 8086 CPU has to tools. handle double word operands. The necessary assembly language routines are contained in the link library which is part of the Lantech Cross Listings of the two assembly routines used to perform software tools. the I/O for the validation simulation are found in Appendix I. The total size of the validation code amounts to 1680 bytes which is very considerable in an N.mPc simulation context. This code corresponds to about 300 8086 instructions or a C program of about 40 lines.

The steps to build the simulation of an Intel 36/12 SBC and to run the validation testprogram ("VALCMD.C") on the simulated hardware are shown in detail in Appendix D. How to run the intermediate programs ("SACLZ.FOR", "SACLZI.FOR") produced when developing the validation testprogram ("VALCMD.C") is also indicated in Appendix D.

#### 5. VALIDATION/TEST PROCEDURES

In the case of the actual Intel SBC hardware it was very easy to run the validation testprogram as the 86/30 SBC is running the iRMX86 operating system. Appendix C shows that the actual running of the validation testprogram CMD.C (here named "CMVALID.C86") is done by a single command.

In the case of the simulated 86/12 SBC hardware things are not so easy. The user has to initialize some registers of the 8086 CPU in order to have the 8086 start executing at the beginning of a program and to set up a stack and data area in memory. The use of the Lantech cross software development tools introduces a restriction for the initialization of the 8086 which will be discussed in detail.

The Lantech 8086 C cross software development tools are intended to develop software to be run on hardware consisting of an 8086 CPU and an 8087 math processor. In usual applications one just develops the software in high level language and the operating systems of the host and target systems will take care of everything else. In an N.mPc simulation, there is no operating system on top of the simulated hardware so that the user has to initialize the simulated hardware before he runs a program. The initialization of a simulated 8086 CPU serves the following purposes:

- It sets the instruction pointer (ip) and the code segment register (cs) to point to the starting address of the code.

- 2) It places the data area and the stack area appropriately into the data block reserved in memory by the loader. The Lantech cross software development tool requires that the 8086 stack and data segment registers be initialized with the same value.

To perform a proper initialization of the 8086 CPU one has to remember the following loading information from the previous development steps:

i) the address where the loaded program starts

ii) the beginning and the end of the common memory block reservedby the loader for the data and stack areas

In order to determine those values one has to look at the listing produced by the cross loader when using the -l option and find the starting addresses and sizes of code and data blocks. The end of the reserved memory area is verified by inspecting the corresponding simulated memory when the simulation is in runtime mode. The following example was made up to illustrate the initialization procedure discussed above.

1) Information from the cross loader (obtained when the -1 option was used with cross loader):

- The program code block starting address is 400 hex (=1024).

- The data block starting address is 470 hex (=1136), the end of the reserved memory area is found at 600 hex (=1536). Memory areas not reserved by the loader are characterized by an "illegal memory access" message when being inspected. Use the "initrecord" option in 0T0L to reserve a bigger memory space (see section 4.1.3).

- 2) Program counter initialization:

- Set the combination of instruction pointer (ip) and code segment register (cs) to the starting address of the code block.

etc ...

3) Data segment, stack segment initialization:

- It should be noted that the Lantech 8086 C cross software development tools do not make any distinction between stack segment and data segment; the starting addresses of stack and data segments have to be identical which means that the "ds" and "ss" segment registers have to be initialized with identical values (see [19], page 3-6).

- Have the data and stack segment registers (and the extra segment register if it is used) point to the starting address of the data block: - "deposit 0x47 :ds"

- "deposit 0x47 :ss"

(- deposit 0x47 :es) (if "es"

#### used)

- The stack grows downwards from its top; it is therefore reasonable to put the top of the stack near or at the end of the memory block reserved for data and stack by initializing the stack pointer with an appropriate value. Example: - (end of reserved stack, data memory area its base address) = 600 hex - 470 hex =

190 hex: "deposit 0x190:sp"

The initialization information as well as all the other essential

information about all "ready-to-run" simulations is found in the "Oreadme.fst" textfiles put into each simulation directory.

The step by step description of how to build and run the validation testprogram "VALCMD.C" on simulated 86/12 SBC hardware is found in Appendix D. The execution of the testprogram ("SIEVE.C") on the actual Intel SBC hardware is handled in a similar fashion to the execution of the validation testprogram shown in Appendix C.

With the exception of the initialization step, the execution of the "sieve.c" test is also analoguous to the execution of the validation testprogram. The "OREADME.FST" textfile in the simulation directory (86sieve) describes how to carry out the performance test.

#### 6. COMPARISON OF SIMULATION AND ACTUAL RESULTS

#### 6.1. Interpretation of the Validation Results

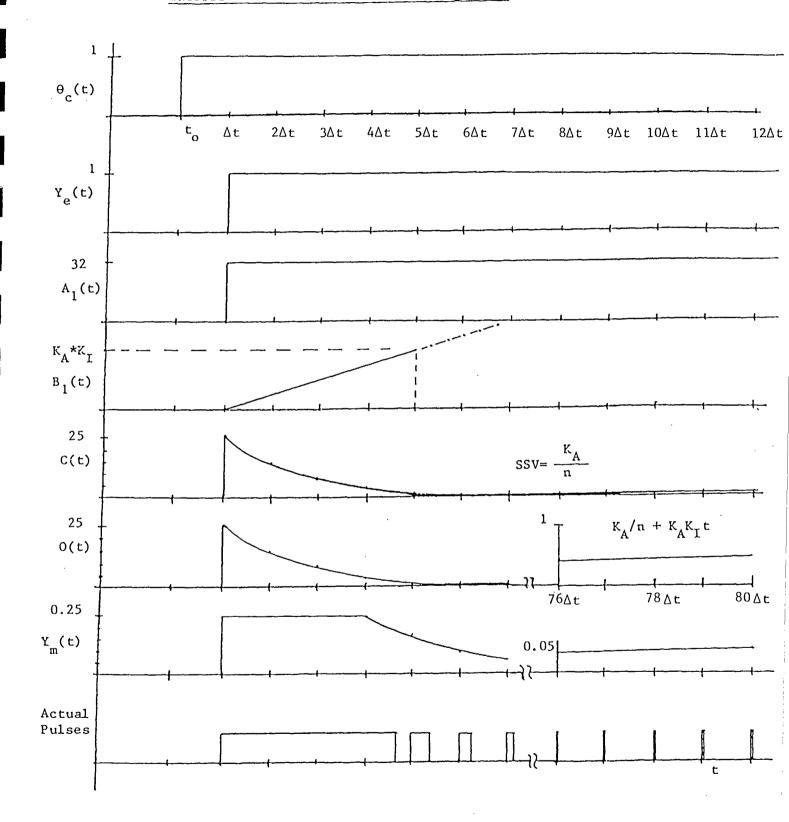

Figures 6-la and 6-lb show the input and the output produced by running the validation testprogram ("VALCMD.C", see Appendix B) on the simulated 86/12 single board computer. The validation of N.mPc as a CAE tool for microprocessor simulations is done by comparing these results to the ones produced when "CMD.C" (or "HEXCMD.C") is run on the actual Intel SBC hardware. The program "CMD.C" only differs from "VALCMD.C" in the routines used for I/O operations. The results are identical if identical "angles" are entered by the user when running "CMD.C" on the simulated hardware or "CMD.C" (or "HEXCMD.C" for output in hex numbers ) on the actual Intel SBC hardware. Figures 6-2a and 6-2b show the results obtained when running "HEXCMD.C" (see Appendix B) on an actual Intel 86/30 SBC using the same input angle as the one used to produce the simulation output shown in Figures 6-la and 6-lb.

Thus the validation testprogram, written in the high level language C; and implementing a discrete, scaled version of the "Simple Attitude Control Algorithm" (SACL), was developed and run on both simulated and actual Intel SBC hardware, producing identical results.

she def USER & DISKI: CICLI.NHCC.READYSIN.86VAL) See val run val Welcome to N.mfc/VHS Himfe: val den 1024 ::= der Oxaa iss den Oxaa ids der 280 15+ 1 14 MAX 11:45:34 VAL CFU=00:00:31.97 FF=1924 10=2421 HEH=307 Enter angle(degrees/2 digits):01 01 0000 0000000 0000000 0000 0000 0000 0001 00000020 00000004 6451 6451 1600 0002 00000020 00000000 3013 3003 1600 0003 00000020 00000014 2522 2522 1600 0004 00000020 0000001C 16EB 16EB 1600 0005 00000020 00000024 0664 0664 0664 0006 0000020 0000020 0946 0946 0946 0007 00000020 00000034 0635 0635 0635 0008 00000020 000003C 045E 045E 045E 0009 00000020 00000044 0344 0344 0344 000A 00000020 0000004C 0298 0298 0298 000B 00000020 00000054 0236 0236 0236 000C 00000020 0000005C 01F9 01F9 01F9 0000 00000020 00000064 0105 0105 0105 0006 00000000 0000006 0100 0100 0100 000F 00000020 00000074 0184 0184 0184 0010 00000020 0000007C 01AD 01AD 01AD 0011 00000020 00000084 01A9 01A9 01A9 0012 00000020 000008C 01A7 01A7 01A7 0013 00000020 00000094 0146 0146 0146 0014 00000020 0000009C 01A5 01A5 01A5 0015 00000020 00000044 0146 0146 0146 0016 00000020 000000AC 01A6 01A6 01A6 0017 00000020 00000084 01A7 01A7 01A7 0018 00000020 000000RC 01A7 01A7 01A7 0019 0000020 00000C4 01A8 01A8 01A8 001A 00000020 000000CC 01A9 01A9 01A9 0018 0000020 00000004 01AA 01AA 01AA 001C 00000020 0000000C 01AA 01AA 01AA 0010 00000020 000000E4 01AB 01AB 01AB 001E 00000020 000000EC 01AC 01AC 01AC 001F 00000020 000000F4 01AD 01AD 01AD 0020 00000020 000000FC 01AE 01AE 01AE 0021 00000020 00000104 01AE 01AE 01AE 0022 00000020 0000010C 01AF 01AF 01AF 0023 00000020 00000114 0180 0180 0180 0024 00000020 00000110 0181 0181 0181 0025 00000020 00000124 0182 0182 0182 0026 00000020 00000120 0182 0182 0182

....

Figure 6-1b: Running the Validation Program on the Simulated 86/12

| run hexcmd<br>Enter the commanded andle                                  |

|--------------------------------------------------------------------------|

| 1 0 0 0 0 0 0                                                            |

| 1 20 4 6451 6451 1600<br>2 20 c 3cd3 3cd3 1600                           |

| 3 20 14 2522 2522 1600<br>4 20 1c 16eb 16eb 1600                         |

| 5 20 24 e64 e64 e64<br>6 20 2c 946 946 946                               |

| 7 20 34 635 635 635<br>8 20 3c 45c 45c 45c                               |

| 9 20 44 344 344 344<br>a 20 4c 29b 29b 29b                               |

| b 20 54 236 236 236<br>c 20 5c 1f9 1f9 1f9                               |

| d 20 64 1d5 1d5 1d5                                                      |

| 1 20 74 164 164 164                                                      |

| 10 20 7c 1ad 1ad 1ad<br>11 20 84 1a9 1a9 1a9                             |

| 12 20 8c 1a7 1a7 1a7<br>13 20 94 1a6 1a6 1a6                             |

| 14 20 9c 1a5 1a5 1a5<br>15 20 a4 1a6 1a6 1a6                             |

| 16 20 ac 1a6 1a6 1a6<br>17 20 b4 1a7 1a7 1a7                             |

| 18 20 bc 127 127 127<br>19 20 c4 128 128 128                             |

| 1a 20 cc 1a9 1a9 1a9<br>1b 20 d4 1aa iaa iaa                             |

| ic 20 de laa laa laa<br>id 20 e4 lab iab lab                             |

| ie 20 ec lac lac lac<br>if 20 f4 iad iad iad                             |

| 20 20 fc lae lae lae<br>21 20 104 lae lae lae                            |

| 22 20 10c 1af 1af 1af<br>23 20 114 1b0 1b0 1b0                           |

| 24 20 11c 1b1 1b1 1b1<br>25 20 124 1b2 1b2 1b2                           |

| 26 20 12c 1b2 1b2 1b2<br>27 20 134 1b3 1b3 1b3                           |

| 28 20 13c 164 164 164<br>29 20 144 165 165 165                           |

| 2a 20 14c 166 166 166<br>26 20 154 166 166 166                           |

| 2c 20 15c 1b7 1b7 1b7<br>2d 20 164 1b8 1b8 1b8                           |

| 2e 20 16c 1b9 1b9 1b9<br>2f 20 174 1ba 1ba 1ba                           |

| 30 20 17c 1ba 1ba 1ba<br>31 20 184 1bb 1bb 1bb                           |

| 32 20 18c 1bc 1bc 1bc<br>33 20 194 1bd 1bd 1bd                           |

| 34 20 19c 1be 1be 1be<br>35 20 1a4 1be 1be 1be                           |

| 36 20 1ac 1bf 1bf 1bf<br>37 20 1b4 1c0 1c0 1c0                           |

| 38 20 1bc 1c1 1c1 1c1<br>39 20 1c4 1c2 1c2 1c2                           |

| 3a 20 1cc 1c2 1c2 1c2<br>3b 20 1d4 1c3 1c3 1c3                           |

| 3c 20 1dc 1c4 1c4 1c4<br>3d 20 1e4 1c5 1c5 1c5                           |

| 3e 20 lec 1c6 1c6 1c6<br>3f 20 lf4 1c6 1c6 1c6                           |

| 40 20 1fc 1c7 1c7 1c7<br>41 20 204 1c8 1c8 1c8                           |

| 42 20 20c 1c9 1c9 1c9<br>43 20 214 1ca 1ca 1ca                           |

| 44 20 21c 1ca 1ca 1ca<br>45 20 224 1cb 1cb 1cb                           |

| 46 20 22c 1cc 1cc 1cc<br>47 20 234 1cd 1cd 1cd                           |

| 48 20 23c ice ice ice<br>49 20 244 ice ice ice                           |

| 47 20 244 100 100 100<br>48 20 24c 1cf 1cf 1cf<br>.45 20 254 1d0 1d0 1d0 |

| 4c 20 25c 1d1 1d1 1d1                                                    |

| 4e 20 26c 1d2 1d2 1d2                                                    |

| 4f 20 274 1d3 1d3 1d3<br>50 20 27c 1d4 1d4 1d4                           |

|                                                                          |

:

Figure 6-2a: Running the Validation Program on the actual Intel SBC Hardware (output in hex)

\$

| run end                                                                 |   |

|-------------------------------------------------------------------------|---|

| Enter the commanded angle                                               | : |

| 0 0 0 0 0 0<br>1 32 4 25681 25681 5632                                  |   |

| 2 32 12 15571 15571 5632<br>3 32 20 9506 9506 5632                      |   |

| 4 32 28 5867 5867 5632                                                  |   |

| 5 32 36 3684 3684 3684<br>6 32 41 2374 2374 2374                        |   |

| 7 32 52 1589 1589 1589<br>8 32 60 1118 1118 1118                        |   |

| 9 32 68 836 836 836<br>10 32 76 667 667 667                             |   |

| 11 32 84 566 566 566<br>12 32 92 505 505 505                            |   |

| 13 32 100 469 469 469<br>14 32 108 448 448 448                          |   |

| 15 32 116 436 436 436                                                   |   |

| 16 32 124 429 429 429<br>17 32 132 425 425 425                          |   |

| 18 32 140 423 423 423<br>19 32 148 422 422 422                          |   |

| 20 32 156 421 421 421<br>21 32 164 422 422 422                          |   |

| 22 32 172 422 422 422<br>23 32 180 423 423 423                          |   |

| 24 32 188 423 423 423<br>25 32 196 424 424 424                          |   |

| 26 32 201 425 425 425                                                   |   |

| 27 32 212 426 426 426<br>28 32 220 426 426 426                          |   |

| 29 32 228 427 427 427<br>30 32 236 428 428 428                          |   |

| 31 32 244 429 429 429<br>32 32 252 430 430 430                          |   |

| 33 32 260 430 430 430<br>34 32 268 431 431 431                          |   |

| 35 32 276 432 432 432<br>36 32 281 433 433 433                          |   |

| 37 32 292 434 434 434<br>38 32 300 434 434 434                          |   |

| 39 32 308 435 435 435<br>40 32 316 436 436 436                          |   |

| 41 32 324 437 437 437<br>42 32 332 438 438 438                          |   |

| 43 32 340 438 438 438<br>44 32 348 439 439 439                          |   |

| 45 32 356 440 440 440<br>46 32 364 441 441 441                          |   |

| 47 32 372 442 442 442<br>48 32 380 442 442 442                          |   |

| 49 32 388 443 443 443                                                   |   |

| 50 32 396 414 444 444<br>51 32 404 445 445 445                          |   |

| 52 32 112 116 116 146<br>53 32 120 146 146 146                          |   |

| 54 32 128 117 117 117<br>55 32 136 118 118 118                          |   |

| 56 32 444 449 449 449<br>57 32 452 450 450 450                          |   |

| 58 32 460 450 450 450 .<br>59 32 468 451 451 451                        |   |

| 60 32 176 152 152 152<br>61 32 484 153 153 153                          |   |

| 62 32 492 154 151 154<br>63 32 500 154 454 454                          |   |

| 64 32 508 455 455 455<br>65 32 516 456 456 456                          |   |

| 66 32 524 457 457 457<br>67 32 532 458 458 458                          |   |

| 68 32 540 458 458 458<br>69 32 548 459 459 459                          |   |

| 70 32 556 460 460 460<br>71 32 564 461 461 461                          |   |

| 71 32 389 481 481 481<br>72 32 572 462 462 462<br>73 32 580 462 462 462 |   |

| 74 32 588 463 463 463                                                   |   |

| 75 32 596 161 164 464<br>76 32 604 165 165 165                          |   |

| 77 32 612 466 466 466<br>78 32 620 466 466 466                          |   |

| 79 32 628 467 467 467<br>80 32 636 468 468 468                          |   |

| •                                                                       |   |

Figure 6-2b:

Running the Validation Program on the actual Intel SBC Hardware (output in decimal) ٢.,

### 6.2. Performance of Simulated and Real Hardware

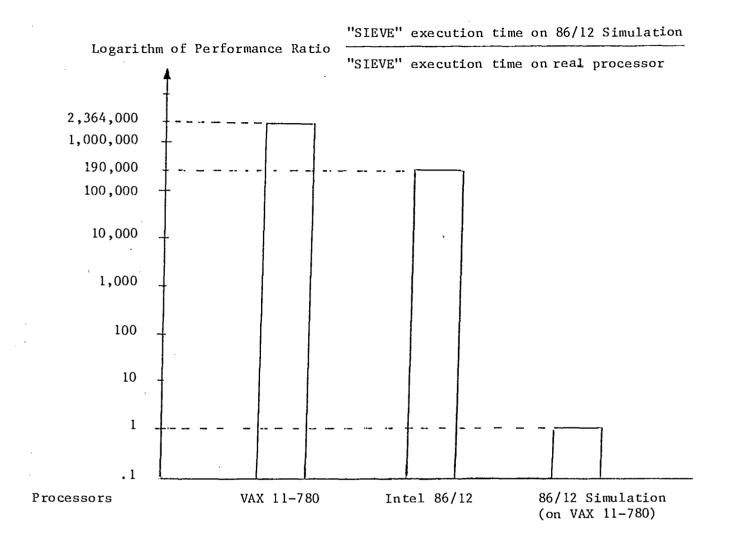

As another application for the high level software capabilities of the 86/12 simulation developed during this work, it was decided to run performance tests using a high level benchmark program in C. This program could be run on any machine equipped with a C compiler. The machines being compared in this case were the VAX 11-780, the iSBC 86/12 single board computer and a simulation of the 86/12 using N.mPc on the To get reasonable and measurable execution times for the VAX 11/780. "sieve" benchmark, the program was executed 100,000 times on the VAX and on the 86/12 while one single execution of the "sieve" on the 86/12 simulation was sufficiently long. The factor 100,000 was later taken into account when comparing the relative performance of each processor. The "sieve" benchmark uses the "long integer" data type for variables on all three machines. The execution times on the VAX were measured in CPU The details about how the "sieve" benchmark was run on different time. machines are to be found in Appendix D.2. The performance comparison of real machines to a simulated one shows of course a significant performance penalty due to the simulation overhead. The following execution times were measured when running the "sieve" benchmark:

- VAX 11/780 : 17 sec. for 100,000 runs of "sieve"

- iSBC86/12 : 211 sec. for 100,000 runs of "sieve"

- Simulation of the iSBC 86/12 using N.mPc on a VAX 11-780: 402 sec. for one run of "sieve"

Expressed in performance ratio (P for Performance) this means:  $P_{VAX}$  : P<sub>8612</sub> : P<sub>Simulation 8612</sub>  $\approx$  2,364,000 : 190,000 : 1

Figure 6-3 shows the same results in a graphical form. These performance comparisons only serve to get a notion of the order of magnitude of the performance penalty caused by the N.mPc simulation overhead and do not claim to be exact as compiler differences may influence the results. See Appendix D or the "readme" file in the "86sieve" directory for details on the performance comparisons.

Performance Penalty due to Simulation using N.mPc

•••••

## 7. SUMMARY AND CONCLUSIONS

The following is a summary of the main results of the study presented in this report:

- A simulation of an Intel iSBC 86/12 single board computer was performed successfully. It included an 8086 CPU, a dual port RAM, a ROM, a programmable interrupt controller (PIC), a Multibus interface, a global memory and an I/O facility based on N.mPc's "raw memory" feature. These modules were designed and thoroughly tested and debugged during the course of the work.

- The program "OTOL" was used to transfer object code produced by the cross compiler to the "l.out" format needed by N.mPc. The program was subsequently upgraded in order to handle code intended to be run on an 8086 CPU. This made it possible to do software development for the 86/12 simulation in the high level language "C", using the C 8086 cross software development tools by Lantech Inc.

- The validation of N.mPc as a CAE tool for microprocessor simulations was performed by implementing a "Simple Attitude Control Algorithm" as a "C" program, which was successfully run on the simulated 86/12 single board computer as well as on the actual Intel SBC hardware. The validation not only established the reliability of the simulated hardware but also demonstrated the I/O capabilities of the 86/12 simulation. The development of the validation program in "C" demonstrated the potential of the high level software development path introduced as a result of this work.

The work reported in this document was an opportunity to acquire considerable expertise with the CAE tool N.mPc. As a result, it has

been felt that N.mPc is in fact a valuable tool in the development of a computer system.

For the case of the Intel 86/12 simulation the following observations were felt to be strong points of the CAE tool N.mPc:

- The design of the hardware modules of the simulation of the 86/12 SBC showed N.mPc's flexibility; making hardware changes due to new requirements or correcting design errors could be performed easily and efficiently.

- The debugging of the description of the 8086 CPU demonstrated the power of N.mPc's monitoring, control and debugging features which allow the tracing of errors in hardware descriptions.

- This work showed the feasibility of a high level language software development for N.mPc microprocessor simulations.

- The major effort of writing a hardware description of the 8086 CPU could be reduced by using a description from the library of descriptions of existing microprocessors (this library was delivered with the N.mPc system).

The following observations are based upon the 86/12 simulation work and outline some difficulties experienced with N.mPc:

- The C programs which were executed on the simulated 86/12 SBC were limited to be of a moderate size. This restriction was due to the simulation performance penalty resulting from the simulation overhead.

- Errors in the 8086 CPU description from the N.mPc's microprocessor description library required a considerable debugging effort. Just as the testing of VLSI chips is a major

problem of today's semiconductor industry, the same problem occurs in N.mPc descriptions of complex hardware modules. As in all software endeavours, the larger the programs one can run successfully, the more confidence one can have in a microprocessor description, for example. At the present time, there is no straightforward, systematical way to find all the possible bugs in a complex hardware description.

The VMS version of the N.mPc run-time environment behaved strangely, at times, when faced with some subtle hardware description errors. The result was a catastrophic exit to VMS which left one unable to ascertain the cause of the failure systematically.

Some general conclusions can be drawn from the experience gained during the work documented in this report. Some of the strong points of a design approach using computer aided design tools such as N.mPc are listed below:

-

N.mPc introduces the inherent flexibility of software into hardware design.

- Complex computer systems can quickly be simulated by taking a few hardware descriptions from a library and "interconnecting" them in a topology file.

- N.mPc separates the logical hardware design problems from the technical ones (timing, etc.) so that they can be solved separately.

- N.mPc not only offers an entirely programmable software development environment for microprocessor simulations but also allows to use of commercial cross software development

packages. These packages make it possible to develop software for microprocessor simulations in a high level language.

Of course, the advantages gained by the use of CAE tools come at a price:

- The performance penalty paid by N.mPc microprocessor simulations is significant and clearly limits the size of software to be run on a simulated processor. This simulation performance penalty will be alleviated by the ever increasing performance and decreasing cost of host computer systems.

- N.mPc's library of hardware descriptions should be improved in order to contain descriptions of existing hardware elements (microprocessors, etc.) with a reliability that is similar to the actual hardware. The hardware designer using the N.mPc could then directly use these descriptions without having to worry about debugging.

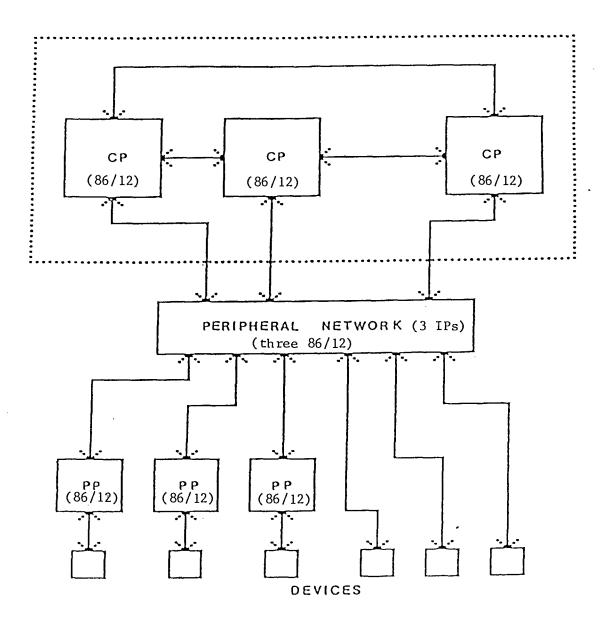

It is interesting to note that the design of a fault tolerant computer architecture for space applications (see Figure 7-1) was part of the work done under this contract. In that section of the work, a fault tolerant multiprocessor architecture was developed and it was decided to simulate the operations of such an architecture with N.mPc. The 8086 CPU was chosen as the generic processor for the elements of the multiprocessor system. N.mPc makes possible the simulation of several 8086 based processing elements at a very low incremental effort. This is where a CAE tool like N.mPc really shows its inherent power.

CP = Central Processor

IP = Interface Processor

PP = Peripheral Processor

Figure 7-1: Fault Tolerant Computer Architecture

#### REFERENCES

- [1] Ordy, G.M., "N.mPc: Runtime User's Manual," Department of Computer Engineering and Science, Case Western Reserve University, 1979.

- [2] Ordy, G.M. and Rogers, L.A., "N.mPc: MetaMicro User's Manual," Department of Computer Engineering and Science, Case Western Reserve University, 1979.

- [3] Rogers, L.A., "N.mPc: Linking Loader User's Manual," Department of Computer Engineering and Science, Case Western Reserve University, 1979.

- [4] Ordy, G.M., "N.mPc: Ecologist User's Manual," Department of Computer Engineering and Science, Case Western Reserve University, 1979.

- [5] Leffler, S.J., "PP: A Post-Processor for N.mPc," Department of Computer Engineering and Science, Case Western Reserve University, 1979.

- [6] Rogers, L.A., "A Generalized Linking/Loader for the Allocation of Code in Vertical and Horizontal Machines," Master of Science Thesis, Department of Computer Engineering and Science, Case Western Reserve University Report CES-79-6, August 1978.

- Streit, M., "VAX 11-780 CAE Tools for Multiprocessor Simulation: N.mPc User's and Application Manual and Installation Guide", a Report prepared by Intellitech, September 1984.

- [8] Streit, M., "Simulation of the SBP 9989 Microprocessor Using the Computer Aided Engineering Tool N.mPc on a VAX 11/780", a Report prepared by Intellitech, September 1984.

- [9] Parke, F.I., "An Introduction to N.mPc Design Environment", Proceedings of the ACM/IEEE Design Automation Conference, June 1979.

- [10] Rose, C.W., Rogers, L.A., and Straubs, R.V., "The N.mPc System Description Facility," Proceeding of ACM/IEEE Design Automation Conference, June 1979.

- [11] Hewitt, D.C., Parke, F.I., and Rose, C.W., "The N.mPc Runtime Environment," Proceedings of the ACM/IEEE Design Automation Conference, June 1979.