#### VOLUME 2

### TIME SHARED SYSTEMS HARDWARE

- Memory Hierarchy Management -

by

John deMercado

Terrestrial Planning Branch

June 1972

QA 00, 76.53 D44 V.2 19.76

VOLUME 2

Industry Canada Library Queen.

JUL 2 9 1998

Industrie Canada Bibliothèque Queen

### TIME SHARED SYSTEMS HARDWARE

- Memory Hierarchy Management -

by

John deMercado

Terrestrial Planning Branch

June 1972

4 Dart 2 Jp. 23 Obs .

### Acknowledgements

The purpose of these notes is to promote dialogue within the Terrestrial Planning Branch and serve as a basis for our computer-communication systems implementation program.

The notes are only in first draft form and borrow heavily from the references. They should be read in conjunction with the attached reference papers.

As a revised version is planned the author would appreciate any corrections or omissions in the text that were brought to his attention. He also wishes to thank Messrs. John Harris, S. Mahmoud and Kalman Toth for their valuable contributions.

Miss Gail Widdicombe and Miss Yollande Chartrand typed them in record time from an almost unreadable handwritten manuscript.

Introduction

Memory System Design Problems

Addressing and Allocation

Static Relocation

Dynamic Relocation Using Base Registers

Dynamic Relocation Using Paging

Memory Maps

Segment Concepts

Communications within the Time Shared Computer

Communication with the Main Memory

Memory Management Software - Storage Hierarchies

Modelling - Working Set Replacement Algorithm

References (attached)

- 1. W.W. Chu, N. Oliver and H. Opderbeck, "Measurement Data on the Working Set Replacement Algorithm and Their Applications".

- 2. R.L. Mattson, J. Gecsei, D.R. Dlutz and I.L. Traiger, "Evaluation Techniques for Storage Hierarchies",

- 3. Gerald H. Fine, et al, "Dynamic Program Behavior under paging".

General References.

### Introduction

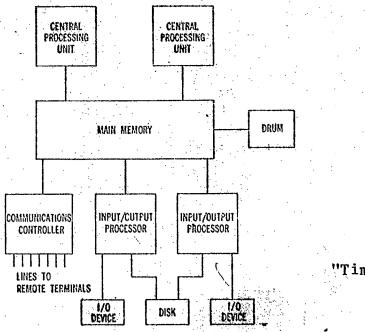

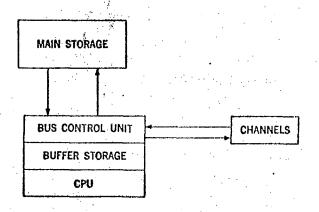

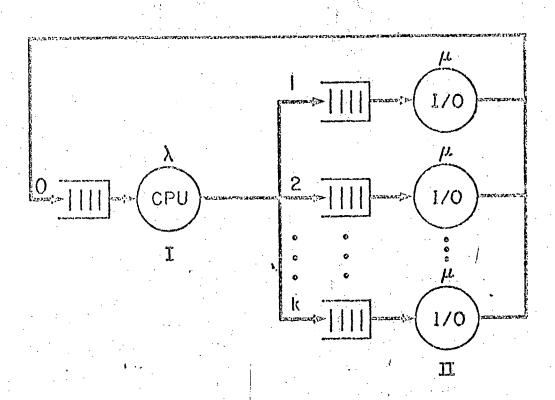

The intent of these notes is to briefly review the features of the hardware required for effective memory hierarchy management in time sharing systems. The time shared systems will have the general architectures as shown in Figure 1 below.

"Time Shared System"

Figure 1

The major hardware features required by such systems are:

- protection mechanisms to help safeguard one process from another and the system from itself and user processes and:

- mechanisms which contribute to efficient dynamic allocation of resources.

- high reliability.

## Memory-system Design Problems

The central resource in current systems is the main memory. This main memory holds the instructions for the arithmetic-logic processors (CPU's) and for the I/O processors (IOP's).

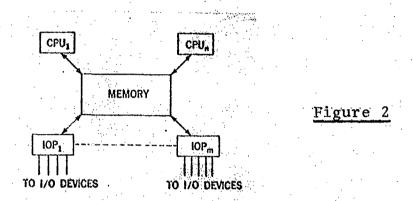

It also serves as the buffer for information passing over communication lines and between various I/O and secondary storage devices, and stores the code for the resident operating system. It goes without saying that the proper design of the memory system is critical to the success of a large scale time-sharing system. Figure 2 shows the memory centered model of a computer system which shows the memory as the control resource.

## Addressing and Allocation

Main-memory devices have multiplexing properties that must be considered in order to specify an appropriate addressing and allocation scheme for a timeshared computer. While any portion of main memory can be dedicated to a process. Processors themselves can be allocated only as units. Processors, however, can be multiplexed rapidly, while main memory cannot. This time is required to move information between main and auxiliary memory. This moving of processes between main memory and auxiliary storage in order to multiplex main memory is called <a href="mainto:swapping">swapping</a>.

A requirement in the design of an addressing scheme for a timeshared computer is that it should maximize the allocation advantages of memory and minimize the multiplexing disadvantages. For example, it is preferable to have only one copy of a particular procedure, say a compiler, in main memory that can be shared by several processes rather than have each process obtain a separate copy. Programs designed to be shared by several processes are called reentrant programs or pure procedures. A reentrant program has two characteristics:

- none of its instructions or addresses can be modified during its execution,

- temporary storage and data areas are maintained outside the procedure itself, usually in the memory space of the calling programs.

Although re-entrant programs can be written for machines with a wide variety of addressing techniques, certain addressing techniques can make the writing and protection of these programs simpler.

Memory can effectively be utilized by achieving flexibility with respect to where processes can be placed in physical memory. This ability to relocate processes dynamically in physical memory is by a variety of addressing and allocation techniques.

The cost of designing and implementing application systems, as well as the treatment of certain classes of problems - is to be affected by the properties of the addressing and allocation scheme. The various tradeoffs in the design of an addressing and allocation system must take into account both user needs and system considerations. A designer must decide whether the logical-address space is going to be smaller, the same size or larger than the physical-address space. The structure of the logical-address space must also be determined. Many structures are possible,

e.g., the large linear array commonly used, a set of linkable linear arrays, as found in Multics, or a tree structure. It must be decided how much of this structuring to perform in hardware and how much in software. The technique of translating or mapping the logical addresses to physical addresses must be determined. Present systems perform this mapping at three points, namely

When the procedure is prepared as an operable computer program; the result is an absolute program, which, in effect, is assigned the same resources each time it is run.

When the program is loaded; this is known as static relocation.

When the program is in execution; this is called dynamic relocation.

Usually only linear arrays or sets of linear arrays are considered as forms of hardware memory structures, because more specialized structures, such as trees, lists, or rings, are usually left for implementation by software processors.

# Static Relocation

The translation of data references to physical addresses is easily accomplished during program preparation but suffers from the severe problems which arise when one attempts to share or modify programs. For example, if one inserts an instruction into a program, all references to instructions and data beyond the point of insertion must be updated.

Similarly when one constructs a program out of routines prepared independently, the address references must be modified to reflect the locations into which the routines are loaded. Further, translation at that time restricts the size of the logical-address space to that of the physical-address space.

The process of static relocation involves a fair amount of computation. In systems using static relocation, programs are usually assembled as if they were to be loaded with the first instruction at location zero, with succeeding instruction and data words being placed in contiguous cells from this point. The location of the first word of the program is called the base address. All instructions or data words with address references are marked by the assembler. Then at load time, a program called the loader adjusts all address references to reflect the actual base address at which the program was loaded. If several programs assembled independently are to be loaded as a unit, the loader, using information supplied by the assembler, adjusts the interprogram address references to reflect the actual locations of the different programs. This process is called linking.

With static relocation, a user can be initiaely loaded anywhere in memory. However, when the process is removed to auxiliary storage and then returned during swapping, it must be placed in the same locations as before, to avoid the loading process. (Furthermore, to go through the loading process again implies that the program must be separable into a pure procedure part and a data part and that the data part must contain no absolute-memory addresses.) The major gain of static relocation is that during the loading process independtly written programs and data can be combined into a computation with proper linking of parts. The proper

mapping to the physical-address space is performed by the loader. Each program can be written in a logical space of its own, but no duplication of symbolic location names is allowed, although programming techniques can be developed to resolve such duplication.

The ability to load programs anywhere in physical memory is useful in the linking process above but of little value in achieving effective memory utilization in a timeshared system. For example, when a new process is to be started, the system can attempt to find a process which would fit in an available block of cells. If such a process can be found and it can remain in main memory until completion, static relocation is sufficient to enable several processes to share main memory. (The assumption of some sort of memory-protection scheme is implicit;) A more usual situation will be that the total number of free cells available is sufficient for the number required by a new process but that these cells are not in a contiguous block.

If swapping is required, then even if a contiguous block were available on initial loading, the same contiguous block will not necessarily be available each time the process is run, without moving some information to another aspot in main memory or moving it to secondary storage. For these reasons, systems without dynamic-relocation hardware, when used for timesharing, generally have allowed only one complete process to reside in memory at a given time. Thus, during the swapping operation, the system must remain idle. It is this situation which motivated the development of dynamic-relocation methods.

### Dynamic Relocation Using Base Registers

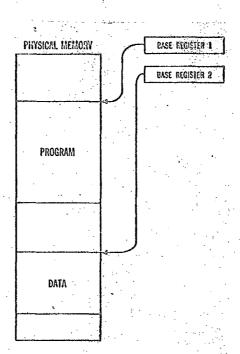

One of the simplest and most common dynamic-relocation techniques uses base registers, which are registers that can have their contents added to the address of each memory operation. By adding the contents of a base register to all addresses, one can load a program anywhere in memory in a block of contiguous cells and then set the appropriate base address of the program into the base register. Using base registers, programs are initially loaded using static-relocation techniques but can be dynamically relocated as a unit later without going through the loading process. This flexibility results because the loading is to logical space not physical space. The base registers form a hardware map which maps logical space to physical space. Further flexibility is gained if there is more than one base register, which facilitates sharing programs and makes it possible to split a program for loading into noncontiguous storage areas.

There are many possible variations of the base-register In fact, techniques such as segmentation technique. are implemented using some hardware registers called base registers. Here, we are only interested in the concept of base registers in its simplest form as defined above and illustrated in Figure 3 below. There are two common ways of specifying which base register to use in forming an address. One technique, represented by the IBM System 360, requires the base registers to be directly addressed by the program and allows the program to access the base registers. The second technique, represented by the UNIVAC 1108, does not allow programs to access the base registers and implicitly addresses the base registers depending on the type of memory operation being executed. For example, all instruction fetches use one base register and all data fetches and stores use another base register.

Program sharing is performed in a system using base registers by writing the reentrant programs to make memory references to themselves through one base register and to make memory references to data in the calling process through a second base register.

### Figure 3

Two base registers used for dynamic relocation of program and data.

## Size of Logical Space

The size of the logical-address space using static relocation or dynamic relocation with base registers is usually equal to or less then the size of the physical-address size. A larger physical space can be simulated by the user by explicitly overwriting a portion of his computation not immediately required with another part brought in from auxiliary storage. This process is called overlaying. Overlaying is closely related to the concept of swapping except that overlaying is a user responsibility whereas swapping is a system responsibility.

#### Memory Utilization

One of the problems uncovered by static relocation is the fact that, once loaded, a process's address references are bound to a certain contiguous area of memory and that during swapping the process must be returned to the same area of main memory each time it is given control of the physical processor. When base registers are used, this restriction no longer holds. When the processor is to be switched to a process not in main memory, a free contiguous block of main memory must be found for it to reside in. If such a block exists, no information need be saved on auxiliary memory in order to make room for the incoming process. The more usual situation results when although enough free cells are available in main memory for the process, they are not in a large enough contiguous block. In this case, a system designed to use base registers can do three things:

- search for a process which will fit into one of the available contiguous blocks,

- swap out part of some process presently in main memory bordering on a free area in order to make a large enough contiguous area, or

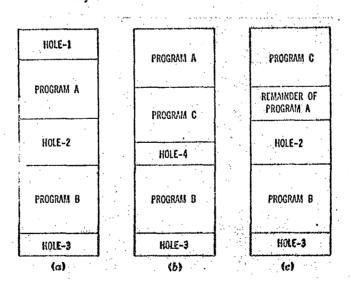

- perform a compacting operation on main memory. Figure 4 illustrates the last two ideas.

Figure 4a shows memory at a given point in time. There are two programs entirely residing in memory and three free-space areas (holes). It is desired to bring into memory a third program C which is larger than individual holes but smaller than total space available in holes 1 and 2. Figure 4b shows one approach to making enough space available to fit in program C. Program A is moved entirely to start

at the beginning of memory, thus creating enough free space for program C. Figure 4c shows another way of making enough space available to fit in program C. Enough of program A bordering on hole 1 is removed to auxiliary storage to make room for program C.

One solution to the problem of finding a large enough contiguous area might be to use multiple base registers so that smaller pieces of the process could be loaded into existing free spaces. This approach seems to be impractical because the instructions of a given pièce must refer to the correct base register. Thus, the programmer or compiler must decide how to split up the process and which base registers to assign which pieces. Binding instructions to base-register addresses at load time means binding the process to a portion of logical space.

The system could not easily perform this base-register assignment function dynamically because it would be very time-consuming and complicated to determine which instructions to modify.

Figure 4: Memory allocation using base registers: (a) typical memory snapshot at a point in time; (b) making room for program C by compaction; (c) making room for program C by partial removal of program A.

#### Dynamic Relocation Using Paging

Dynamic relocation using base registers, which requires program to be located in contiguous areas of main memory, leads to difficulties in fully utilizing main memory because free areas develop which are not large enough to be used. If, however, programs and main memory could be broken into small units and the program pieces could be located in corresponding sized blocks anywhere in main memory, then the possibility exists of utilizing main memory more effectively. Paging is the name given to a set of techniques which enable such a uniform memory ragmentation to be implemented. Paging techniques can also allow economic implementation of a logical-memory space larger than the physical-memory space.

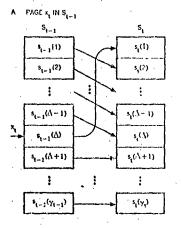

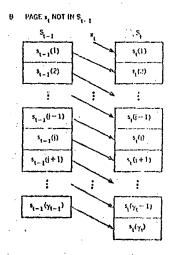

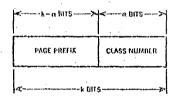

In a paged system, physical memory is considered to be broken up into blocks of a fixed size, usually 512, 1,024, or 2,048 words. The term page refers to units of logical space, while equal-sized units of physical space are called blocks. The programs are also considered to be split into pages of a size equal to the block size of physical memory. the address in such a system is considered to be represented by two numbers: (1) a page address or number and (2) a linewithin-page address. For a machine with an n-bit address field, the high-order p bits are considered the page address and the remaining n - p bits are the line address. The operating system may occupy less memory than a multiple of a larger In newer systems the page size can be changed page size. dynamically by the system. The memory can be more fully utilized by the system if smaller page sizes are available (64, 128, or 256 words). More effective utilization of memory results from using smaller page sizes for the following reason. Since a given process is not usually going to require an amount of memory space which is an even multiple of a page size, the last page of a process will not utilize all the block assigned to it. It seems

reasonable to assume that on the average the last page of a process will use half of its assigned block. The larger the page size, the more potential waste space there is going to be. A paging mechanism requires a table, called a page table, or map with one entry for each page in order to perform address translation from logical to physical space. The smaller the page size, the larger the table required for a given logical-address space. Thus, there is a tradeoff between waster space related to page size and resources used to store and manipulate large page tables. The total amount of waste space due to unused block locations depends on the number of processes expected to reside in main memory.

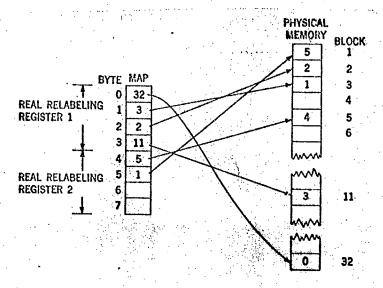

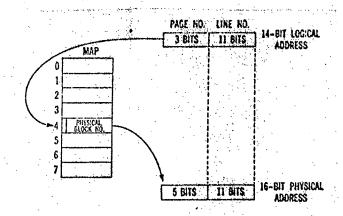

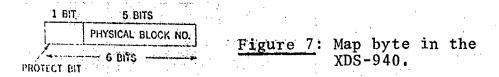

### E.g. Paging on the XDS-940

The address space of a process in the XDS-940 can be as large as 64K, and thus the logical-address space is smaller than the physical-address space. It should be noted that there are general cases of a paged system yielding a virtual memory larger than the physical-address space. A process in the XDS-940 is broken up into 2K word pages, and memory is similarly broken into 2K word blocks. There are 14 bits in the address field of a 940-instruction The address field is considered to contain two parts, a 3-bit page number and an 11-bit line-within-page number. The relocation mechanism (Figure 5) uses eight 6-bit bytes called a memory map. The memory map in the XDS-940 is organized as two 24-bit registers. Each register contains four map bytes. These registers are called the real relabeling registers, because they relabel (map) the page number into a physical-memory block number. These map bytes are considered by the hardware numbered 0 to 7 and correspond to logical pages. A given map byte is addressed by the page number contained in the memory address. Within a given map byte is a number for the actual physical block containing the code for the logical

page. For example, in Figure 5 logical page 0 is in physical block 32, logical page 1 is in physical block 3, and so forth. The numbers in the physical blocks of the figure indicate which logical pages they contain.

The logical address is converted to a physical address as shown in Figure 6.

The 3-bit page number indicates which map register contains the physical-block number where the page actually resides. The map register is 6 bits long and is shown in Figure 7; note 5 bits contain the physical-block number, and 1 bit is for memory protection. The physical address is simply formed by concatenating the physical-block number with the line number to form a 16-bit address. With 16 bits, 64K of memory can be addressed.

This hardware mechanism is quite simple, but to work as part of the of the total system it requires additional software tables, which keep track of the memory space of each process. The basic idea is that when a process is to be brought into main storage, the software monitor examines the state of main storage and swaps out only as many pages as are required in conjunction with free pages to meet the needs of the incoming process. The monitor then assigns the available physical blocks to the logical pages of the incoming process and swaps its pages into these blocks. The memory map is updated. Then after restoring the processor registers and program counter to the values they had when the process was last executing, the process is restarted.

Figure 5: Paging in the XDS-940

Figure 6: Mapping from logical to physical address in the XDS-940.

## Memory Map

The most important general concept introduced above is that of a memory map. A map translates the logical-address space into the physical-address space. In the dynamic-relocation techniques, the map is a set of tables in memory or a set of hardware registers. In the static-relocation technique the

map is a program. In the dynamic-relocation method using base registers, the base registers are the map. dynamic-relocation method using paging, the page map can be looked at as a way of efficiently implementing multiple base registers. The paging process is completely invisible to the users and to the compilers, which function as if they were working with one contiguous logical chunk. The ability to fragment memory uniformly, made possible by splitting main memory into blocks, means that all blocks of main memory can be used, although assure that no two shared procedures which might be used concurrently occupied the same position in logical space. If the page table were organized and addressed as an actual or simulated associative memory, then it could be reduced in size because no gaps need result. The practical problem of implementing in hardware and software such a large associative map for efficient execution may still create difficulties, although further study may be fruitful.

In summary, then the difficulty of using paging for sharing single copies of procedures and data in full generality and for allowing for data-structure growth results:

- Because of the large number of address bits required to ensure unique page numbers in a large logical space.

- Because of the large, possibly sparsely filled, map required using an indexed page table (with an efficient associative map this argument is reduced, although duplicate entries for each page of shared procedures and data must exist in the map of each process using the shared procedures or data).

- Because of the careful bookkeeping required by the installation and the system to be certain that procedures used concurrently do not occupy the same position in logical space (i.e., have the same page numbers), and to properly position data which contain address references.

### Segmentation Concept

The problems with physical-space allocation using static relocation resulted because address references were bound to positions in physical space when procedures and data were loaded into the system. Once loading was accomplished, all addresses were absolute physical locations. This restriction was removed in the base-register and paged systems by introducing mechanisms which allowed physical-address references to be made relative to either a base register or block number, the contents of which did not have to be set until execution time. However, the particular base register or map entry to be used was bound into the instructions at load time. In other words, once loading was accomplished, all addresses were to absolute logical locations.

The problem which segmentation sets out to solve is that of allowing relative addressing within the logical-memory space. This means that logical space must be broken up into chunks of contiguous locations and all addresses within a given chunk are to be relative to the start of the chunk.

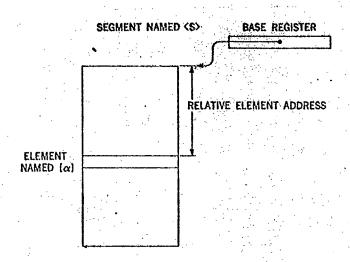

We then need a hardware or software base register which points to the base location for each chunk. Interchunk references must refer to the proper base register and give a relative address within the referenced chunk. The trick is to develop an efficient mechanism which allows these base registers to be assigned at execution time. The chunks of contiguous logical locations are commonly called segments. The basic idea of segmentation is thus quite simple, but the mechanisms for allowing assignment of base registers at execution time are more involved.

A <u>segment</u> is an ordered set of data elements (usually computer words) having a name. A particular data element within a segment is referenced by the symbolic segment name and the symbolic data-element name with the segment,  $(S)/[\alpha]$ . The notation (S) indicates a symbolic segment named  $\alpha$ . The symbolic segment name (S) is eventually (at run time) translated into a base-register number, and the symbolic data-element name in the segment  $[\alpha]$  is going to be translated into a relative location within the segment. In other words, a segment is a one-dimensional array, and the segment name is related to the address in logical space of this array (its base address); the symbolic element name within the segment is related to the address of the referenced element relative to start of the segment, as shown in Figure 8.

Segmentation often referred to as two-dimensional logical-address space because particular elements within the logical space are explicitly referenced by a pair of names. A paging system is not considered two-dimensional, even though the address has a page-number and a line-number pair, because these conventions are invisible to the user. To be general

one could consider base-register and paged systems as segmented systems allowing one segment, and thus the segment name is implicit. In a general segmented system, the user programs his addresses using a pair notation,  $(S)/[\alpha]$ . A segment is a self-contained logical entity of related information defined and named by the programmer, such as a procedure, data array, symbol table, or pushdown stack. There is no logical restriction on the length of a segment, although in any given implementation there will be an upper bound on segment length. Segments can grow and contract as needed.

Figure 8: A Segment.

## Communications Within the Time Shared Computer

The purpose of a timeshared computer system is rapid time multiplexing of computer-system resources on behalf of user requirements. The system attempts to perform this multiplexing so as to satisfy user completion and response-time needs and to utilize system resources efficiently. These time shared systems are usefully viewed as large communication-switching centers which control the transmission and trans-

formation of information as it moves between the large number and variety of devices (terminals, discs, etc) that are attached.

### Communication with Main Memory

The central point through which the information passes in present organizations is main memory (with a possible side journey to the CPU for transformation) as it moves from one device to another. Main memory is a prime system resource and consequently, a potential source of communications problems. In timesharing systems, multiple CPUs, high-transferrate secondary storage devices, and numerous I/O devices share access to main memory. The processors which control the secondary storage and I/O devices and communication with memory are usually referred to as channels, I/O controllers, or I/O processors.

## Communication with Auxiliary Storage and I/O Devices

A basic communication problem with auxiliary storage and I/O devices is gaining access to a direct-transfer path to main memory. A timesharing system contains a variety of devices attached to it. Associated with these devices is a range of data-transfer rates. Direct-transfer paths to main memory require logic to resolve conflicts for access to a memory module and require sending an receiving circuits at each end of the path; therefore, it is usually uneconomical to provide a separate path for each device. It is possible, however, using the fact that the attached devices have a range of transfer-rate requirements, to design I/O processors which enable many devices to share one direct-transfer path to main memory concurrently.

#### Communication with Remote Devices

Three major communication problems are associated with remote devices such as terminals, printers, etc. these are

- the transmission of information between the central facility and the remote devices

- the interface between transmission lines and the central facility

- the interface between transmission lines and the remote devices

Along with the transmission of information techniques must be considered for utilizing standard telephone lines for digital information, sharing lines among several devices, and synchronizing communication between remote points. Associated with the interface between transmission lines and the central facility are the problems of identifying, controlling, and addressing communicating devices and converting the transmitted information to a form usable by the central machine and vice versa. Associated with the interface between transmission lines and the remote devices are problems of encoding information and providing identification.

# Communication With the Main Memory

Multiple Memory Box and Bus Organization: The technological problem to be solved in the design of a memory communication system is to provide adequate transfer capability between main memory and all processors requiring access. In practical systems, the rate at which data can be transferred between processors and main memory is limited by the transfer

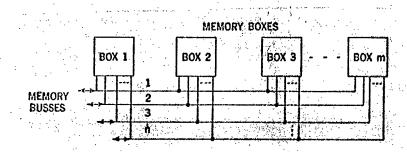

capabilities of the memory itself and the memory busses. The rate at which the memory can transfer information is often referred to as the memory bandwidth, usually measured in words per second. Bandwidth limitations also exist for the busses. Because the memory system is shared by several processors, care must be taken in the design to keep performance from being seriously degraded due to interference caused by simultaneous attempts on the part of the several processors to utilize a facility such as a memory bus or portion of memory itself. Figure 9 shows a common method for organizing the memory structure in a resource-sharing system.

The maximum memory-system bandwidth for the system shown in Figure 9 is p X R, where p is the smaller of the number of memory modules m and the number of access paths n, and R is the maximum transfer rate of each box. In other words, the maximum transfer rate is achieved when each path requests access to a separate module.

The minimum transfer rate is just R and occurs when all paths request access to the same module. There is interference in this case.

Figure 9: Memory organization in a resource-sharing system.

The scheme shown in Figure 9 cuts interference by allowing simultaneous access to more than one box. That is, if bus 1 requests access to box 2 at the same time buts 2 requests access to box 3, both accesses are granted because each box has its own addressing and read/write circuitry. Even given the scheme shown in Figure 9, serious interference can result when memory addresses are contiguous in the boxes, e.g., box 1 having addresses 1 to 16K 1 to 32K. Consider the case of a high-speed drum processor which transfers at the memory rate. If this device has a higher priority for memory access than the arithmetic unit, then during a block transfer the arithmetic unit could be denied memory access for a prolonged period if it tried to access the memory box bieng used by the drum processor. To get around this problem designers have developed the technique called interleaving. (Analagous to multiplexing)

In an interleaved memory, consecutive addresses are in different memory boxes. For example, in a two-memory-box system all the even addresses might be in one box and all the odd addresses in the other. With an interleaved memory, the probability of one processor's tying up the memory for a significant time is greatly decreased. The design problem is to determine the size of each box and whether or not interleaving is to occur over all boxes or over groupings of boxes.

E.g. The IBM 360/85 Memory Organization. A schematic of the model 85 memory system is given in Figure 10. Main storage in this system has a cycle time of about 1 microsecond. For storage configurations of 500K and 1,000K words (32-bit), storage is interleaved four ways. For smaller storage configurations, storage is interleaved two ways. Note that the buffer storage is available only to the CPU and not to the

I/O or other processors. The buffer storage has a cycle time of 80 nanoseconds. The buffer storage is either 4K, 6K, or 8K words. The design of this system was oriented toward increasing the effective speed of memory as seen from the CPU. The importance of high data-transfer rate between all processors and memory has not been highly developed in this machine. The memory bus is four words wide in order to achieve the bandwidth required for the main applications envisioned. For I/O oriented systems, this organization offers little advantage, but the basic ideas can be extended.

Main memory and the buffer storage are organized into sectors of 256 words. During operation, a correspondence is set up between buffer-storage sectors and main-storage sectors, in which each buffer-storage sector is assigned to a single different main-storage sectors. Because of the limited number of buffer storage sectors, most main-storage sectors do not have any buffer-storage sectors assigned to them. Each of the buffer-storage sectors has a 14-bit sector address register, which holds the address of the main-storage sector to which it is assigned.

Figure 10: 1BM 360/85 memory system.

The assignment of buffer-storage sectors is dynamically adjusted during operation so that they are assigned to the main-storage sectors that are currently being used by programs. If the program causes a fetch from a main-storage sector that does not have a buffer-storage sector assigned to it, one of the buffer-storage sectors is then reassigned to that main-storage sector. To make a good selection of a buffer-storage sector to reassign, enough information is maintained to order the buffer-storage sectors into an activity list.

When a buffer-storage sector is assigned to a different main-storage sector, the entire 256 words located in that main-storage sector are not loaded into the buffer at once but each sector is divided into 16 blocks of 16 words each, which are located on demand.

Storage operations always cause main storage to be updated. If the main-storage sector being changed has a buffer-storage sector assigned to it, the buffer is also updated; otherwise no activity related to the buffer takes place. Since all the data in the buffer are also in main storage, it is not necessary on a buffer-storage-sector reassignment to move any data from the buffer to main storage.

Two 80-nanosecond cycles are required to fetch data that are in the buffer. The first cycle is used to examine the sector address and the validity bits to determine if the data are in the buffer. The second cycle is then used to read the data out of the buffer. If the data are not in the buffer, additional cycles are required while the block is loaded into the buffer from main storage.

Simulation was used extensively during the design of this memory system. There are many important parameters, such as choice of a replacement algorithm, buffer size, sector and block sizes, which must be determined.

With the simulation running a representative scientificoriented job mix, it was found that mean performance of this

system as compared to an ideal system consisting of only

80-nanosecond memory was 81 percent. That is, on average,

the CPU obtained information from the buffer storage on

81 percent of its references.

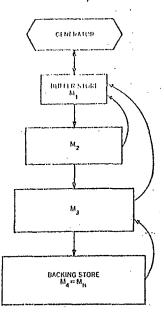

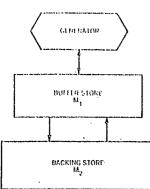

#### Memory Management Software - Storage Hierarchies

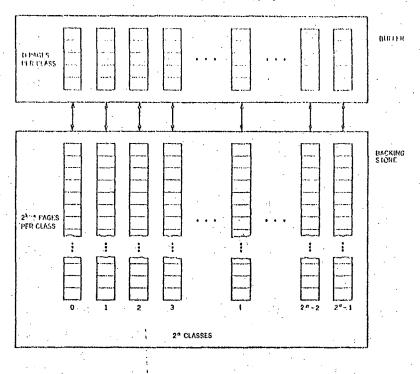

The purpose of storage system is to hold information and to associate the information with a logical address space known to the remainder of the computer system. For example, the CPU may present a logical address to the storage system with instructions to either retrieve or modify the information associated with that address. If the storage system consists of a single device, then the logical address space corresponds directly to the physical address space of the device. Alternatively, a storage system with the same address space can be realized by a hierarchy of storage ranging from fast but expensive to slower but relatively inexpensive devices. In such storage hierarchies, the logical address space is often partitioned into equal size pages (or unequal size segments) that represent the blocks of information being moved between devices in the hierarchy.

A hierarchy management facility is included to control the movement of pages and to effect the (generally dynamic) association between the logical address space and the physical address space of the hierarchy. When the CPU references a logical address, the hierarchy management facility first determines the physical location of the corresponding logical page and may then move the page to a fast storage device where the reference is effected. The goal of the hierarchy management facility is to maximize the number of times logical information is in the faster devices when being referenced. As this goal is approached, most references are directed to the fast, small stores whereas most of the logical address space is distributed over the slower, large stores.

Memory (hierarchy) management becomes a severe problem in multiprogramming and critical memory systems. a multiprogramming system, many programs are concurrently executed by the processor. Thus the main memory is shared by many programs. Since the total size of all the programs far exceeds the size of the main memory, in order to keep information that will be used in the near future in the main memory, the system constantly moves information between several levels of storage media. Here, for example, we shall consider the case of paged memory system; that is, the address spaces are partitioned into equal size blocks of contiguous addresses. The page replacement problem is defined as the problem of deciding which page should be kept in memory and which should be removed when additional space is needed. Obviously, the page removed should be a page with the least probability of being needed in the near However, this should be done without incurring difficult implementation problems at the same time.

Many replacement algorithms have been proposed and studied, examples:

- 1. Least Recently Used (LRU)

- 2. Stack Replacement Algorithms

- 3. Random Replacement

- 4. Working Set Replacement Algorithm

for an excellent introduction to those algorithms, see the paper given by R.L. Mattson, et. al.

We shall illustrate briefly as an example the Working Set Replacement Algorithm. (see the paper by W.W. Chu)

Model (Working Set Replacement Algorithm)

The working set W(t,t) at a given time t is the set of distinct pages referenced in the time interval (t-(T-1),t) where T is called the working set parameter. The working set size w(t,T) is the number of pages in W(t,T). The k average working set size S(T) is defined as S(T) = Lim  $\frac{1}{k}$   $\sum_{k \to \infty} W(t,T)$ .

For systems employing working set replacement algorithm, several parameters are of interest:

- 1. page inter-reference internal distribution F(t) which describes the fraction of the page inter-referenced intervals less than T.

- 2. Average page fault freq. m(T) which describes the average number of page faults per page reference for working set parameter T.

- 3. Average working set size S(T).

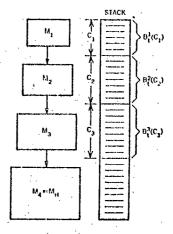

program's sequence of reference working set of replacement simulator algorithm  $(T) \quad \text{used}$   $F(T) \quad \text{for}$   $S(T) \quad \text{system}$

(An example including the results is given in Chu's paper).

Examples of how to use the parameters of the working set replacement algorithm.

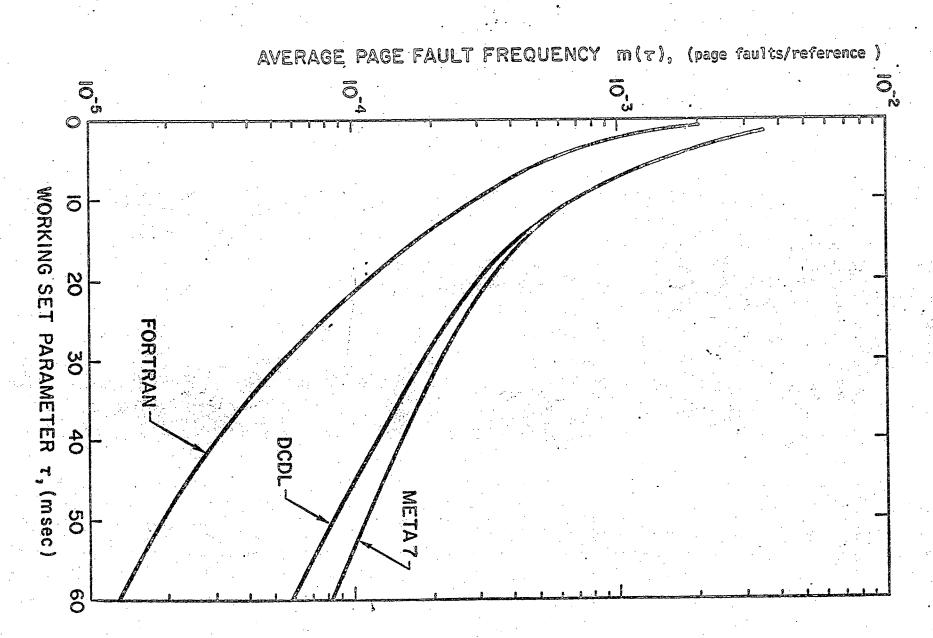

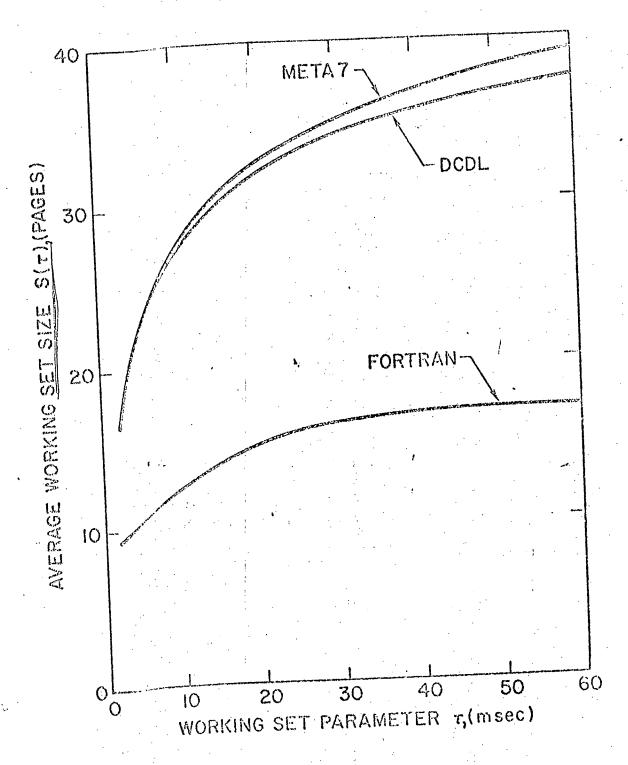

1. Suppose we would like the system to operate at an average page fault level of about  $10^{-4}$  page faults/reference; that is one page fault in every  $10^{-4}$  page reference, then from the graph representing m(T) versus T for different programs,

$m(T^{O}) = 10^{-4}$  page faults/reference

$T^{o} = 22 \text{ m.sec}$

FORTRAN

$T^{O} = 45 \text{ m.sec}$

DCDL

$T^{O} = 54 \text{ m.sec}$

META-7

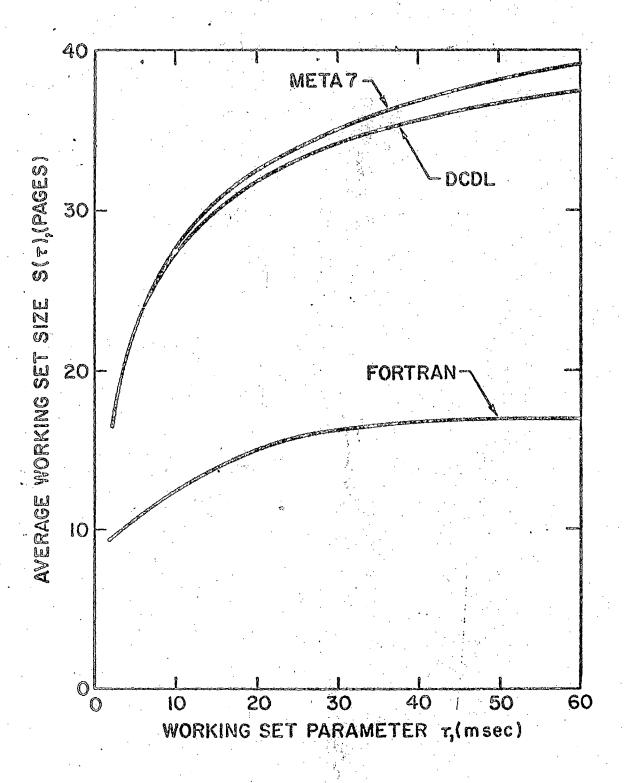

and from the graph representing the average working set size S(T) we find:

$S(T^{O}) = 15 \text{ page}$  FORTRAN

$S(T^{O}) = 36 \text{ page}$  DCDL

$S(T^{O}) = 39 \text{ page}$  META-7

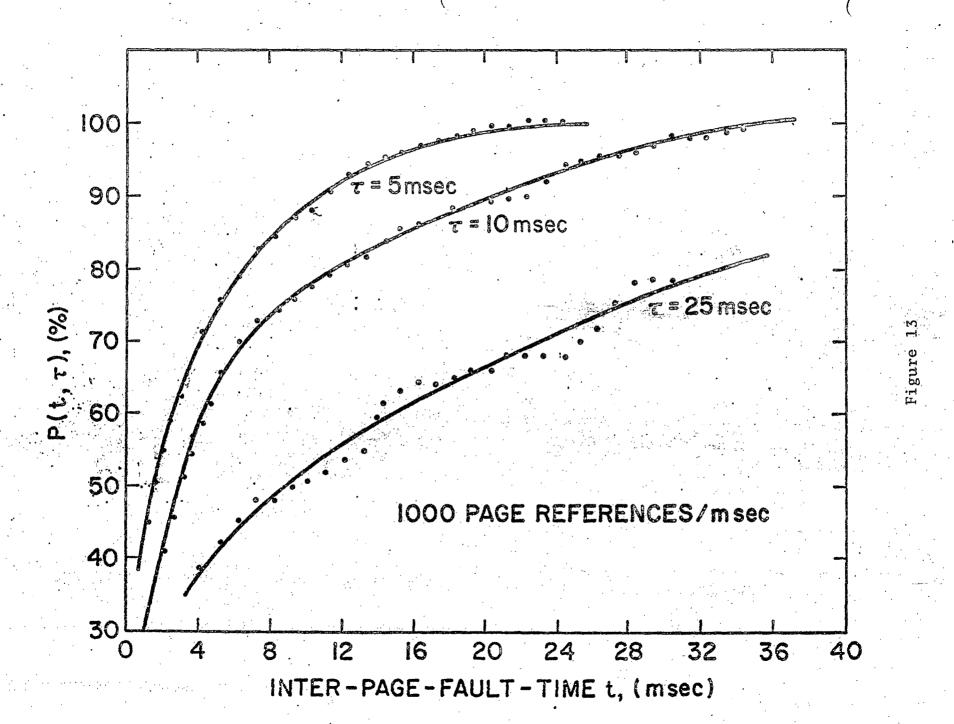

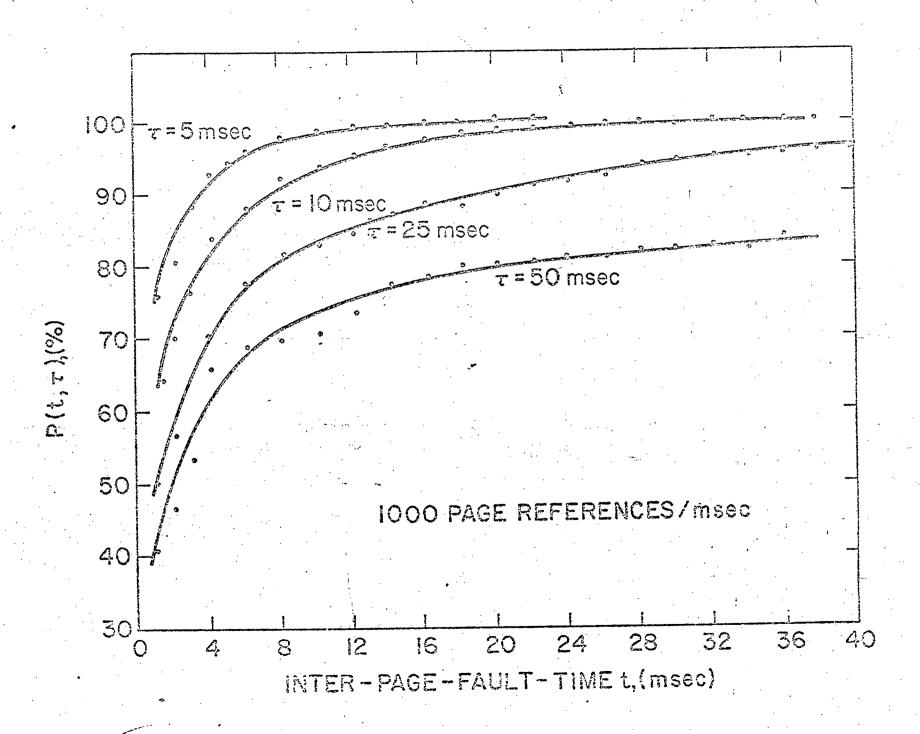

4. Inter-page-fault-time (time between page fault) distribution P(t,T) which describes the fraction of the interpage-fault times less than or equal to t for a given T.

If we assume that page reference rate is one page/unit time, we immediately obtain the following relationships:

m(T) = 1 - F(T)

1/m(T) = average running time between page faults

$$1/m(T) = \sum_{t=1}^{\infty} \{t. P(t 1,T) - P(t,T)\}$$

To employ measurement techniques for estimating these parameters, we collect data bout the pattern of references to all the pages which comprise the executed program and measure these parameters experimentally via interpretive execution (steps are shown in the following representation).

object programs | Interpreter | program's sequence of references (programs' behavior)

## Figure Captions

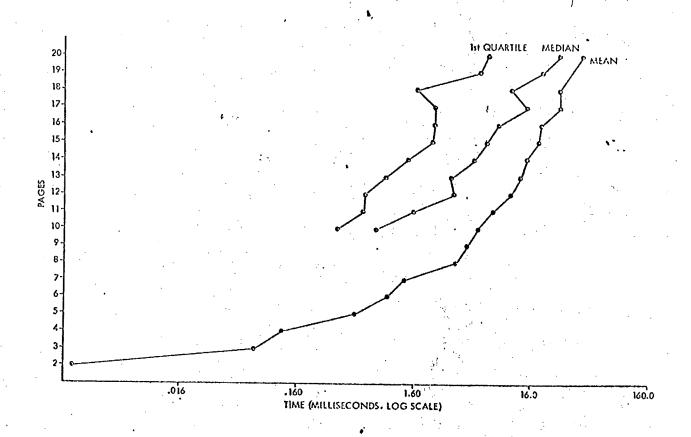

Figure 11: Average page fault frequency  $m(\tau)$  as a function of working set parameter  $\tau$ .

Figure 12: Average working set size  $S(\tau)$  as a function of working set parameter  $\tau$ .

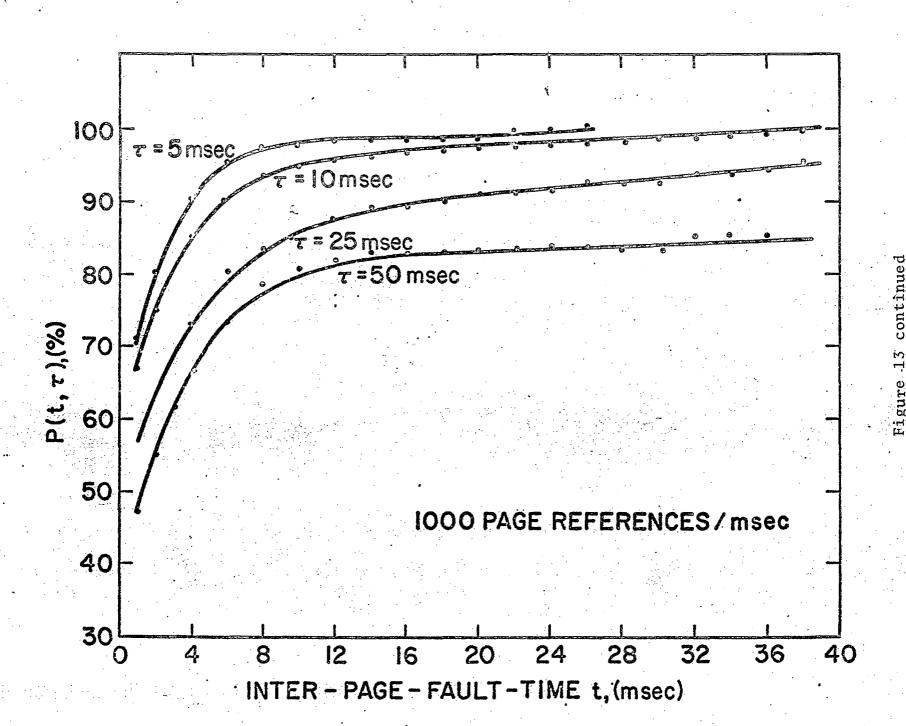

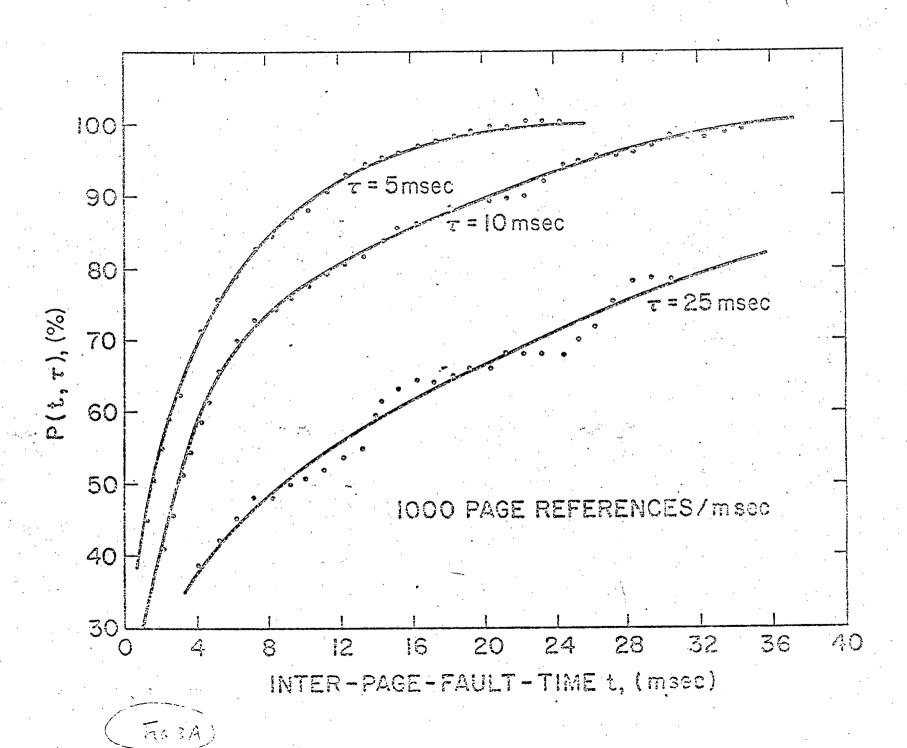

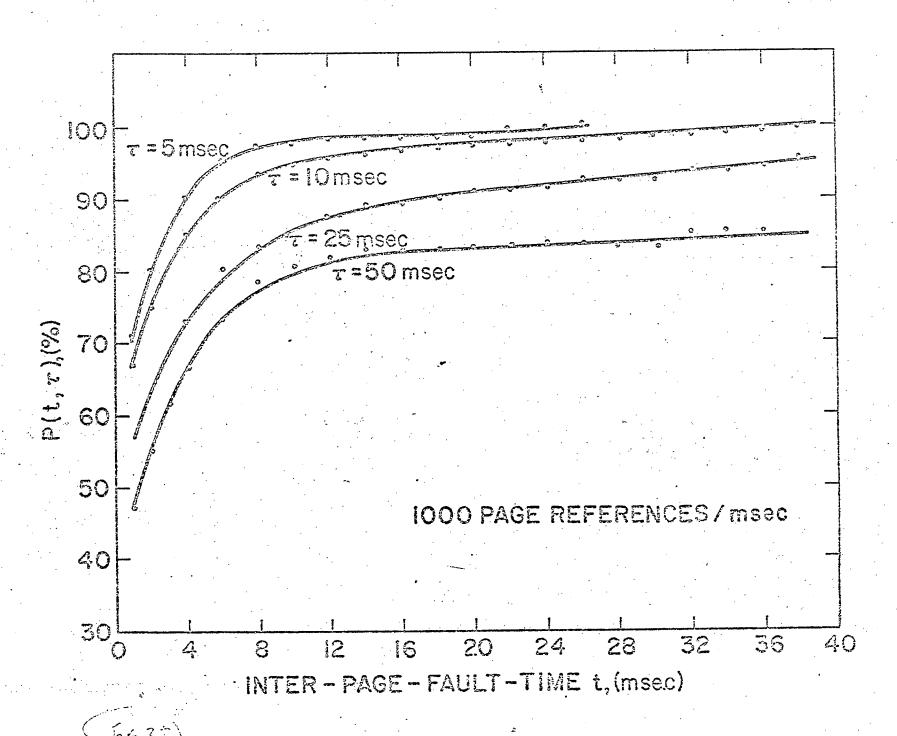

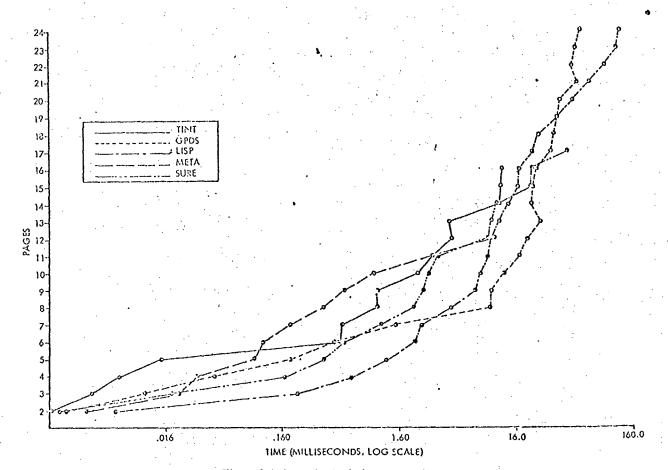

Figure 13: Inter-Page-Fault-Time Distribution

- a) FORTRAN Compiler

- b) DCDL

- c) META-7 Compiler

Figure 12

References - Memory Hierarchy

Management

Presented at the PBI International Symposium XXI on Computer-Communications Network and Teletraffic, April 1972.

Measurement Data on the Working Set Replacement

Algorithm and Their Applications\*

by

W.W. Chu, N. Oliver<sup>†</sup> and H. Opderback

Computer Science Department University of California Los Angeles, California 90024

(Revised March 31, 1972)

#### **ABSTRACT**

Page inter-reference interval distribution, average page fault frequency (the frequency of those instances at which an executing program requires a page of data or instructions not in the main memory) average working set size and inter-page fault-time (time between page fault) distribution for a simulated Working Set Replacement Algorithm for three typical programs with different sizes were measured on the UCLA Sigma Executive (SEX) time-sharing system via page reference strings. These measured results are reported in this paper. The average page fault frequency relationships between working set parameters and process scheduling are discussed. These relationships are useful in planning the working set size and process scheduling which optimize system efficiency.

This research was supported by the U.S. Office of Naval Research, Mathematical and Information Sciences Division, Contract No. NO0014-69-A-0200-4027, NR 048-129 and the Advanced Research Projects Agency of the Department of Defense, Contract No. DAHC 15-69-C-0285

<sup>&</sup>lt;sup>†</sup>Formerly of UCLA, now at General Motors Research Technical Center, Warren, Michigan.

#### I. Introduction

Memory management becomes a severe problem in multiprogramming and virtual memory systems. In a multiprogramming system, many programs are concurrently executed by the processor. Thus the main memory is shared by many programs. Since the total size of all of the programs far exceeds the size of the main memory, in order to keep information that will be used in the near future in the main memory, the system constantly moves information between several levels of storage media.

In this paper, we consider the case of paged memory systems: that is, the address spaces are partitioned into equal size blocks of contiguous addresses. The paged memory system has been used by many computer systems. However, the basic page replacement problem of deciding which page should be kept in main memory and which should be removed when additional space is needed is still little understood and has been of considerable interest. Obviously, the page removed should be a page with the least probability of being needed in the near future. The difficulty lies in trying to determine which page this will be without incurring difficult implementation problems at the same time.

Many replacement algorithms have been proposed and studied in the past: such as Random, First-in First-out, Stack Replacement Algorithms [1] (for example, Least Recently Used (LRU)), and the Working Set Replacement Algorithm. [2] The first three replacement algorithms require a fixed size memory space for each process. The Working Set Replacement Algorithm, however, requires a variable size storage space for each process and the size

varies with program demands. This variable storage space provides an adaptive capability in the replacement algorithm which is quite appealing. The working set principle of memory management states that a program may use a processor only if its working set (set of pages) is in the main memory, and no working set pages of an active program may be considered for removal from the main memory. Properties of the working set replacement algorithm, the relationships among page inter-reference interval, average page fault frequency and average working set size for the Working Set Replacement Algorithm are described in a recent paper by Denning and Schwartz. [3]

Because of the complex nature of program behavior, analytical estimation of the above mentioned parameters of program behavior becomes very difficult. Yet this information is important in the planning of an efficient replacement algorithm that optimize system performance. Therefore we employ measurement techniques for such estimations. We collect data about the pattern of references to all the pages which comprise the executed program, and measure these parameters experimentally via interpretive execution. This technique has been used previously to measure dynamic program behavior [4] and also to measure the performance of Belady's Optimal Replacement Algorithm [5] and LRU replacement algorithms. [6,7]

Here we report the measured program behavior of the Working Set

Replacement Algorithm. We shall first report measurement results such as

page inter-reference interval distribution, average page fault frequency,

average working set size and inter-page-fault-time distribution. We then

discuss the use of average page fault frequency to determine the working set

parameter, and propose a page fault scheduling algorithm for process scheduling

which improves system efficiency.

### II. Measurements and Results

The working set  $W(t,\tau)$  at a given time t is the set of distinct pages referenced in the time interval  $((t-\tau+1), t)$ , where  $\tau$  is called the working set parameter. The working set size  $W(t,\tau)$  is the number of pages in  $W(t,\tau)$ . The average working set size  $S(\tau)$  defines as  $S(\tau) = \lim_{k \to \infty} \left\{ \frac{1}{k} \sum_{t=1}^k W(t,\tau) \right\}$ . For systems employing working set replacement algorithms, several parameters of interest are: 1) page inter-reference interval distribution  $F(\tau)$ , which describes the fraction of the page inter-reference intervals less than  $\tau$ ; 2) average page fault frequency  $W(\tau)$  which describes the average number of page faults per page reference for working set parameter  $\tau$ ; 3) average working set size  $S(\tau)$ , and 4) inter-page-fault-time (time between page fault) distribution  $P(t,\tau)$  which describes the fraction of the interpage-fault-times less than or equal to t for a given  $\tau$ .

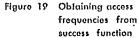

$F(\tau)$  is a fundamental distribution; it closely relates to the other three parameters. When we assume that the page reference rate is one page per unit time, we know that the page references that result in page faults are those references whose inter-reference intervals exceed  $\tau$ . Thus,  $m(\tau)$  = 1- $F(\tau)$ . It can be shown [3] that  $S(\tau) = \sum_{k=0}^{\tau-1} m(k)$ . Thus,  $S(\tau)$  is closely related to  $m(\tau)$ .  $1/m(\tau)$  is the average running time between page faults. Since  $P(t,\tau)$  is the fraction of inter-page-fault-time less than or equal to t,  $1/m(\tau)$  is the time average of the density function  $P(t+1,\tau) = P(t,\tau)$ ; that is,  $1/m(\tau) = \sum_{k=0}^{\infty} t \cdot [P(t+1,\tau) - P(t,\tau)]$ .

To employ measurement techniques for estimating these parameters, we collect data about the pattern of references to all the pages which comprise the executed program and measure these parameters experimentally via interpretive execution. For this purpose an interpreter for the UCLA Sigma-7 time-sharing system has been developed. This interpreter is capable of

executing Sigma-7 object programs by handling the latter as data and reproducing a program's sequence of references. This sequence, in turn, can then be used as input to programs which simulate the Working Set Replacement Algorithm.

Three different programs with different sizes were interpretively executed, and their behavior was investigated under the Working Set Replacement Algorithm. A FORTRAN Compiler was chosen as the representative for a small program. META-7 was chosen as the representative for a large program. It translates programs written in META-7 to the assembly language of the Sigma-7. A DCDL (Digital Control Design Language) compiler was chosen as a representative for a medium size program. This compiler is written in META-7. DCDL translates specifications of digital hardware and microprogram control sequences into interpretive code.

Table I shows some characteristic properties of these programs.

The column 'size' is divided into two parts. 'Static' refers to the number of pages necessary to store the program as an executable file on a disk where one page consists of 512 32-bit words. 'Dynamic' indicates the number of different pages actually referenced while processing the given input data. The difference between the number of pages in static and dynamic results from the fact that programs creat new pages during execution for working storage areas and that not all pages of programs are reference during executing a specific set of input data.

Table 1. Program sizes of the three measured programs

|         | Size       |        | e       | Numt | lumber of page references |     |

|---------|------------|--------|---------|------|---------------------------|-----|

|         |            | Static | Dynamic | ,    |                           |     |

| FORTRAN | Smad       | 24     | 34      | • •  | 1,000,000                 | • . |

| DCDL.   | medicin    | 44     | 58      |      | 1,000,000                 | •   |

| META-7  | layer size | 84     | 153     |      | 1,000,000                 | • . |

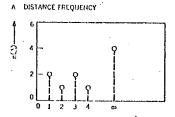

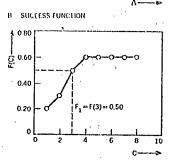

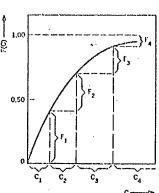

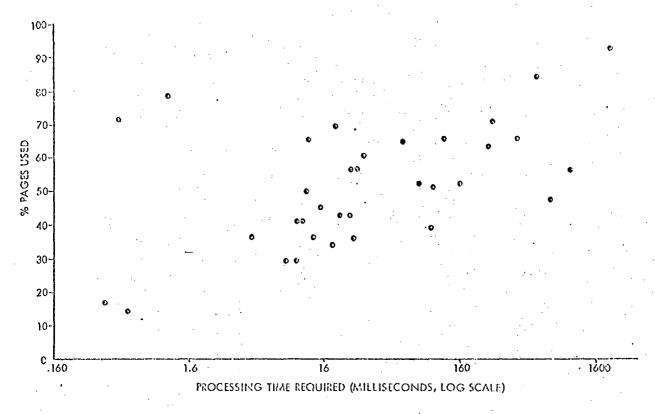

Figure 1 shows the average page fault frequency  $m(\tau)$  for the three programs. We note that all three programs exhibit similar page fault characteristics. The average page fault frequency decreases rapidly with  $\tau$ . Large programs tend to have a slower rate of decrease. The reason for such characteristics is mainly the locality of the program; that is, during any interval of execution, a program favors a subset of its pages, and this set of favored pages changes its membership slowly. Further, the locality for large programs is usually larger than that of small programs. The page inter-reference interval distribution  $F(\tau) = 1-m(\tau)$  can be obtained easily from  $m(\tau)$ . The average working set sizes as a function of  $\tau$  are shown in Figure 2. Measurement data support the premise that average working set size increases as program size increases and reaches a constant level as τ reaches a certain value. The  $P(t,\tau)$ 's of the three programs for selected  $\tau$ 's are shown in Figure 3. We note that  $P(t,\tau)$  is very sensitive to  $\tau$  and program size. For a given program, the average inter-page-fault-time increases as  $\tau$ increases. This occurs because for the small  $\tau$  case, many of the pages to be referenced in the near future are in the secondary memory; thus the average working set size is very small and yields a high page fault rate. For the large  $\tau$  case, most of the pages are in the main memory which yields a large average working set size and a small page fault rate. For

a given t, large size programs have a higher page fault rate than that of a small size program. In the next section we shall discuss the applications of these parameters to determine the working set parameters and process scheduling which improve system efficiency.

# III. Applications of Measurement Data

A) Working Set Parameter  $\tau$  is an important parameter which affects page fault rate, memory utilization, and thus system efficiency. The measurement data support the fact that  $\tau$  should be chosen according to the executing program (e.g., size) and system organization (e.g., available memory size and the speed ratio between main and secondary memory). If  $\tau$  is not properly chosen, for example if  $\tau$  is too short, then pages are removed from the main memory while still potentially useful. This results in high page traffic between the different levels of memory. If  $\tau$  is too long, then pages that are not needed may remain in the main memory, which is an inefficient use of memory space. Instead of choosing  $\tau$  arbitrarily, we propose to determine  $\tau$  from the measured  $m(\tau)$  and designate it as  $\tau^0$ . As a result,  $\tau^0$  is now closely related to program behavior as well as to system organization.

The efficiency of a program is defined as the ratio of total virtual running time to total real running time (total virtual time and total page waiting time); that is,

Eff = total virtual running time total real running time

(1)

1 1+m(τ)R

where R = A/T

A = Access time of the main memory

T = Access time of the secondary memory

Since R is fixed for a given system, from (1) we know a fixed average page fault frequency  $m(\tau)$  insures a certain level of efficiency.

Suppose we would like the system to operate at an average page fault level of about  $10^{-4}$  page faults/reference; that is, one page fault in every  $10^4$  page references. Then from Figure 1,  $\tau^0$  for Fortcomp, DCDL and META-7 are 22, 45, and 54 m sec (1 usec per page reference) respectively. From Figure 2, the corresponding average working set size is 15, 36, and 39 pages.

Usually in a multiprogramming environment several types of programs may be concurrently operated by the operating system. The working set parameter of such a system may either be variable of fixed. In the variable  $\tau$  case, the  $\tau^0$  should change from one program to another; while in the fixed  $\tau$  case, the  $\tau^0$  remains fixed for all types of programs. Because of the simplicity of a fixed  $\tau$  scheme, it requires less overhead to implement than the variable  $\tau$  scheme. However, the efficiency may not be as high as that of the variable  $\tau$  case.

One way to determine the value of a fixed  $\tau$  is to use the weighted average working set parameters of each program; that is,

$$\tau^{0} = \frac{1}{n} \sum_{i=1}^{n} u_{i} \tau_{i}^{0}$$

(2)

where  $\tau_i^0$  = working set parameter for the  $i^{th}$  program that selected from its  $m(\tau)$

u; = relative usage frequency of the i<sup>th</sup> program

n = total number of distinct programs used in the system

The decision as to which scheme should be used for a given system should be based on program behavior, relative usage frequency of all the distinct programs used by the system, and the overhead in implementing these schemes.

#### B. Process Scheduling

In a multiprogramming system, to increase system efficiency and to reduce response time for short jobs, the job queues for CPU processing usually have several priority levels. Let us consider a system having two levels of queues: Short Quantum Queue (SQQ) and Long Quantum Queue (LQQ). SQQ has a higher priority than LQQ. All jobs enter the SQQ. Processes in the SQQ are given one time slice at a time. The process is put at the back of the SQQ after the process either incurred a page fault or used up the time slice; that is, the process is serviced in a round-robin fashion. A process stays in the SQQ until its short quantum time runs out. It is then put on the front of the LQQ. The LQQ will not be serviced until the SQQ is empty. A process in the LQQ receives service until its long quantum time runs out. It is then put at the end of the LQQ.

When a system is properly designed, such scheduling algorithms yield: 1) fast response time to short jobs, and 2) most of the short jobs are run in the SQQ and long jobs (compute-bound processes) will run in the

LQQ. Since LQQ provides more memory space for each process than that of SQQ, such scheduling yields less page swapping.

short jobs will be in the LQQ; if the quantum time is too long, then many computational jobs will be in the SQQ. The system is designed such that most of the short jobs finish their processing in the SQQ and only the computebound processes enter into the LQQ. The short quantum time should be larger than the average real process time of short jobs. However, the process time varies from one process to another. In addition, the processing time is further complicated by page faults occurring during its execution.

The real processing time of a process is the sum of the virtual process time and the total time wasted due to page faults of that process. For example, two processes requiring the same amount of virtual CPU processing time could have very different page fault frequences, and thus yield very different real processing time. Therefore the real processing time is extremely difficult to estimate.

We know that page fault frequency has great influence on system efficiency and the response time of the short jobs. We propose to use a page fault as a measure in process scheduling; that is, when a process exceeds a certain number of page faults or exceeds the quantum time of the SQQ (whichever occurs first), then the process switches from the SQQ to the LQQ. We shall call such a scheme a page fault scheduling algorithm. In a multiprogramming environment, the CPU idle times due to page swapping between main and secondary memories are directly affected by the page fault frequency. The page fault scheduling algorithm should be effective in reducing CPU idle time And improve system efficiency. (See Appendix).

<sup>\*</sup>For a system operating in a multiprogramming environment, we should also include the time spent in waiting for the availability of CPU.

Processes with high page fault rates occupied in the main memory greatly reduce the efficient utilization of main memory. The page fault scheduling algorithm adaptively allocates the low page fault rate processes in the main memory and higher page fault rate processes in the secondary memory. Thus such scheduling improves the utilization of main memory. As a result, this will improve the average response time of the system. An analogy to the above scheduling algorithm is the well known "serving the shortest job first" algorithm in queueing theory that results in improvements in average waiting time; except in our case we have further improved the memory utilization efficiency.

The number of page faults occurring during processing before switching a process from a SQQ to a LQQ depends on the response time required, the number of processes operating concurrently, the replacement algorithm used, and page fault frequency characteristics. Further study in this area is needed.

In order to reduce response time, the quantum time of the SQQ and LQQ are further divided into many time slices. The optimal size of time slices is another important parameter that affects system efficiency. The time slice should be selected such that most of the processes either page fault or become inactive before running out of the time slice. Since  $P(t,\tau)$  describes the inter-page-fault-time distribution of a process for a given  $\tau$ , the time slice for the Quantum Queues can be determined from  $P(t,\tau)$ . For example, if we wish 95% of the time that the process will page fault before running out of the time slice — that is, only 5% of the time the process will run to the end of the time slice — then from Figure 3 we know

the time slices of the LQQ $^*$  for  $\tau=10$  m sec are: 28 m sec for the FORTRAN Compiler, 13 m sec for DCDL, and 12 m sec for META-7. Time slices for  $\tau=25$  m sec are: 58 m sec for the FORTRAN Compiler, 38 m sec for DCDL, and 35 m sec for META-7. Thus, the measured inter-page-fault-time distribution provides a good way to determine the optimal time slices for the Quantum Queues which avoids excessive unnatural interrupts that degrade response times.

The page fault scheduling algorithm, as well as the selection of the time slice form inter-page-fault-time distribution, are quite general and can be applied to other types of replacement algorithms.

#### V. Conclusions

Page inter-reference interval distribution, average working set size, average page fault frequency, and inter-page-fault-time distribution for three typical programs with working set replacement algorithms are measured and reported. Measurement results support program locality and the following working set properties: the average page fault frequency decreases rapidly as t increases and increases as program size increases. Based on these measured data, working set parameter and process scheduling may be selected from and based on the average page fault frequency. The time slices for the Quantum Queues may be determined from inter-page-fault-time distributions. A page fault scheduling algorithm is proposed for process scheduling in a multiprogramming environment. Such an algorithm is effective in reducing CPU idle time and improve system efficiency.

<sup>\*</sup>The three measured programs are not short jobs; they should be run in LQQ. Therefore, these measured  $P(t,\tau)$ 's provide the estimate of time slices for the Long Quantum Queue.

Although the Working Set Algorithm provides an upper bound on replacement algorithm performance, the high cost of implementation prevents it from being widely used. Therefore future research should be in developing low cost hardware devices for economically implementing the Working Set Algorithm or, perhaps even more fruitful, in developing new replacement algorithms that have performance comparable to that of the Working Set Algorithm but are much easier to implement. For example, we have recently studied a Page Fault Frequency Replacement Algorithm. Such an algorithm adjusts the LRU (Least Recently Used ) stack according to page fault frequency. Preliminary results already indicate it has excellent performance.

## Acknowledgement

The authors wish to thank P.E. Denning of Princeton University for his critical comments on this paper.

#### **APPENDIX**

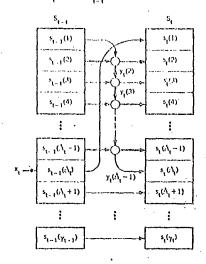

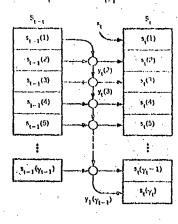

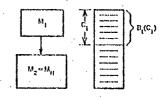

A Cyclic Queueing Model to Study CPU and I/O Operations

To illustrate the relationships among CPU idle time, average page fault frequency and swapping time (time to bring in a new page from the auxiliary memory) T, a cyclic queueing model [8] is used to study CPU and 1/0 operations. The system in Figure 4 consists of two classes of service facilities. Service facility class I represents a single CPU; its service rate is directly determined by the average page fault rate\*  $\lambda$ . Service facility class II represents k parallel I/O servers with each having an average service rate  $\mu = \frac{1}{1}$ . The k parallel servers represent, for example, a paging drum with k different sectors. Using such I/O facilities, a high degree of overlap of I/O requests can be achieved in a multiprogramming system with relatively low page fault frequency.

Let  $P_{ij}$  be the probability that a job leaving server i will proceed to server j. We assume that the job leaves CPU (server 0) and goes randomly to the k I/O servers for service; thus  $P_{0j} = \frac{1}{k}$ , for  $j = 1, 2, \ldots, k$ . Since jobs which have finished their I/O operations always return for CPU operations,  $P_{i0} = 1$  for  $i = 1, 2, \ldots, k$ ; and all the other  $P_{ij}$ 's are equal to zero.

Let N be the total number of jobs in the system, and let  $n_i$  denote the number of jobs in service plus the number in queue at the  $i^{th}$  server. The state of the system can then be determined by the k+1 tuple  $(n_0,n_1,\ldots,n_k)$  in which  $\sum_{i=0}^k n_i = N$ . The number of distinguishable states of the system—equal to the number of partitions of N customers among k+1 servers—is  $\binom{N+k}{k}$ .

<sup>\*</sup>For a system using Working Set Replacement Algorithm with parameter  $\tau$ , then  $\lambda = m(\tau)$ .

and the company of the first transfer of the company of the company of the

the first of the control of the cont

Let  $P(n_0,n_1,\ldots,n_k)$  be the stationary probability that the system is in state  $(n_0,n_1,\ldots,n_k)$ , and let all the service times be assumed to be exponentially distributed. Then the steady state equations can be written in the form:

$$\begin{cases} \varepsilon(n_{0}) \ \lambda + \sum_{j=1}^{k} \varepsilon(n_{j}) \ \mu \end{cases} P(n_{0}, n_{1}, \dots, n_{k})$$

$$= \sum_{j=1}^{k} \varepsilon(n_{j}) \ \lambda P_{0j} P(n_{0}+1, n_{1}, \dots, n_{j}-1, \dots, n_{k})$$

$$+ \sum_{i=1}^{k} \varepsilon(n_{0}) \ \mu P_{i0} P(n_{0}-1, n_{1}, \dots, n_{i}+1, \dots, n_{k})$$

(A1)

where the indicating function

$$\varepsilon(n_j) = \begin{cases} 0 & \text{if } n_j = 0 \\ 1 & \text{if } n_i \neq 0 \end{cases}$$

accounts for the impossibility of any customer leaving the j<sup>th</sup> server if that server is empty.

The left hand side of (A1) represents the rate of transition out of state  $(n_0,n_1,\ldots,n_k)$ ; and the right hand side is the rate of transition into this state. Solving (A1) by a method of separation of variables [8], we have

$$P(n_0, n_1, \dots, n_k) = \frac{1}{G(N)} \prod_{i=1}^k \left(\frac{P_{0i}\lambda}{\mu}\right)^n i$$

$$= \frac{1}{G(N)} \left(\frac{\alpha}{k}\right)^{N-n_0}$$

(A2)

where  $\alpha = \lambda/\mu$  and the normalizing function G(N) is determined from the fact that the sum of all the  $P(n_0, n_1, ..., n_k)$  is equal to 1. Thus

$$G(N) = \sum_{\substack{k \\ \sum n_{i} = 0}} \frac{k}{i=1} \left(\frac{\alpha}{k}\right)^{n_{i}}$$

$$= \sum_{n_0=0}^{N} {\binom{N-n_0+k-1}{k-1}} \left(\frac{\alpha}{k}\right)^{N-n_0}$$

(A3)

where  $\binom{N-n_0+k-1}{k-1}$  is the number of distinguishable partitions of N-n<sub>0</sub> jobs among k I/O servers.

The probability that the CPU is idle is

$$P_0 = \sum_{\substack{k \\ \sum j=1}^{k} n_j = N} P(0, n_1, n_2, \dots, n_k)$$

$$= \frac{1}{G(N)} \left( \frac{N+k-1}{k-1} \right) \left( \frac{\alpha}{k} \right)^{N}$$

(A4)

For the case k = 1, then (A4) reduces to  $P_0 = \frac{\alpha^N}{N}$

For the case N = 3 and k = 6, the values of  $P_0$ 's for selected  $\alpha$ 's are shown in Table II.

| Table II | $P_0$ vs. $\alpha$ |

|----------|--------------------|

| α        | Po                 |

| 0.25     | 0.003              |

| 0.50     | 0.019              |

| 1.00     | 0.091              |

| 1.50     | 0.187              |

| 2.00     | 0.278              |

| 2.50     | 0.362              |

| 3.00     | 0.431              |

| 3,50     | 0.488              |

| 4.00     | 0.537              |

| 4.50     | 0.577              |

| 5.00     | 0.612              |

We note that  $\alpha$  is the ratio of average page swapping time (from secondary memory) to average inter-page-fault-time. A large  $\alpha$  implies large page swapping time or small inter-page-fault-time (high page fault frequency), or both. Thus the probability of CPU idle time increases as  $\alpha$  increases. Hence, the page fault scheduling algorithm should be effective in reducing CPU idle time and should thus improve system efficiency.

#### REFERENCES

- 1. Mattson, R.L. et al., "Evaluation Techniques for Storage Hierarchies," IBM System Journal, Vol. 9, No. 2, pp. 78-117, 1970.

- 2. Denning, P.J., "The Working-Set Model for Program Behavior," <u>Communications of the ACM</u>, Vol. 11, No. 5, pp. 323-333, May 1968.

- 3. Denning, P.J. and S.C. Schwartz, "Properties of the Working Set Model,"

Proceedings of the 3rd ACM Symposium on Operating System Principles,

October 1971.

- 4. Fine, G.H., C.W. Jackson and P.V. McIsaac, "Dynamic Program Behavior Under Paging," <u>Proceedings of the 21st National Conference on ACM</u>, pp. 223-228, 1966.

- 5. Belady, L.A., "A Study of Replacement Algorithm for a Virtual-Storage Computer," <u>IBM System Journal</u>, Vol. 8, No. 2, 1966.

- 6. Coffman, E.G. and L.C. Varian, "Further Experimental Data on the Behavior of Programs in a Paging Environment, "Communications of the ΛCM, Vol. 11, No. 7, pp. 471-474, July 1968.

- 7. Joseph, M., "An Analysis of Paging and Program Behavior," Computer Journal, Vol. 13, No. 1, February 1970.

- 8. Gordon, W.T. and G. F. Newell, "Closed Queueing Systems with Exponential Service," <u>Operations Research</u>, Vol. 15, No. 2, April 1967, no. 245-265.

# Figure Captions

- Average page fault frequency  $m(\tau)$  as a function of working set Figure 1: parameter T.

- Figure 2: Average working set size  $S(\tau)$  as a function of working set parameter  $\tau$ .

- Inter-Page-Fault-Time Distribution

a) Fortran Compiler Figure 3.

- Meta 7 Compiler

Figure 4: A Cyclic Queneing system for modeling CPU and I/O operations.

F6 2

F164

# IIII Systems of Court Two Land

159

160

Evaluation techniques for storage hierarchies

R. L. Mattson, J. Gecsei, D. R. Slutz, and I. L. Traiger

A model of floating buffering

L. J. Woodrum

Interactive Saturn flight program simulator

J. H. Jacobs and T. J. Dillon

Authors

**Abstracts**

Copyright © 1970 by International Business Machines Corporation. All rights reserved. Printed in U.S.A.

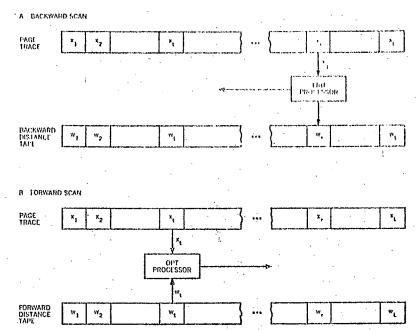

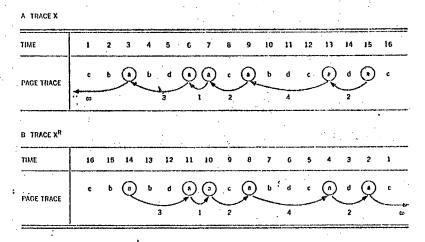

The design of efficient storage hierarchies generally involves the repeated running of "typical" program address traces through a simulated storage system while various hierarchy design parameters are adjusted.

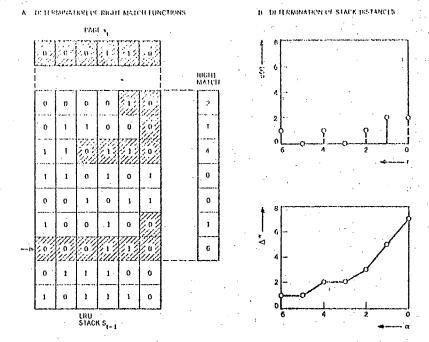

This paper describes a new and efficient method of determining, in one pass of an address trace, performance measures for a large class of demand-paged, multilevel storage systems utilizing a variety of mapping schemes and replacement algorithms.

The technique depends on an algorithm classification, called "stack algorithms," examples of which are "least frequently used," "least recently used," "optimal," and "random replacement" algorithms. The techniques yield the exact access frequency to each storage device, which can be used to estimate the overall performance of actual storage hierarchies.

# Evaluation techniques for storage hierarchies J. Gecsei, D. R. Slutz, and I. L. Traiger

Increasing speed and size demands on computer systems have resulted in corresponding demands on storage systems. Since it has been generally recognized that the speed and capacity requirements of storage systems cannot be fulfilled at an acceptable cost-performance level within any single technology, storage hierarchies that use a variety of technologies have been investigated.

Several previous papers describe the general concepts of hierarchy design<sup>1-3</sup> and evaluation,<sup>4-6</sup> whereas others deal with specific hierarchy systems, such as the core-drum combination on the ICT Atlas computer<sup>7-9</sup> and the cache-core combination on the IBM System/360, Model 85.<sup>10,11</sup>

This paper introduces an efficient technique called "stack processing" that can be used in the cost-performance evaluation of a large class of storage hierarchies. The technique depends on a classification of page replacement algorithms as "stack algorithms" for which various properties are derived. These properties may be of use in the general areas of program modeling and system analysis, as well as in the evaluation of storage hierarchies. For a better understanding of storage hierarchies, we briefly review some basic concepts of their design.

The purpose of a sassociate the information of the Processing Unit of the System with instruction associated with a single device, then to the physical address system with the same of storage devices relatively inexpensive logical address space (or unequal-size segments) of the physical of storage devices relatively inexpensive logical address space (or unequal-size segments).

A hierarchy managerment of pages and between the logical of the hierarchy. Whierarchy managemetion of the corresponding to a fast storage these actions are "tr system (except for the indistinguishable for the corresponding the corresponding the corresponding to the corresponding to

The goal of the hier number of times log being referenced. As directed to the fast, s space is distributed system then acquire while maintaining the less expensive store primary justification

Clearly, many factor hierarchy. On the per and characteristics of the hierarchy, the hierarchy management references. On the coto find and move los as the cost-per-bit a factors, it is quite diff

The typical approach designers has been to at various levels of cl large number of rel olves the through a grameters

mining, in suge 1 sex are 1

ed "stack 4," "least lgorithms. h storage mance of

oms have

Sit it

y requireable the

hierarchy h specific n on the m on the

rocessing"

of a large

classificathms" for

may be of

n analysis,

r a better

ome basic

IBM SYST J

The purpose of a storage system is to hold information and to associate the information with a logical address space known to the remainder of the computer system. For example, the Central Processing Unit (CPU) may present a logical address to the storage system with instructions to either retrieve or modify the information associated with that address. If the storage system consists of a single device, then the logical address space corresponds directly to the physical address space of the device. Alternatively, a storage system with the same address space can be realized by a hierarchy of storage devices ranging from fast but expensive to slower but relatively inexpensive devices. In such storage hierarchies, the logical address space is often partitioned into equal-size pages (or unequal-size segments) that represent the blocks of information being moved between devices in the hierarchy.

A hierarchy management facility is included to control the movement of pages and to effect the (generally dynamic) association between the logical address space and the physical address space of the hierarchy. When the CPU references a logical address, the hierarchy management facility first determines the physical location of the corresponding logical page and may then move the page to a fast storage device where the reference is effected. Since these actions are "transparent" to the remainder of the computer system (except for timing), the logical operation of the hierarchy is indistinguishable from that of a single-device system.

The goal of the hierarchy management facility is to maximize the number of times logical information is in the faster devices when being referenced. As this goal is approached, most references are directed to the fast, small stores whereas most of the logical address space is distributed over the slower, large stores. The storage system then acquires the approximate speed of the fast stores while maintaining the approximate cost-per-bit of the slower and less expensive stores. This increase in cost-performance is the primary justification for storage hierarchies.

Clearly, many factors can affect the cost-performance of a storage hierarchy. On the performance side, one must consider the capacity and characteristics of each storage device, the physical structure of the hierarchy, the way in which information is moved by the hierarchy management facility, and the expected pattern of storage references. On the cost side, the hardware and/or software required to find and move logical information must be considered, as well as the cost-per-bit and capacity of each device. Because of these factors, it is quite difficult to design an "optimal" hierarchy.

The typical approach to hierarchy evaluation employed by computer designers has been to simulate as many hierarchy systems as possible, at various levels of detail. During the first stages of design, a large number of relatively simple simulations may be run with

No. 2 1970

STORAGE HIERARCHY EVALUATION

hierarchy concepts

79

Figure 1 Linear storage hierarchy