DEPARTMENT OF COMMUNICATIONS

.

MINISTÈRE DES COMMUNICATIONS

Volume 3

### Time Shared Systems

- Communications Processor Theory

- Communications Processor Hardware

by

John deMercado

Terrestrial Planning Branch June 1972

QUEEN QA 76.53 .D44 1972 V.3

#### DEPARTMENT OF COMMUNICATIONS

MINISTÈRE DES COMMUNICATIONS

QA 76.53 D44 .v.3 1977 U13

#### Time Shared Systems

#### - Communications Processor Theory

#### - Communications Processor Hardware

## by

#### John deMercado

Terrestrial Planning Branch June 1972 COMMUNICATIONS CAMADA FEB 12 1979 LIBRARY - BIBLIOTHEBUE ...

and the second second second second second second second

· · · ·

a stalja Nastralja

a na shekara a sa araa a

(b) a stranssister set set state

•

#### Acknowledgements

The purpose of these notes is to promote dialogue within the Terrestrial Planning Branch and serve as a basis for our computer-communication systems implementation program.

The notes are only in first draft form and borrow heavily from the references. They should be read in conjunction with the attached reference papers.

As a revised version is planned the author would appreciate any corrections or omissions in the text that were brought to his attention. He also wishes to thank Messrs. John Harris, S. Mahmoud and Kalman Toth for their valuable contributions.

Miss Gail Widdicombe and Miss Yollande Chartrand typed them in record time from an almost unreadable handwritten manuscript.

#### Contents

## Communications Processor Theory

|                                                 | Page |   |

|-------------------------------------------------|------|---|

| Introduction                                    | . 1  |   |

| Methods of Connecting Devices to Memory Modules | 1    |   |

| Multiplexing an Access Path                     | 5    |   |

| Codes                                           | 6    |   |

| Synchronous and Asynchronous Transmission       | 7    |   |

| - A design example                              | 10   | • |

| Line Sharing Techniques                         |      |   |

| - Concentrators                                 | 21   |   |

| - Multidrop and Polling Techniques              | 22   |   |

| Computer Interfaces                             |      |   |

| - Line Buffers                                  | 23   |   |

| - Communications Controller                     | 24   |   |

| Terminal Interface                              | 25   | • |

| Memory Protection                               | 25   |   |

| Control Protection                              | 28   |   |

| - User and System Mode                          | 28   |   |

| - Switching Between User and System Mode        | 28   |   |

|                                                 |      |   |

#### **REFERENCES:**

- 1. W.W. Chu, "A study of asynchronous time division multiplexing for time sharing computer systems", FJCC 1969.

- W.W. Chu, "Demultiplexing considerations for statistical multiplexers", IEEE Transactions in Communication techology June 1972.

- 3. W.W. Chu, "Design Considerations of Statistical Multiplexers" ACM Symposium on Problems in the optimization of data communication systems", October 1969.

- Jack S. Sykes, "Analytical Model of Half-Duplex Interconnections of Computers", IEEE Transactions on Communications Technology Vol. Com.17, No. 2, April 1969.

## Contents (cont'd)

| Communications Processor Hardware                                                                                         | ;       |

|---------------------------------------------------------------------------------------------------------------------------|---------|

| Introduction                                                                                                              | 93      |

| Communications Processor Functions                                                                                        | 93      |

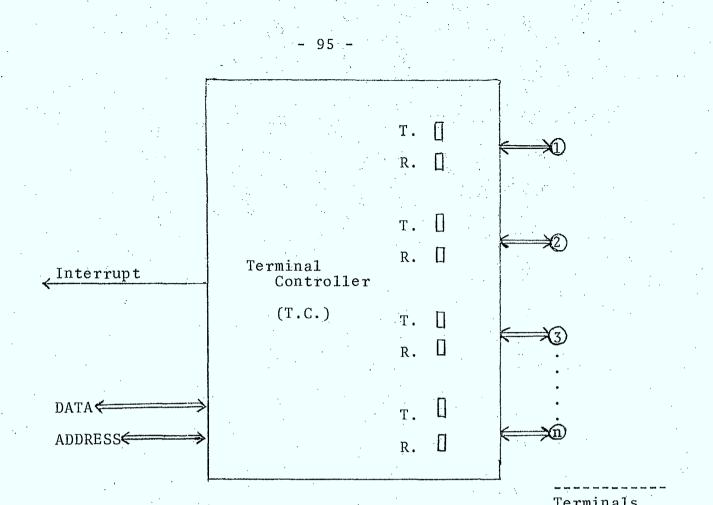

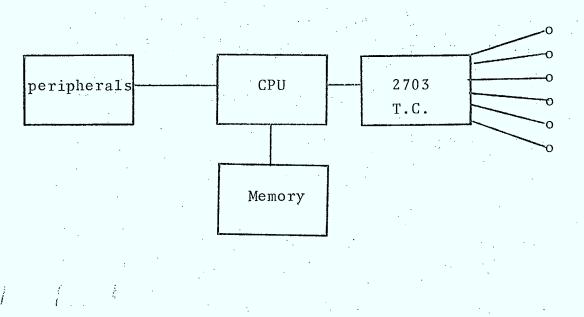

| Terminal Controllers                                                                                                      | 94      |

| Types of Terminal Controllers                                                                                             | 96      |

| Communications Processor Configurations                                                                                   | 96      |

| References for Communications Processor Hardware                                                                          | 99      |

| <ol> <li>Michael Townsend, Communication Control by Comp</li> <li>an Introduction. Telecommunications May 1972</li> </ol> | •       |

| <ol> <li>D. Doll, Planning Effective Data Communications</li> <li>Data Processing Magazine, November 1970.</li> </ol>     | Systems |

3. H. Becker, Communications Processing for Large Data Networks - Data Processing Magazine, November 1970.

## General References

112

•

•

Communications Processor Theory

eory

#### Communications Processor Theory

#### Introduction

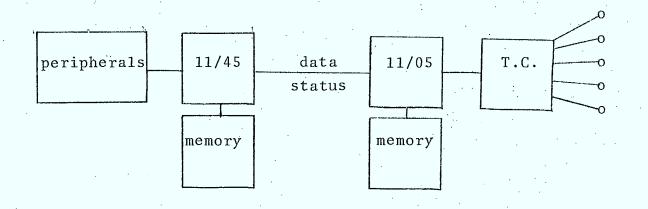

In these notes, a brief outline of the ways in which auxiliary storage and I/O devices gain access to the resources of the main memory is presented. The study of these ways is called Communications Processor Theory. It is conceptually useful to think in terms of conventional communications theory as these theories stand almost in a 1:1 correspondence.

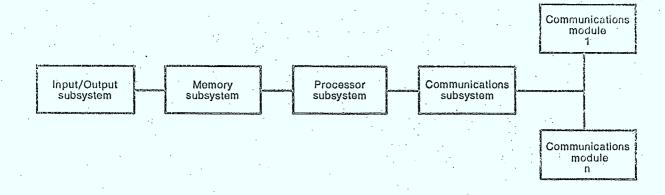

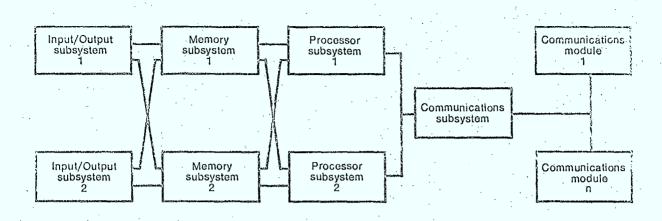

#### METHODS OF CONNECTING DEVICES TO MEMORY MODULES

#### Direct Connection

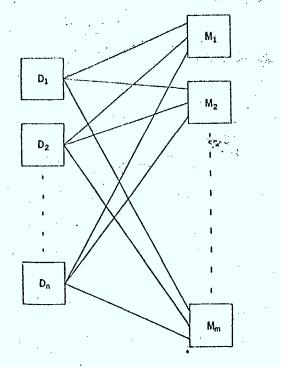

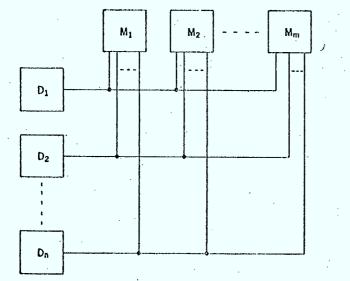

storage and I/O devices is gaining access to a direct-transfer path to main memory. Further, logic is required to determine where in memory to transfer to or from and to determine how much information to transfer. Theoretically, these problems can be solved by providing a direct-transfer path, addressing, and count logic for each device to each memory module. Sùch a scheme is shown in Figure 1. This approach is usually unsatisfactory because of its cost in terms of line-selection logic and line-driving circuits. This cost can be reduced by the use of information available about device and memory information-transfer rates. From Figure 1, it is apparent that a memory module can transfer information to only one device at a time and devices can transfer to only one memory module at a time. Transfer can take place over a maximum of n or m lines, depending on which is larger, but there are n x m lines. Therefore, at a given instant, most of the access lines will be idle, and their associated logic and driver circuitry not used.

A basic problem with auxiliary

Figure 1: Direct communication of n devices with m memory modules (where n > m, usually).

#### Cross-Bar Connection

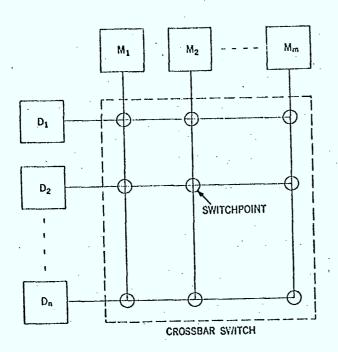

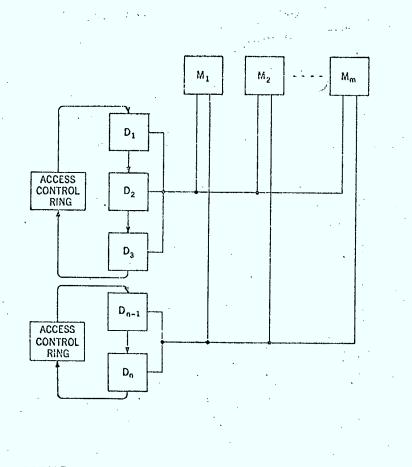

The above fact, suggests that the logic associated with each device should be used to determine which access line to use and the logic associated with each memory module could be used to arbitrate between competing requests for access and centralize it in the interconnection scheme as shown in Figure 2. The logic required, in this scheme, for determining the path between devices and modules is called a <u>crossbar switch</u>. The circled points **cal**led <u>switchpoints</u>, determine the connection path from devices to modules. Conflicts for access to a given module line would be resolved by a priority scheme and analyzed via queuing theory. This use of a crossbar switch reduces the number of line drivers required, but the switching

lîne drive

logic required to set up a transfer path is probably as great as in Figure 1. The crossbar switch however has the disadvantage over the direct-connection scheme in that localizing the switching logic in one central unit makes the system highly dependent on the reliability of the crossbar switch.

Figure 2: A crossbar switch for n devices to communicate with m memory modules.

#### Distributed Connection

The logic of the cross bar switch can be distributed into the memory modules to increase reliability. The resulting organization is shown in Figure 3. In a practical system n is usually larger than m. Thus, not all devices can have access to memory simultaneously, however since devices transfer at varying rates, access paths between them can be shared.

Figure 3: Communication switching distributed into the memory modules for connecting n devices with memory modules.

#### Shared Connection

Some devices transfer at very low rates of a few bits per second, and others transfer at very high rates of hundreds of thousands to millions of millions of bits per second. Therefore, slower devices can share access paths. Figure 4 shows a method of sharing access paths using timeshared (multiplexed) busses.

The limitation of the number of devices which can multiplex a transfer path is determined by the bandwidth of the path and the transfer rates of the devices. The maximum transfer rate of a device must be less than the bandwidth of a path. The maximum transfer rate of all devices on the system which can transfer concurrently is a function of the memory-bus and memorybox bandwidths. This function is a statistical function based on the traffic flow. If at peak transfer points the transfer rate exceeds that of a bus or memory box, <u>saturation</u> is said to occur. For example, all memory busses may be operating below saturation, but the system can be saturated because all busses are trying to access the same memory module. The design goal is to have the system operate near saturation at all times. Without buffering (temporary storage) of information, a saturation condition may cause information to be lost. The amount of buffering required for a device depends on the statistical properties of the system (the distributions of transferrate requirements to the memory modules and busses), the transfer rate of the device, and the cost or possibility of losing information from the device.

- 5 -

There are many tradeoffs between numbers of access paths, bandwidth of access paths, buffering, and the costs of each of these, in order to meet a given information-transfer rate. The concepts discussed above apply to memory-bus structures and to other I/O busses connected to I/O processors, as discussed below.

#### MULTIPLEXING AN ACCESS PATH

Access to a shared transfer path is commonly governed by a control line which runs serially through all devices on the path (Figure 4). The simplest scheme is to assign priority by position in the control ring. When a transfer is completed, control goes to the device requesting access in the highest priority position. With this approach, devices are assigned positions based on worst-case transfer conditions. However, using such a scheme may prevent the path from utilizing its maximum bandwidth. This rigidity is unnecessary if devices can request access to the path with variable priority.

Figure 4: Communication of n devices with m memory modules sharing access paths.

#### CODES

As has been pointed out in the notes in Volume 1 on "Communications Considerations", character information is coded into a string of bits, both for handling by the computer and for transmission. Many codes are in use, but one code format, the ASCII (American Standard Code for Information Interchange) is rapidly gaining widespread use in North America. It encodes 128 characters (see the Table of the code on page 12 of Volume 4 ) into 7 binary information units (bits) and then some equipment uses 1 additional bit to give an error-detection ability, thereby encoding characters in 7 or 8 bits.

#### SYNCHRONOUS AND ASYNCHRONOUS TRANSMISSION

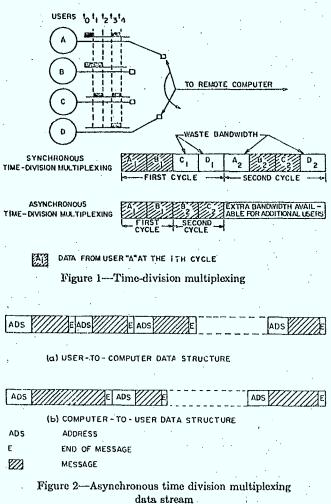

Multiplexing techniques were introduced to increase channel utilization and thus reduce the communication costs in time-sharing systems. Two techniques are commonly used for this purpose. These techniques are also discussed in the volume 1 on Communications Aspects.

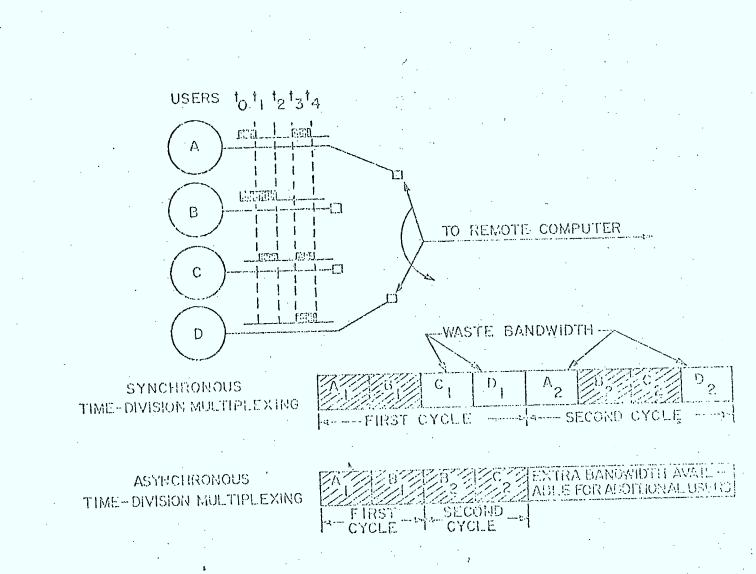

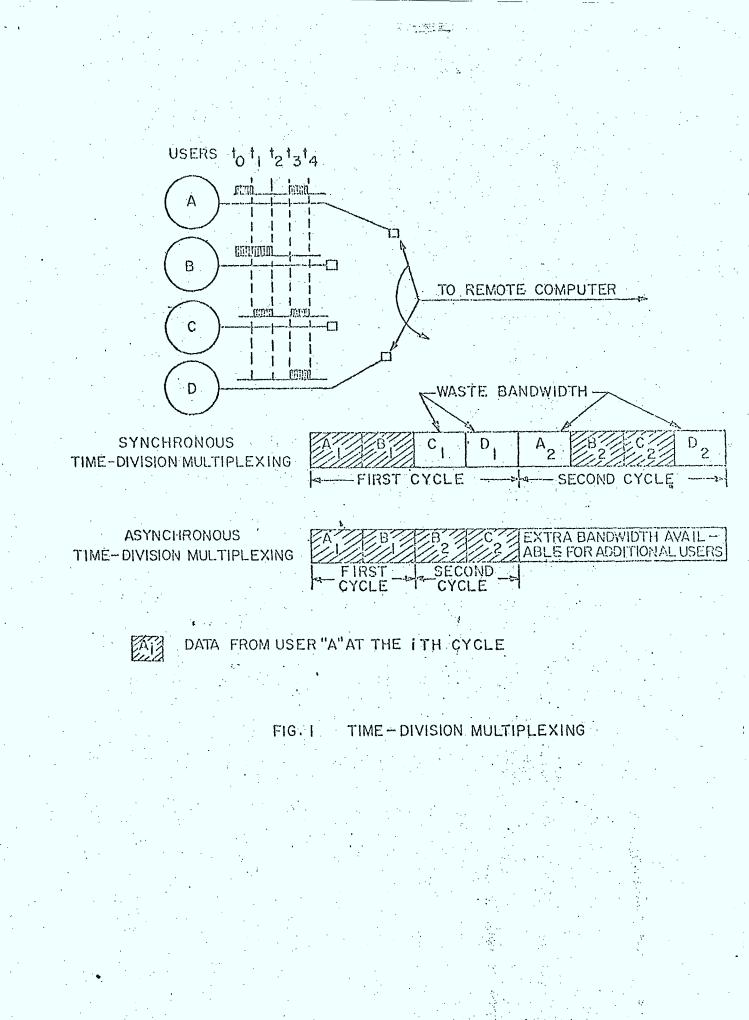

#### 1. Synchronous Time Division Multiplexing (STDM)

Example: consider the transmission of messages from terminals to computer, each terminal is assigned a fixed time duration. After one user's time duration has elapsed, the channel is switched to another user. The main advantage of STDM is that buffering is limited to one character per user line and thus addressing is usually not required.

STDM has certain disadvantages which can be realized immediately from the fact that any terminal is assigned a fixed time duration, whether it is idle during this time or not makes no difference to the multiplexer. Thus the channel remains idle during certain time durations (assigned to idle terminals). This is an inefficient utilization of the communication channels. Data collected from several representative operating time sharing systems revealed that during an average call, 95% of the user-to-computer channel and 65% of computer-to-user channel are idle.

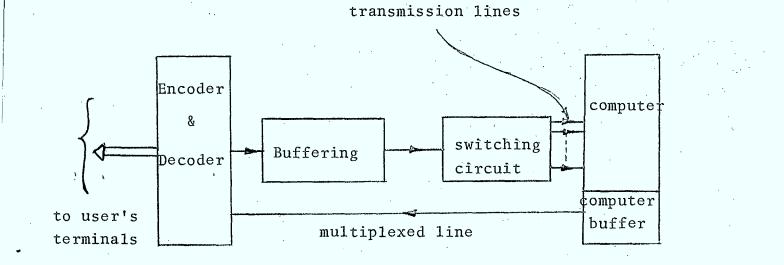

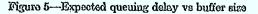

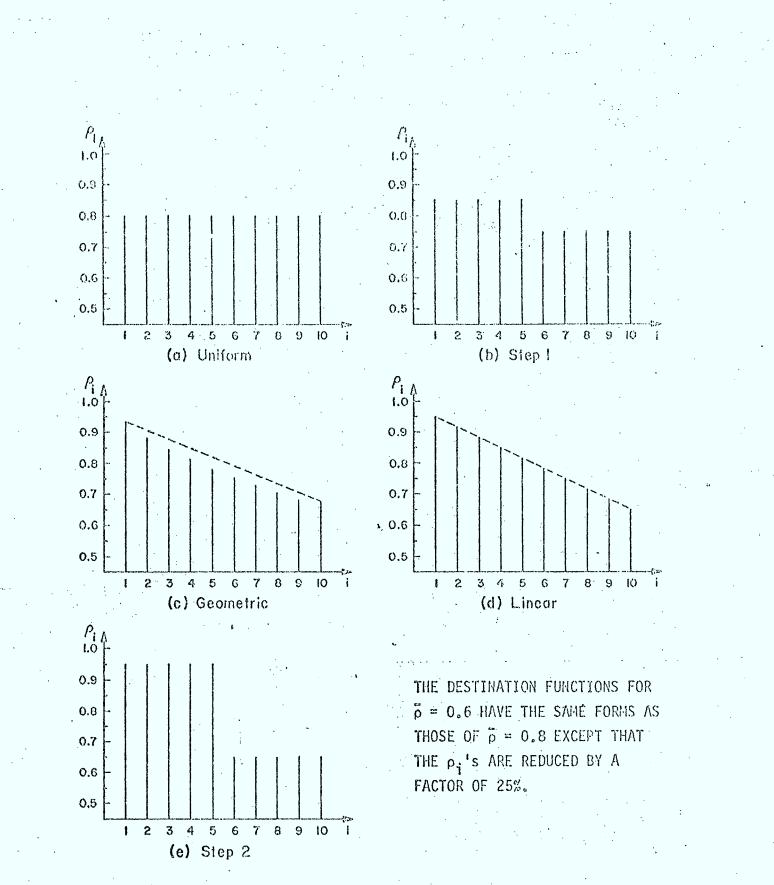

# Asynchronous Time Division Multiplexing (ATDM) (see Fig. 5) (Statistical Multiplexers)

The multiplexer here switches from one user to another user whenever the one user is idle, and asynchronously time multiplexes the data. With such an arrangement, each user would be granted access to the channel only when he has a message to transmit. The crucial attributes of such a multiplexing technique are:

- a) an address is required for each transmitted message;

- b) buffering is required to handle the statistical peaks in random message arrivals (see figure 6).

An operating example of an ATDM system for analog speech is the "Time assignment speech Interpolation" (TASI) system used by the Bell system on the Atlantic Ocean Cable. The ATDM systems operate efficiently under the following conditions:

- 1) Low overflow probability (same or lower order of magnitude as the line error rate).

- 2) An acceptable expected message queuing delay due to buffering.

To study the overflow probability and the expected message queuing delay, analyses of the statistical behaviour of the buffer are needed (see Chu (1) for detailed discussion of this topic).

We shall discuss now the design aspects of these statistical multiplexers and try to identify the trade-offs among the different design considerations.

An optimal multiplexer is the one that yields minimum operating costs and at the same time satisfies the required performance (delays and overflow probabilities). The operating costs of the multiplexers can be divided into transmission costs and storage costs. The transmission costs are dependent on the transmission rates of the lines and the number of lines used. The storage costs are dependent on the buffer length required, the cost of overhead in buffer management, and the cost of waste spaces of fixed-size messages. The queuing delays imposed by multiplexers are dependent, for example, on delays due to buffering, and computer scheduling algorithms.

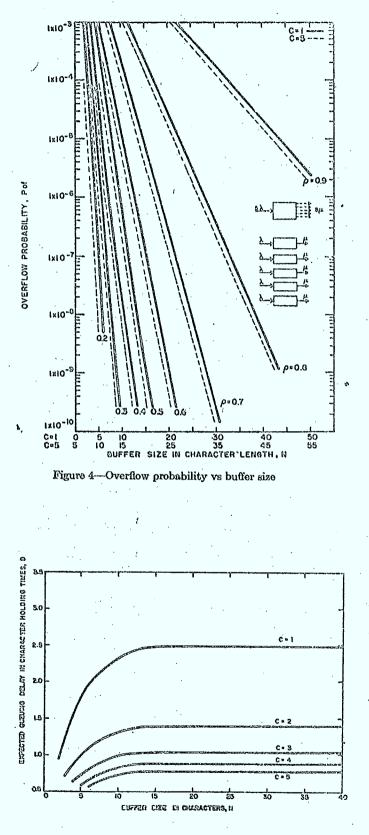

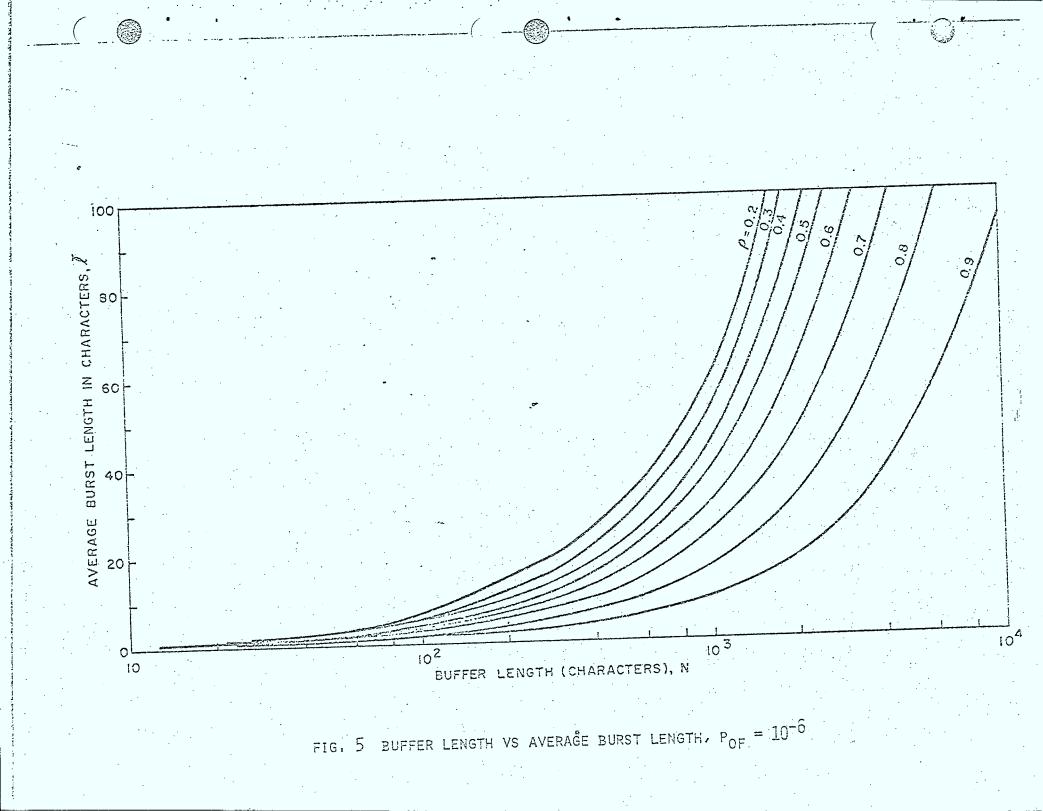

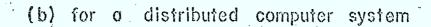

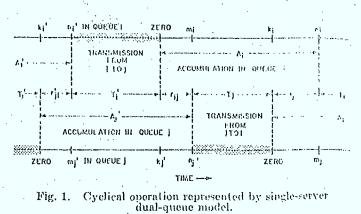

Figure 5 shows the components of a statistical multiplexer. The asynchronous multiplexer's buffer behaviour can be analyzed by queuing models with finite waiting lines.

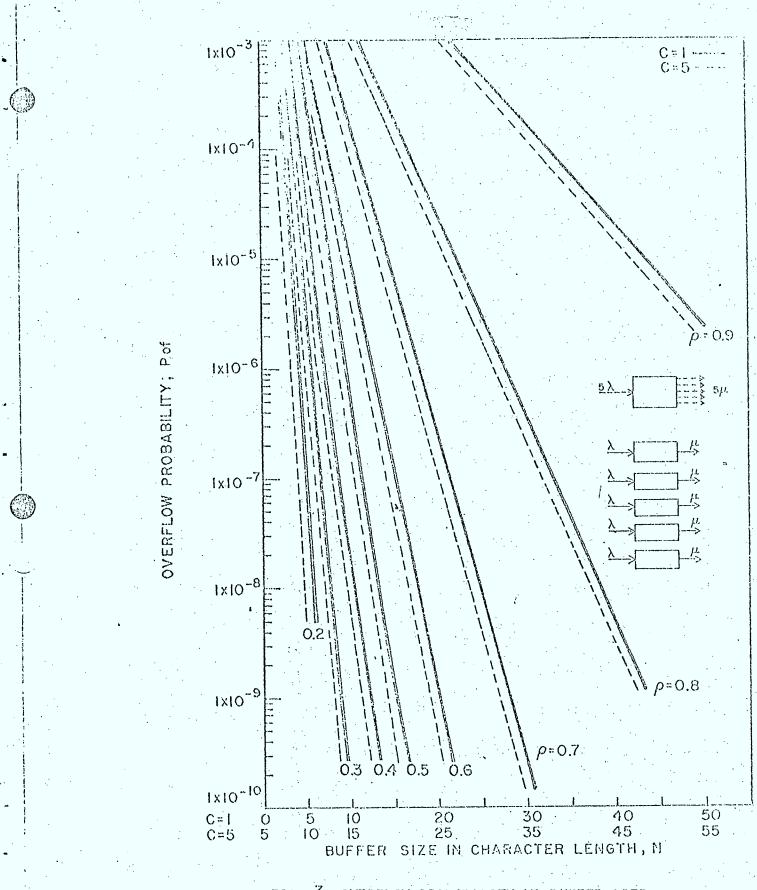

In describing the buffer behaviour, we are interested in the following parameters:

| Pof |      | of the total number of characters that overflow<br>from the buffer).                 |

|-----|------|--------------------------------------------------------------------------------------|

| Р   | 15.1 | traffic intensity (a measure of the degree of congestion of the multiplexed channel) |

| D   | Ξ    | expected queuing delay                                                               |

| N   | 11   | buffer size                                                                          |

| 0   | Ξ    | the average length of a burst (string of                                             |

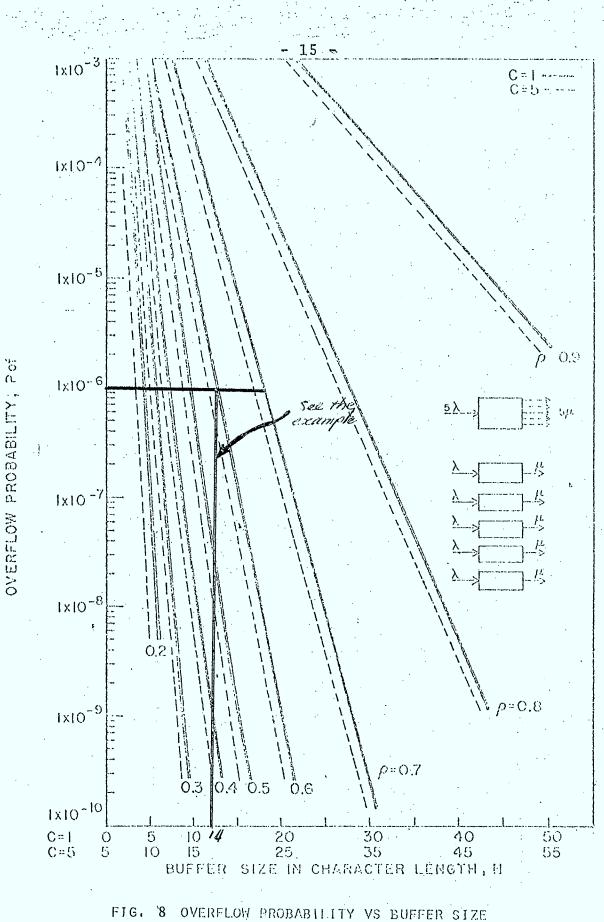

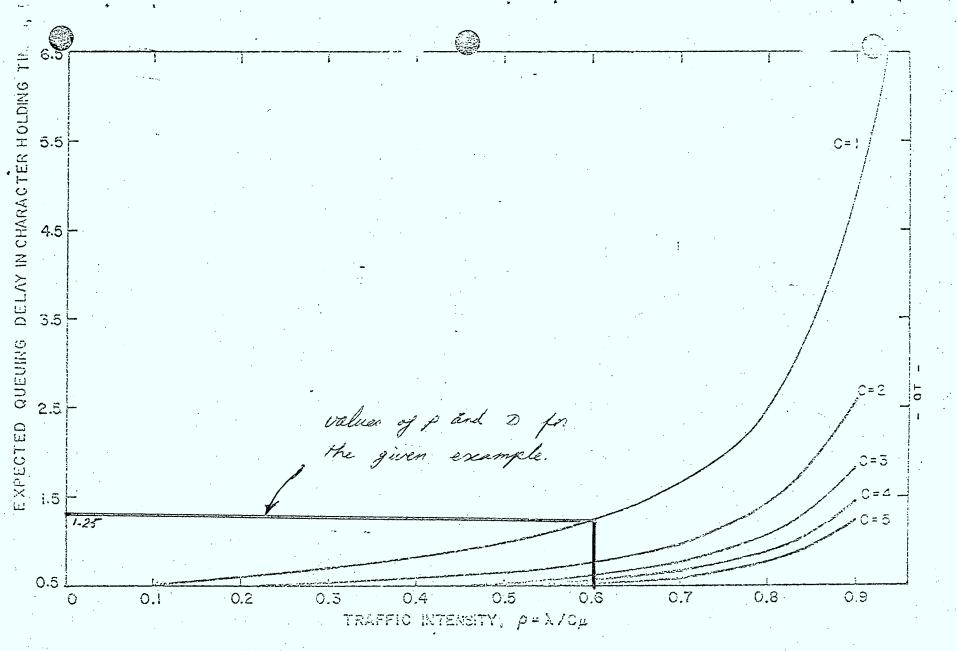

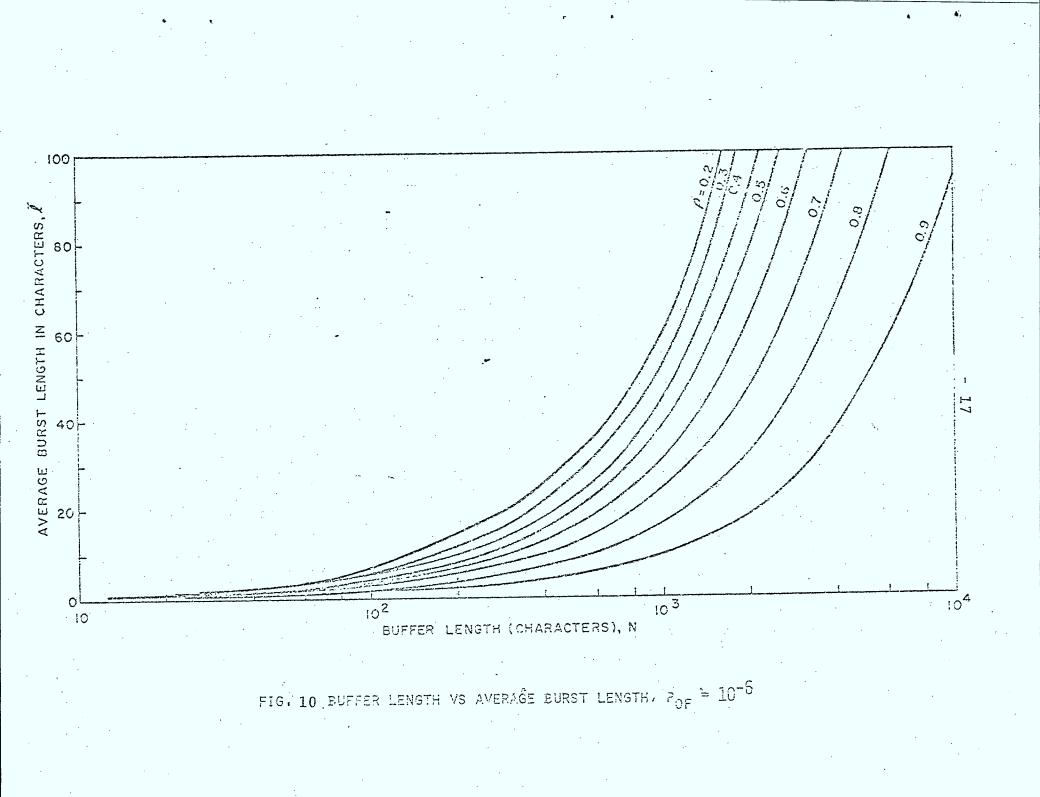

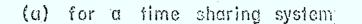

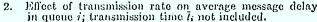

Studies of several existing time sharing systems revealed some results that relate the previously mentioned parameters (figures 8, 9,10,11,12 and 13, Chu (3)).

characters).

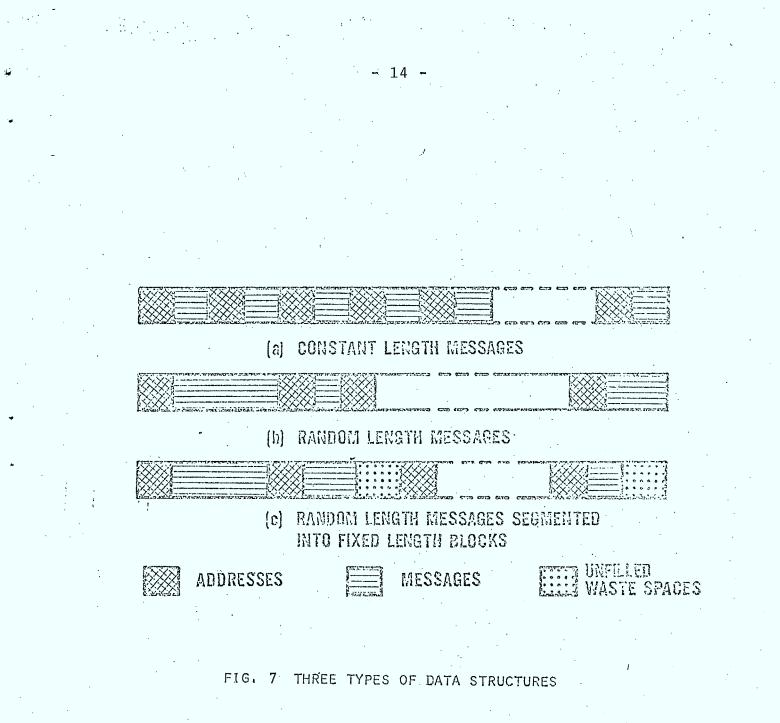

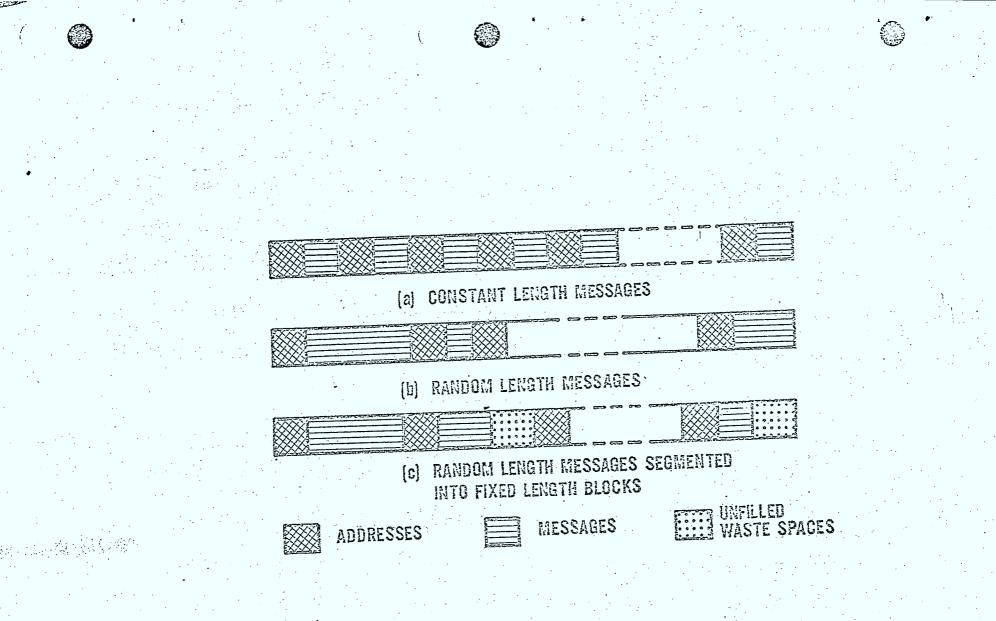

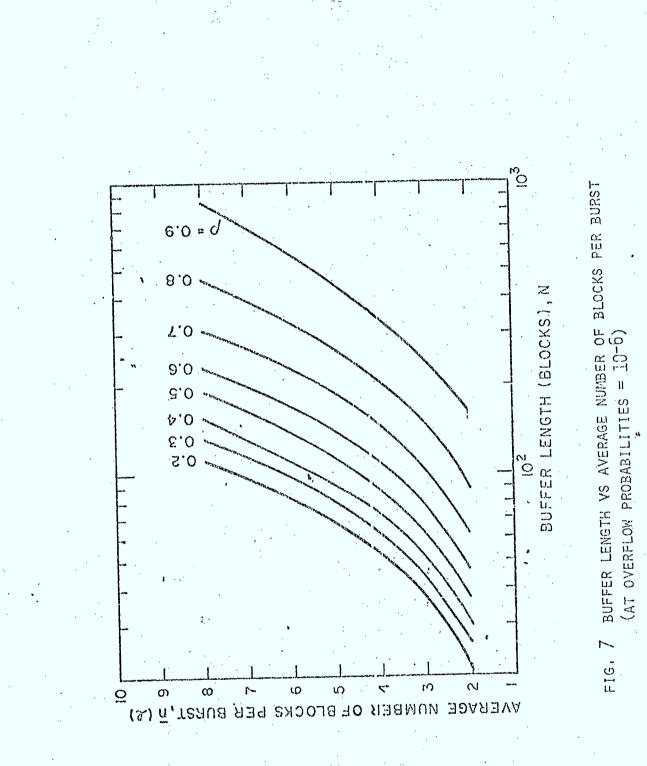

Three types of messages are commonly considered in the design of the statistical multiplexers (figure 7).

- 9 -

The constant length/message model corresponds to the user-to-computer traffic where users type characters one at a time at the terminal.

The random length messages correspond to the computer-to-user traffic. The central processor of a timesharing computer sequentially performs fractions of each user's job and the output traffic to the users is strings of characters which are called bursts. The random nature of the message length greatly complicates the problem of storage allocation. A way to simplify this problem is to segment messages into fixed-sized blocks. An address as well as linking information to subsequent blocks is assigned to each Since each block has an address and is uniform in block. size, a block can be stored in any vacant position in the buffer. Thus the storage allocation problem is greatly simplified. The wasted storage space created by segmentation is:

> some number of address characters to identify each block and to link the subsequent blocks.

2) the unfilled space of the last block.

The trade-off between the extra storage cost and the saving in buffer management is the main consideration to decide whether the random length messages should be segmented into fixed-sized blocks.

#### A design example:

Consider the design of a time-sharing system that consists of many remote terminals and that employs the ATDM technique with full duplex operation between the terminals and the central processor.

The typical value of the character interarrival time per user line can be approximated as exponentially

distributed with mean 0.5 seconds (from the study of several operating systems). Thus the character arrivals can be treated as Poisson arrivals with a rate = 2 char/sec. Voice grade private lines can easily transmit 240 char/sec. from users. Suppose this operating system consists of m = 48 terminals, and assume all the terminals to be statistically independent and have the same average traffic characteristics.

The buffer should be designed such that the overflow probability is less than  $10^{-6}$ .

<u>Requirements</u>: determine the buffer size and the queuing delay incurred by each character.

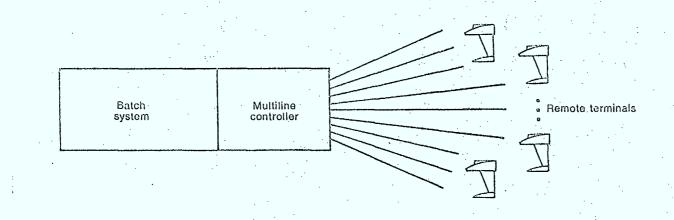

P = traffic intensity = 1.5 x 48 x 2/240 = 0.6

where total no. of characters/sec = no. of terminals x characters/ sec/terminal

= 48 x 2.

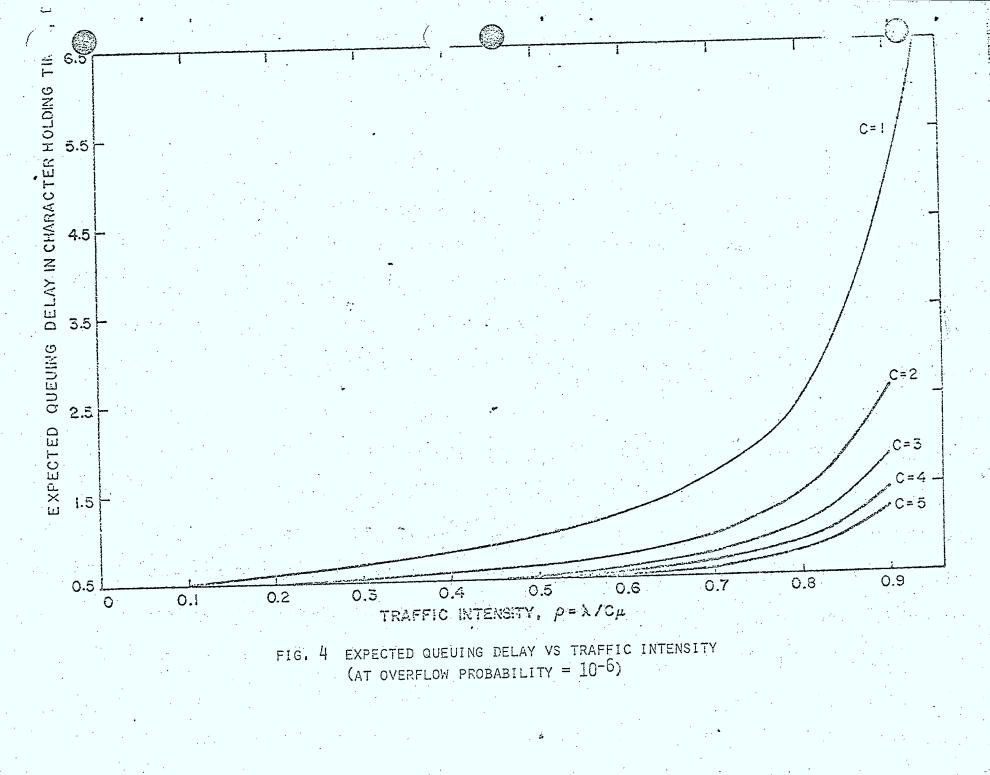

and the factor (1.5) is introduced to account for the characters necessary for addressing and framing (assuming 50% of the source information is necessary for that purpose.) From figure 8 the buffer size that corresponds to  $P_{of} = 10^{-6}$  and P = 0.6is 14 character length. From figure 9, the normalized queuing delay due to buffering is equal to 1.25 character holding times. Since each character holding time is equal to  $\frac{1}{10} = \frac{1}{240}$  m.sec.

= 4.16 millisecond, the waiting time of each character is 5.06 milliseconds.

FIGURE 5

Asynchronous time division multiplexing system for time sharing computer communications.

## Note: the switch circuit is used when we have more than one transmission line.

- 12 -

١

DATA FROM USER "A" AT THE ITH CYCLE

## FIG. 6 TIME-DIVISION MULTIPLEXING

- 13 -

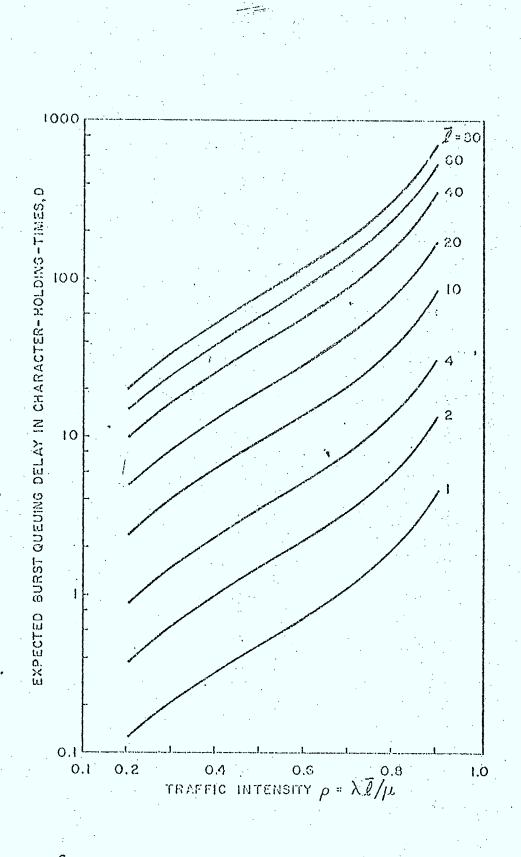

FIG. 9 EXPECTED QUEUING DELAY VS TRAFFIC INTENSITY (AT OVERFLOW PROBABILITY =  $10^{-6}$ )

¥. .

1000 7=00 60 40 EXPECTED BURST QUEUING DELAY IN CHARACTER-HOLDING-TIMES, D 20 100 10 10 1

0.4 0.6 0.8 TRAFFIC INTENSITY  $\rho = \lambda \vec{l} / \mu$

1.Ó

0.1

0.1

0.2

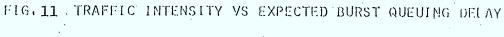

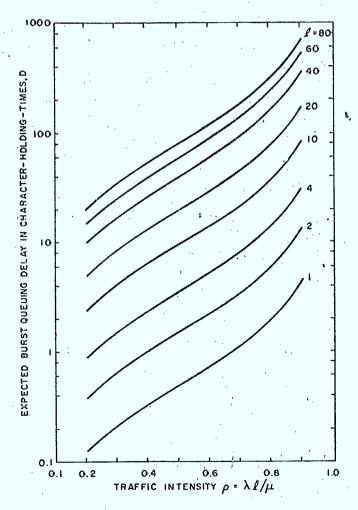

## FIG. 12 BUFFER LENGTH VS AVERAGE NUMBER OF BLOCKS PER BURST (AT OVERFLOW PROBABILITIES = $10^{-6}$ )

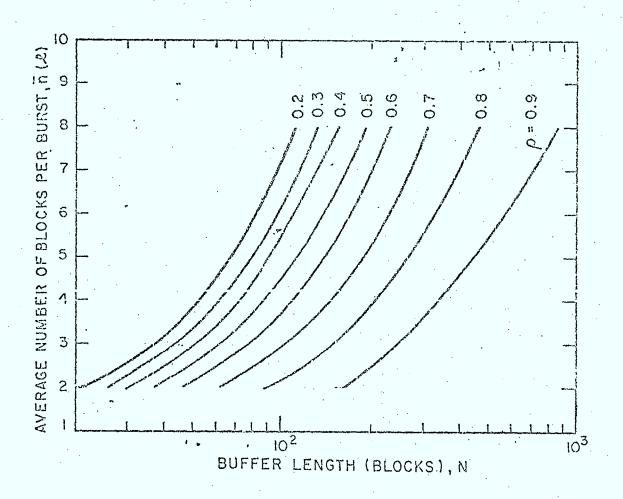

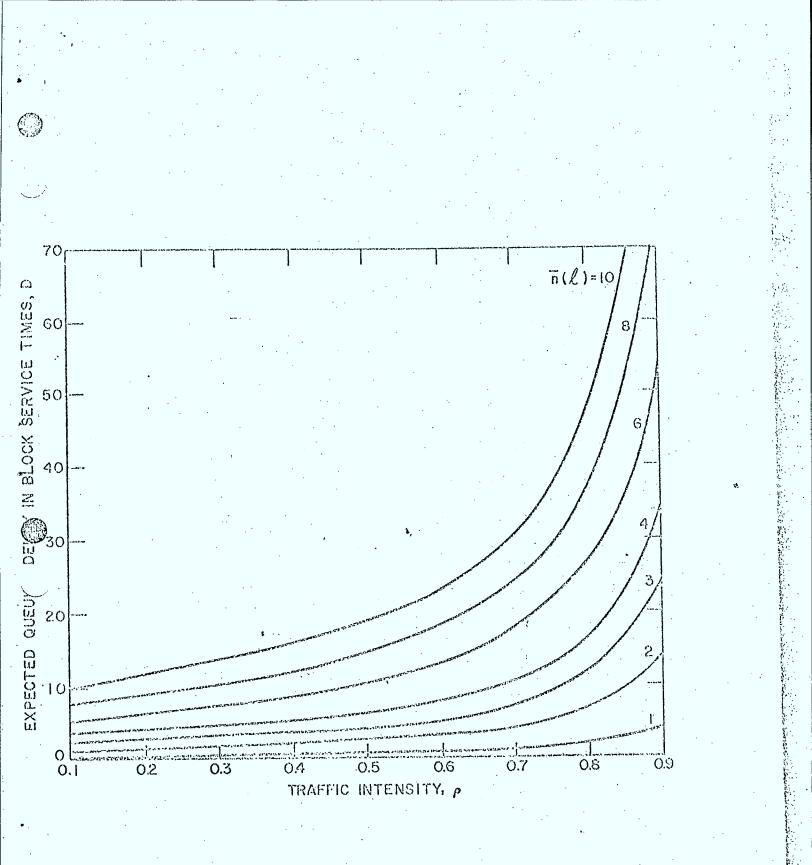

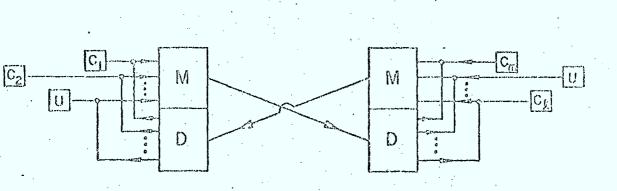

# FIG. 13 EXPECTED QUEUING DELAY VS TRAFFIC INTENSITY (AT OVERFLOW PROBABILITIES = $10^{-6}$ )

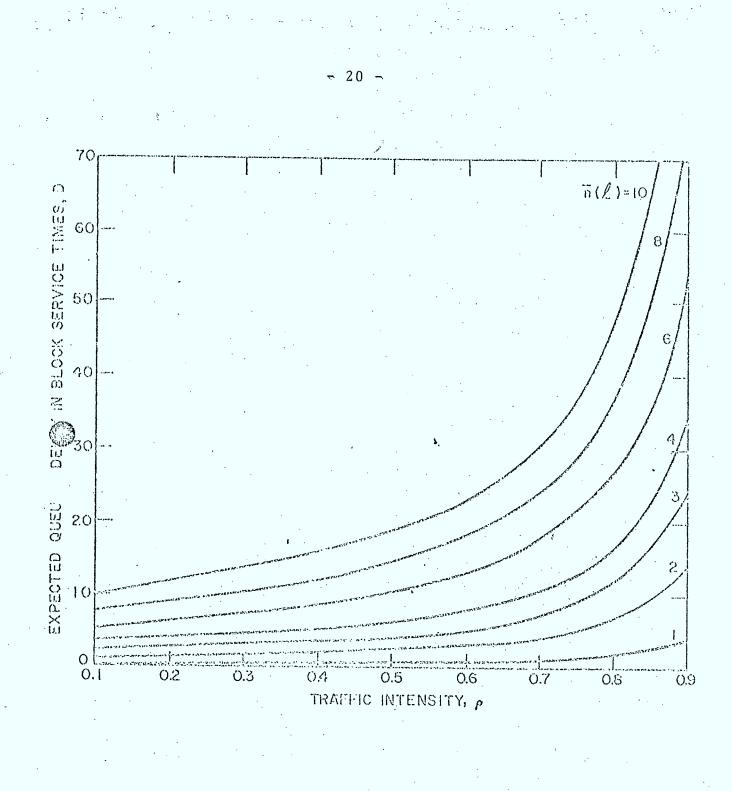

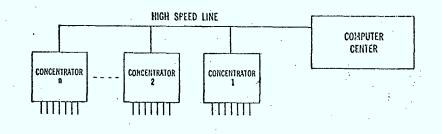

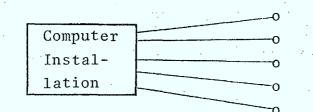

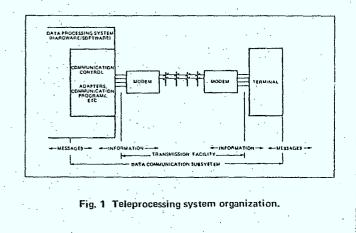

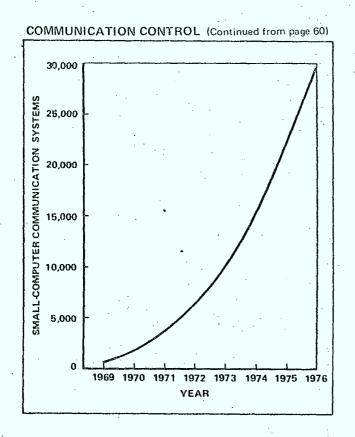

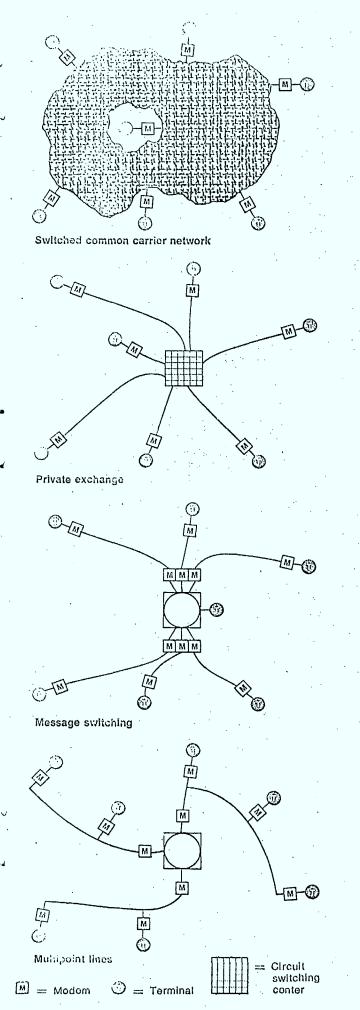

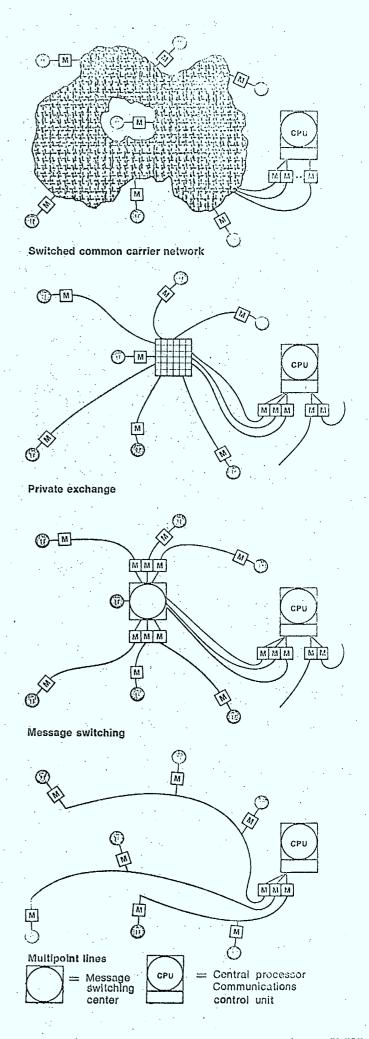

#### Concentrators

Rental of communication lines, particularly highspeed lines over long distance, is expensive and therefore a number of techniques have been developed to share this resource among several terminals. For example, a commercial timesharing service might have a machine in Tel-a-viv and customers in Jerusalem, Haifa and Gaza. The average customer wont want to pay long-distance rates and the timesharing firm could lease one telephone line between each of these places and its central computer and place a concentrator in Haifa, Gaza and Jerusalem. The customer then dials the computer with a local number and is connected with the concentrator. As far as the customer is concerned, he has made direct contact with the computer. The concept is illustrated in Figure 14.

Concentrators are usually small computers that collect messages from the users in a given area, via lowspeed asynchronous telephone lines. The concentrator then transmits the messages over the high-speed leased line to the computer, either asynchronously or synchronously. A message contains a special character or characters, such as a carriage return, recognized by the concentrator. When the concentrator recognizes and end-of-message character from a user, it enters the user's message, preceded by information to identify the user, in a buffer. The output of the buffer then feeds a high speed telephone line.

Messages from the central computer are sent to the concentrator preceded by appropriate identification. The concentrator then sorts the messages into buffers for each user and transmits them to the user at slow speed. With this technique, an expensive resource, namely the long distance telephone line, is shared by several users.

#### Multidrop and Polling Techniques

It is possible to have several concentrators on one line or to attach several terminals to one line. This can be done, using a technique called <u>multidrop</u> for sending information to terminals and called <u>polling</u> for receiving information from terminals. With multidrop, the message is preceded by a device address and followed by an end-of-message character or characters. The message is sent down the line, and all devices decode the address; only the device addressed connects itself to the line. When the end-of-message character is received, the device disconnects itself. The network may be able to precede the message with several addresses or have a <u>broadcast</u> code indicating that several or all devices should receive the message. This concept is illustrated in Figure 15. - 23 -

Figure 15: Communications where several concentrators share one line.

Only one device can transmit to the computer at a time, and the line is organized by polling the devices under computer control. A <u>polling message</u> is sent down the line, which asks "terminal X do you have anything to transmit?" Terminal X replies with a code for yes or no. If the answer is "no" the next polling message is sent.

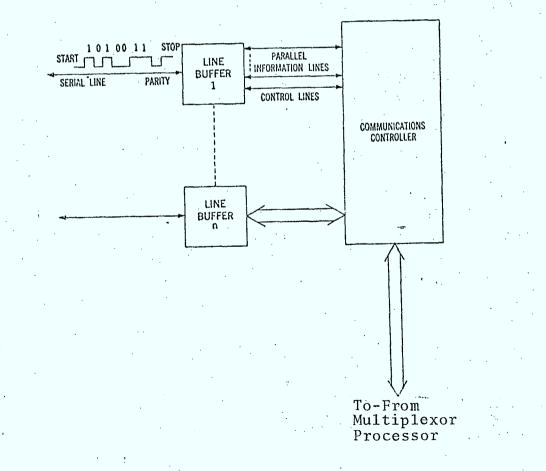

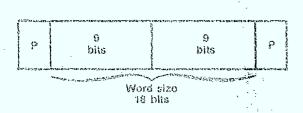

#### Line Buffers

The incoming serial string of bits at the computer interface must be converted into 8 parallel bits representing a character and stored in a buffer register. To accomplish this function required stripping off the start and stop bits on asynchronous transmission. The error-detection bit may also be utilized to check the transmission at this time. Similarly on output, the parallel bits representing a character must be converted to serial form and have the start/ stop bits added. An error-detection bit may also have to be added if the character is represented in the computer without the error-detection bit. These functions are performed by a device commonly called a line buffer. The concept is illustrated in figure 16 The line buffer has additional tasks of sending and receiving control signals to data sets to connect, disconnect and for proper synchronization. The line buffers also receive status information from the modems indicating, for example, whether or not they are still connected to the line. This status information can be tested by the

computer, or it can be used to generate a signal if the state of the line changes. These functions are important for automatic answering of the line and to avoid system difficulties. on accidental or erroneous disconnect. When such a disconnect occurs, it is important that the user on that line be automatically logged out, in order to free the line and protect the user. There is one line buffer for each line.

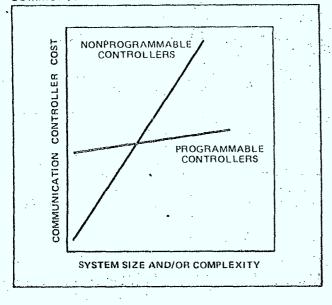

#### Communications Controller

The line buffers must in turn communicate with main memory. This communication is handled by attaching the line buffers to a device commonly called a <u>communications</u> controller.

Figure 16 The communications line interface at the computer.

Timesharing systems/are increasingly called upon to handle terminals with a variety of transmission speeds from 110 to several thousand bauds. It is important that new devices be easily interfaced without major hardware or software modifications. These goals cannot be easily achieved with the simple communications controller described above, which scans each line in sequence, and a communications controller with a variable-priority system is usually required. Such a device, after completing a service request, would simultaneously scan all line buffers requesting service and service the one with the highest priority next.

In some systems, the communications controller is connected to a separate small computer which allows a number of processing tasks to be performed, such as editing, message assembly, file creation, and so forth, without interfering with the work of the central machine.

#### The Terminal Interface

The terminal is the point of interface between the user and the system. It is here that the capabilities of the man and the machine must be matched. There are many terminals available from manufacturers which can usefully be classified into typewriter, cathode-ray tude, and special-purpose terminals. These are discussed in more detail in Volume

#### Memory Protection

Memory protection is a problem common to all time-sharing systems. It can be approached in a variety of ways. Protection is needed in general for two reasons, namely intentional and accidental attempts to address the wrong areas of memory. In a system serving a number of users, there is frequently a need to keep information confidential. Human nature being what it is, it is conceivable that one person would want to look in on someone else's information. Mistakes can be made by both humans and equipment. Mistakes can be costly in that they can destroy information, or even disrupt operation.

It is therefore necessary to allow certain areas of memory to be accessed only under tightly-controlled conditions. This protection can be accomplished by software or a combination of software and hardware. Either approach involves a responsibility on the part of the executive program.

The essential technique is to check addresses as they are generated to make certain they are valid. Many time-sharing CPU's include special registers which automatically check addresses. These registers are set by the executive when the program is entered. They define the limits of memory to be accessed by the program. If an address is called for which lies outside the limits, the execution is automatically trapped for checking.

Other memory protection schemes use various types of codes -- or combination locks. A code might be contained within a user number (or determined from a table keyed to user numbers) which would define the areas of memory and storage open to that user. If a user or his program attempted to address any other area, the execution would again be trapped. Codes can be inserted at the beginning of pages to indicate which users are to have access to the information. Such codes could also indicate if the information in the page was to be read only, and not changed, by users. The code could also indicate if the contents were executable by a user but not readable by him. A case in point might be a grading routine in a computer-assisted-instruction situation.

- 27

In a random file, it might be necessary to prefix a small code to each item to indicate whether it holds permanent or temporary information. Random files also encounter the possibility of two users requesting the same information -- such as a stock number or airline flight. Such events must be guarded against so that one updating can't occur until the other has been completed. The executive might check a table of information in use and place the second request on a queue until the first transaction has been completed.

Magnetic tape offers a built-in form of protection in that read and write operations can't occur at the same time. Before a tape file is "opened" for either reading or writing, the executive can require a check of the label at the beginning of the tape to ascertain that it is the correct one. When a tape is "closed" a master table can be updated giving the location of data and an indication of its status. Code words could also be used on magnetic tape to prevent the reading of confidential information unless the user or program presented the proper combinations.

Memory protection is usually pronounced in general purpose systems where users have more control over what the computer does. In single application systems, where only precoded programs are used, protection schemes are often less complete. For example, in a savings system, a teller at his terminal could not create instructions to read records from another institution. Thus, protection at the teller level would be necessary. Management terminals might have the capacity to insert special instructions into the system, so memory protection might be necessary at this level.

#### Control Protection

Certain instructions in the machine are usually not generally available for any process to execute. For example, processes are usually prevented from directly performing I/O instructions because other processes may be using a particular device. All attempts to perform I/O operations generally go through the system so that these requests for service can be scheduled. Further, user processes must be prevented from halting the machine or executing any other instructions which might interfere with the system or other users.

2.8

#### User and System Mode

To handle the above problem, many machines are designed to operate in two modes, usually called <u>system mode</u> and <u>user mode</u>. In system mode, all instructions in the machine are executable. In user mode, certain classes of instructions, called privileged instructions, are prohibited. If an attempt is made to execute a privileged instruction, a fault interrupt is generated which transfer control to the system.

#### Switching Between User and System Mode

The problem of communications between modes is one requiring careful consideration, because if the design of the mode switching scheme has not been carefully considered, programming can be awkward and time can be wasted in extra checking on the validity of the calls between modes.

A straightforward mode-switching scheme, implemented on the XDS-940 utilizes programmed operations. The programmed-operator concept is in effect a method for making subroutine calls logically appear to the user as machine instructions. When a bit in the instruction word signifying a programmed operator is detected, the bits which are normally interpreted as the operation code are then interpreted as an address to which control is transferred. Two types of programmed operator exist on the XDS 940: 1) a system programmed operator in which the transfer is made to locations in the system code and the mode is switched to system mode (the previous mode is saved) and 2) a user programmed operator in which transfer is made to locations in the user's process. All calls to the system for assistance are thus made with system programmed operators. To return from system mode to user mode, the system executes a jump instruction addressed through the user map rather than the system map. While in system mode, the system can access locations in user processes by use of the user map. Besides giving a simple interface between modes, the programmed operator concept allows the user to think he is programming a machine different and more powerful that that provided by the bare hardware.

- 29 -

Reprinted from – AFIPS – Conference Proceedings, Volume 35 Copyright © by AFIPS Press Montvale, New Jersey 07645

# A study of asynchronous time division multiplexing for time-sharing computer systems

#### by W. W. CHU®

Bell Telephone Laboratories, Incorporated Holmdel, New Jersey

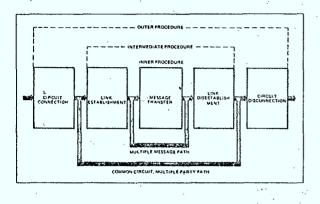

# INTRODUCTION

In order to reduce the communications costs in timecharing systems and multicomputer communication systems, multiplexing techniques have been introduced to increase channel utilization. A commonly used technique is Synchronous Time Division Multiplexing (STDM). In Synchronous Time Division Multiplexing, for example, consider the transmission of messages from terminals to computer, each terminal is assigned a fixed time duration. After one user's time duration has elapsed, the channel is switched to another user. With synchronous operation, buffering is limited to one character per user line, and addressing is usually not required. The STDM technique, however, has cortain disadvantages. As shown in Figure 1, it is inefficient in capacity and cost to permanently assign a segment of bandwidth that is utilized only for a portion of the time. A more flexible system that efficiently uses the transmission facility on an "instantaneous time-shared" basis could be used instead. The objective would be to switch from one user to another user whenever the one user is idle, and to asynchronously time multiplex the data. With such an arrangement, each user would be granted access to the channel only when he has a message to transmit. This is known as an Asynchronous Time Division Multiplexing System (ATDM). A segment of a typical ATDM data

stream is shown in Figure 2. The crucial attributes of such a multiplexing technique are:

- 1. An address is required for each transmitted message, and

- 2. Buffering is required to handle the random measage arrivals.\*\*

If the buffer is empty during a transmission interval, the channel will be idle for this interval.

An operating example of an ATDM system foranalog speech is the "Time Assignment Speech Interpolation" (TASI) system used by the Bell System on the Atlantic Ocean Cable.<sup>1</sup> Using TASI, the effective transmission capacity has been doubled and the system operates with a negligible (with respect to voice transmission) overflow probability of about 0.5 percent, even without buffering.

The feasibility of the ATDM system depends on: (1) An acceptably low overflow probability—of the same or lower order of magnitude as the line error rate—that can be achieved by a reasonable buffer size, and (2) an acceptable expected message queuing dolay due to buffering. To estimate these parameters, analyses of the statistical behavior of the buffer are presented below. The user-to-computer traffic is in

<sup>\*</sup> Present address: Computer Science Dept., UCLA, Los Angeles California, 90024.

<sup>&</sup>lt;sup>26</sup> There may be other reasons for providing buffering such as: tolerating momentary loss of signals (e.g., fading), momentary interruptions of data flow, permitting error control on the line, etc. Under these conditions, the buffer should be designed to satisfy also the above specific requirements.

Fall Joint Computer Conference, 1969 670

system for time-sharing computer communications from the sources to the buffer are assumed to be generated from a renewal counting process; that is, the character interarrival times are independent and identically distributed. Since the line transmits with constant speed, the time it takes to transmit each fixed length character (service time),  $1/\mu$ , is assumed to be constant. For reliability and simplicity in data transmission, synchronous transmission is assumed. The data are taken out synchronously from the buffer for transmission at each discrete clock time. The data arriving at the buffer during the periods between clock,

ning of the next clock time, even if the transmission <sup>1</sup>, facility is idle at the time of arrival. In queuing theory terminology, the above system implies there is a gate between the server and waiting room which is opened at fixed intervals. Thus we shall analyze the queuing modelt with finite buffer size (waiting line) and synchronous multiple transmission channels (servers). Powell and Avi-Itzhak<sup>2</sup> analyzed a similar queuing model with an unlimited waiting line. Birdsall,<sup>8</sup> and later Dor' analyzed a queuing model with limited waiting room but with a single server. In here, the model is generalized to accommodate multiple servers with limited waiting room.

> To establish the set of state equations for analysis of a buffer with a size of N characters and c servers, we assume that the system has reached its equilibrium. Let  $p_n$  be the probability that there are exactly n characters in the system (in the buffer and in service) at the end of a service time, and a, be the probability

> times have to wait to begin transmission at the begin-

units characters, while the computer-to-user traffic is in units strings of characters which we shall call bursts. The length of the bursts are different from one to another and are treated as random variables. Because of the asymmetrical nature of the traffic characteristics, the statistical behavior of the buffer in the user-tocomputer multiplexer and the computer-to-user multiplexer are quite different and, therefore, are treated separately. An example is given to illustrate the multiplexer design in a time-shared computer-communications system that employs ATDM technique.

#### Analysis of buffer behavior

#### User-to-computer buffer

An ATDM system consists of a buffer, encoding/ decoding circuit, and a switching circuit (in the case of multiple multiplexed lines) as shown in Figure 3. For the analysis of the statistical behavior of user-tocomputer buffer, the character (fixed length) arrivals

OUFFERS รพกรีมม CONFOR ENCODIN нюбозо USERS RULTIPLEXED UFFERIN Figure 3-Asynchronous time division multiplexing

LINES

<sup>†</sup> The results derived from this study can also be used as a conservative estimate (upper bound) for the case in which the lines are permitted to transmit the characters arrived during the service interval. The estimate yields better approximation for the heavy than light traffic intensity case. Because under heavy traffic case, the lines are usually all busy and the characters that arrive during the service interval have to wait and cannot be serviced during the service interval. The maximum over design in a buffer system with e transmission lines that permits to transmit the characters arrived during service interval is c characters.

there are no more than c characters in the system at that time, i.e.,

9

$$p_o = \sum_{i=0}^{o} p_i \qquad (1)$$

Without loss of generality, we can let the service interval equal to unity. We shall express the probability of number of characters present in the buffer at the end of the unit service time interval (left side of equation (2)) in terms of the probability of the number present in the system at the beginning of the interval (right side of equation (2)), multiplied by the probability of a given number of characters arriving during the service interval. As this can occur in different combinations, we add the probabilities. With synchronous transmission, all characters in service would finish their service and leave this system at the end of a service interval.

Thus in a unit service interval of time, we have

$$p_{0} = a_{0}\pi_{0}$$

$$p_{1} = a_{0}\pi_{1} + p_{0+1}\pi_{0}$$

$$p_{2} = a_{0}\pi_{2} + p_{0+1}\pi_{1} + p_{0+2}\pi_{0}$$

$$p_{n} = a_{0}\pi_{n} + p_{0+1}\pi_{n-1} + \dots + p_{0+n-1}\pi_{1}$$

$$+ p_{0+n}\pi_{0}, \text{ for } n \leq N - c$$

$$p_{n} = a_{0}\pi_{n} + p_{0+1}\pi_{n-1} + \dots$$

$$p_{n} = a_{0}\pi_{n} + p_{0+1}\pi_{n-1} + \dots$$

$$p_{n-1}\pi_{n+1-(N-0)} + p_{N}\pi_{n-(N-0)}$$

$$for N - 1 \geq n > N - c$$

$$\sum_{i=0}^{N} p_{i} = 1$$

Due to limited buffer size,

Where

$\pi_n$  = probability of n characters originating from a renewal counting process during a service interval

$P_{i>N}$

N =buffer length in characters

$\mathbf{c} =$  number of transmission lines

The first equation describes the case in which the

buffer is vacant, if no more than c characters are in transmission at the beginning of the interval, and no arrivals occur during the interval. The second equation describes the case in which one character is in the buffer if no more than c characters are in transmission at the beginning and one arrives during the service time interval; or there are c + 1 in the buffer at the beginning and no character arrives during the service interval, etc. In the numerical computation carried out in this paper, we assume the character arrivals are generated from a Poisson process; that is,  $\pi_n =$  $\exp(-\lambda_u)\lambda_u^n/n!$ , where  $\lambda_u$  is the average character arrival rate to the user-to-computer buffer (offered load) from the m independent users. Since the buffer has a finite size of N,  $p_{i>N} = 0$ . Thus, when a character arrives and finds the buffer is full, an overflow will result. Therefore, the average character departure rate from the user-to-computer buffer (carried load),  $\alpha_u$  is less than the offered load from the users  $\lambda_u$ . The carried load can be computed from the buffer busy period

$$\alpha_u = \sum_{i=0}^{c-1} \mathbf{i} \cdot \mathbf{p}_i + \mathbf{c} \sum_{i=c}^{N} \mathbf{p}_i \qquad (4)$$

The overflow probability of the user-to-computer buffer, the expected fraction of total number of characters rejected by the buffer, is then equal to

$$P_{of} = \frac{\text{offered load} - \text{carried load}}{\text{offered load}} = 1 - \alpha_u / \lambda_u \quad (5)$$

The traffic intensity from user-to-computer,  $\rho_u$ , measures the degree of congestion and indicates the impact of a traffic stream upon the service streams. It is defined as

$$\rho_u = \lambda_u / c \mu \qquad (6)$$

Channel (server) utilization,  $\eta$ , measures the fraction of time that the lines are busy. It can be expressed as

$$\eta = (1 - P_{of})\lambda_u/c\mu = \alpha_u/c\mu \le \rho_u \qquad (7)$$

Since physically it is impossible for the transmission lines to be more than 100 percent busy, the utilization is limited to a numerical value less than unity. In the no-loss case (unlimited buffer size),  $P_{of} = 0$ , then  $\eta \equiv \rho$ .

The time average queuing length in the user-tocomputer buffer, L<sub>u</sub>, is equal to

$$\mathbf{L}_{s} = \sum_{i=0}^{N} (\mathbf{i} - \mathbf{o})\mathbf{p}_{i} + \lambda_{s}/2 \text{ characters}$$

for N > c. (8)

The first term in Equation (8) is the expected number of characters in the system at the beginning of a service interval. Since the characters could not leave the system during the service interval, we add the time average number of character arrival (for Poisson arrivals) during the service interval which is  $\lambda_u/2$ . The expected (time average) queuing delay of each character at the user-to-computer buffer due to buffering,  $D_u$ , can be evaluated by using Little's<sup>5</sup> result. We have

$$D_{\mu} = L_{\mu}/(\lambda_{\mu}(1 - P_{of}))$$

service times (9)

For the single server case, that is, c = 1, the set of state equations (2) becomes an imbedded Markov Chain, and can be solved iteratively to obtain the state probabilities as shown in References 3 and 4. For the multiple server case, however, the multiple dependence on the various states prevents us from using the iterative techniques for solution. Thus, the set of state probabilities, p.'s, must be solved from the set of linear matrix equations (2). The overflow probability, queuing delay, and queue length are then computed from the p.'s via Equations 4, 5, 8 and 9.

The size of the matrix (Equation 2) corresponds to the buffer length. The matrix equation was solved by the Gauss elimination method.<sup>6</sup> For purposes of accuracy, double precision was used in all phases of the computation. From the character arrival rate,  $\lambda_{u}$ , the coefficient values can be computed from (2) and they are stored in the computer program. Due to the limitation of the computer word size, double precision on IBM 360/65 provides 15-digit accuracy. Therefore, when the coefficient value is less than 10<sup>-15</sup>, it is set equal to zero. The computation time required to solve this type of system equation is largely dependent on its size. For a 10×10 matrix the computation time is about 0.8 seconds, while a 50×50 matrix equation takes about 1.67 minutes.

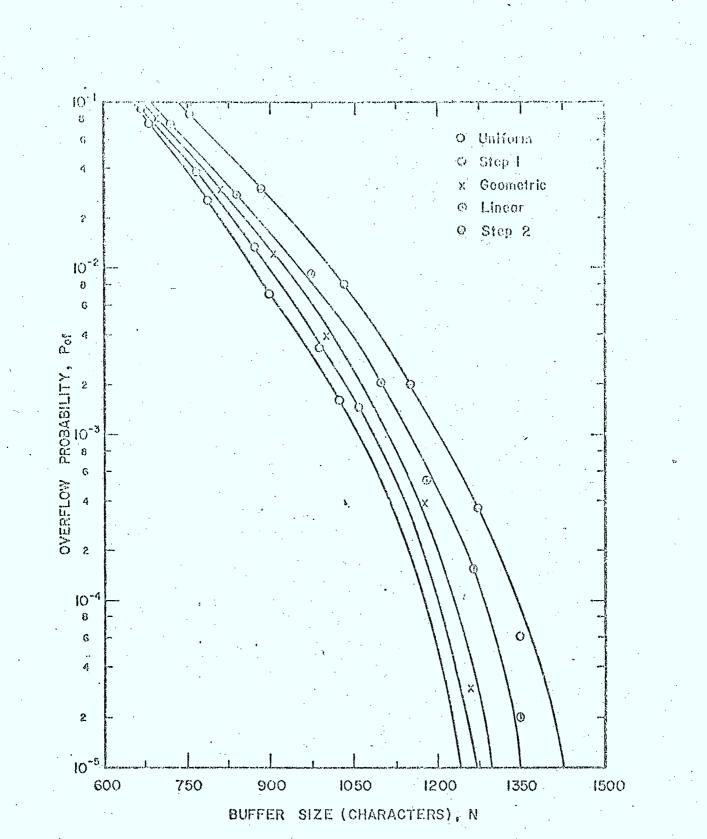

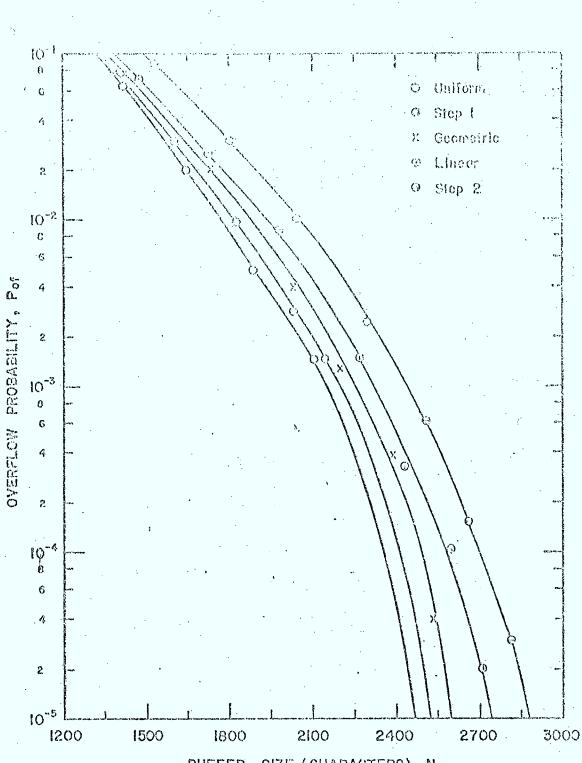

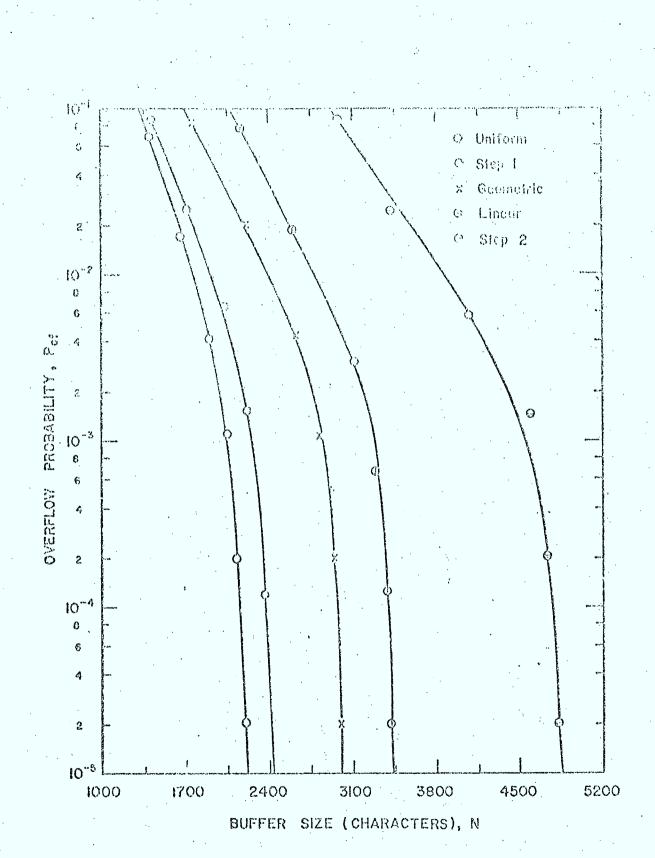

Numerical results are presented in Figures 4, 5 and 6. These results reveal the relationships among the overflow probabilities, number of transmission lines used, traffic intensities, and buffer sizes.

#### Computer-to-user buffer

In a previous section, the buffer behavior has been analyzed for a finite queue with multiple server, Poisson arrivals, and constant service time, which corresponds to the users-to-computer traffic. The

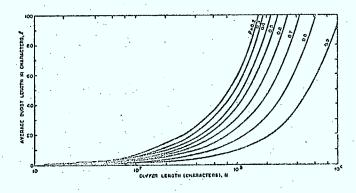

Figure 6-Expected queuing delay vs traffic intensity

computer-to-user traffic, however, is quite different from the users-to-computer traffic. The central processor of a time-sharing computer sequentially performs fractions of each user's job and the output traffic to the users are strings of characters which we shall call bursts. The length of the bursts are different from one to another and are treated as random variables. It is assumed that the internal processing speed of the computer is very fast as compared to the line transmission speed. Further, it is assumed that the various processing tasks generated by the user-computer interactions are independent from one user to another and have exponential interarrival times for a given user. In ATDM operation with these assumptions, the arrivals of bursts at the common output transmission buffer for the group of users are approximated as random. In this section, we shall analyze this buffer behavior under the assumptions of a finite queue, single server with batch (burst) arrivals, and constant scrvice time.

Using the burst length and traffic intensity as parameters, we would like to find the relationships among the overflow probabilities, expected burst delays due to buffering, and buffer sizes.

Let us consider the case that the burst length, Lis geometrically distributed with mean,  $\bar{\ell} = 1/\theta$ ; and the number of bursts arrived during a unit service interval (time to transmit a character from the multiplexed line), N, is Poisson distributed with mean,  $\lambda_{c}$ bursts/service time. The distributions of L and N are as follows:

$$f_{L}(\ell) = \theta(1-\theta)\ell^{-1} \qquad \ell = 1, 2, \cdots \qquad (10)$$

$$f_N(n) = \exp(-\lambda_c)\lambda_c^n/n!$$

$n = 0, 1, 2, \cdots$  (11)

The total number of characters that arrived during the time to transmit a character on the multiplexed line is a random sum,  $S_N$ , and is equal to

$$S_N = \sum_{i=0}^N L_i \qquad (12)$$

where  $L_i$ , a random variable distributed as (10), is the number of characters contained in the ith arriving burst. N, a random variable distributed as (11), is the total number of bursts arriving during the unit service interval. For simplicity in notation, we let  $S = S_{N^2}$

The characteristic function of S,  $\phi_s(u)$ , can be expressed in terms of the characteristic function of  $L_1$ ,  $\phi_\ell(u)$ , and  $\lambda_c$ .

$$\phi_{B}(\mathbf{u}) = \exp[-\lambda_{c} + \lambda_{c}\phi_{L}(\mathbf{u})] \qquad (13)$$

Since the burst lengths are geometrically distributed the characteristic function of L is

$$\phi_L(\mathbf{u}) = \theta \cdot \exp(i\mathbf{u}) / \left(1 - (1 - \theta) \exp(i\mathbf{u})\right)$$

(14)

where  $i = \sqrt{-1}$ . Substituting (14) into (13), then

$$\phi_{\theta}(\mathbf{u}) = \exp[-\lambda_{e} + \lambda_{e} \cdot \theta \cdot \exp(i\mathbf{u})/(1 - (1 - \theta)\exp(i\mathbf{u}))]$$

(15)

From (15), it can be shown that the probability density of j characters arriving during a unit service interval,  $f(S = j) = f_{j}$ , is a compound Poisson distribution as shown in (16)

$$f_{j} = f(S = j) = \begin{cases} \sum_{k=1}^{j} {j-1 \choose k-1} (\lambda_{c}\theta)^{k} \\ (1-\theta)^{j-k} \exp(-\lambda_{c})/k! \\ j = 1, 2, \cdots \\ \exp(-\lambda_{c}) \qquad j = 0 \end{cases}$$

(16)

The expected value of S is given by E[S] = E[L]E[N]=  $\lambda/\theta$ , and the variance of S is given by

$$Var[S] = \lambda (2 - \theta) / \theta^2$$

(17)

674 Fall Joint omputer Conference, 1969

The time required to compute the probability density function of S,  $f_{j}$ , from (16) is dependent on the size of j. For large j (e.g., j > 1000), the computation time could be very large and prohibitive. A convenient and less time consuming way to compute  $f_j$  is from  $\phi_B(u)$  by using the Fast Fourier Transform' inversion method as follows:

$$f_{j} = \sum_{r=1}^{M} \phi_{S}(r) \exp[-2\pi i r j/M]$$

$j = 0, 1, 2, \dots, M - 1$  (18)

where

$$r = 2\pi u/M$$

M = total number of input points to represent  $\phi_S(r) = total$  number of output values of  $f_j$ .

In order to accurately determine  $\phi_s(\mathbf{r})$ , it is computed with double precision on the IBM 360/65. Further, we would like to use as many points as possible to represent  $\phi_s(\mathbf{r})$ ; that is, we would like to make M as large as possible. Because of the word length limitation of the computer, double precision provides 15-digit accuracy. Therefore, when  $f_j < 10^{-15}$ , it is set equal to zero. M is selected such that  $f_{j\geq M} < 10^{-15}$ . The M's are different for different values of  $\lambda_c$  and  $\vec{\ell}$ .

The following is the set of state equations for a buffer size of N characters with batch renewal arrivals, single server, and constant output rate.

$$p_n = \pi_0 p_{n+1} + \sum_{i=1}^n \pi_{n-i+1} p_i + \pi_n p_0$$

$p_{n+1} = \frac{1}{\pi_0} \left[ p_n - \sum_{i=1}^n \pi_{n-i+1} p_i - \pi_n p_0 \right]$ (19)  $n = 0, 1, 2, \dots, N - 1$

$$\sum_{i=0}^{H} \mathbf{p}_{i} = 1$$

(20)

$$\mathbf{p}_{i>N} = \mathbf{0} \tag{21}$$

The above equations are reduced from Equation (2) by letting c=1.

The average character departure rate from the buffer (carried load),  $\alpha_c$ , is less than the average character arrival rate to the buffer (offered load),  $\beta = \lambda_c/\theta$ , from the computer. The carried load can be computed from the probability that the buffer is idle,

$$u_o = 1 - p_0$$

(22)

The overflow probability of the buffer with burst input, the expected fraction of total number of characters rejected by the buffer, is equal to

a

$$P'_{of} = \frac{\text{offered load-carried load}}{\text{offered load}} = 1 - \alpha_o / \beta \quad (23)$$

The traffic intensity from computer-to-user is

$$\rho_c = \beta/\mu = \lambda_c/(\theta\mu) = \lambda_c \overline{\ell}/\mu \qquad (24)$$

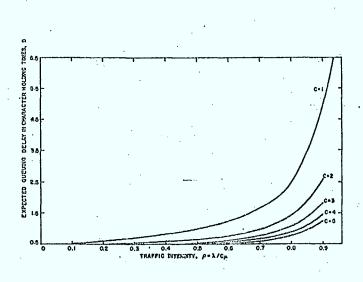

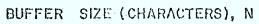

The set of state Equations (19) is an imbedded Markov Chain. In the following numerical computations, we shall assume that the character arrivals are generated from a compound Poisson process, i.e.,  $\pi_i = f_i$ . The state probabilities can be solved iteratively and expressed in terms of  $p_o$ . From (20), we can find the value of  $p_o$ . Thus we find all the state probabilities. The overflow probabilities for various burst lengths can then be computed from (23). These results are presented in Figure 7 which provides the relationships (at  $P'_{of} = 10^{-6}$ ) between burst lengths and buffer sizes for selected traffic intensities.

In the above analysis, we have treated each character as a unit. However, in computing the expected burst delay,  $D_e$ , due to buffering, we should treat each burst as a unit. The service time is now the time required to transmit the entire burst. For a line with

Figure 7—Buffer length vs average burst length,  $P'_{of} = 10^{-3}$

and

or

constant transmission rate, the service time distribution is the same as the burst length distribution except by a constant transmission rate factor. When overflow probability is very small, for example,  $P'_{of} = 10^{-6}$ , then  $D_e$  can be approximated by the expected burst delay of the infinite waiting room with Poisson Arrivals and single server with geometric service time, M/G/1, model.<sup>8,9</sup> Hence

$$D_{c} = \frac{\lambda E(L^{2})}{2(1-\rho)} = \frac{\lambda_{c}(2-\theta)}{2(\theta-\lambda_{c})}$$

character-holding times (25)

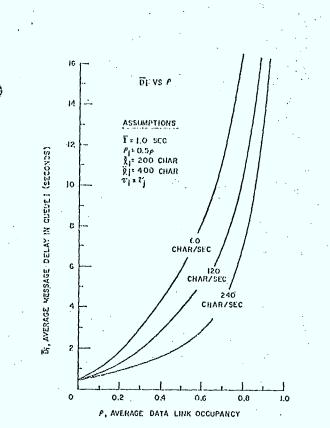

where  $E(L^2)$  = second moment of burst length, L. The delays are computed from (25) for selected traffic intensities and burst lengths. Their results are portrayed in Figure 8.

Figure 8—Traffic intensity vs expected burst queuing delay

#### Discussion of results

We shall first discuss the user-to-computer buffer behavior. Figure 4 portrays the relationships between overflow probabilities and buffer size for selected traffic intensities and selected numbers of servers. The curves for two-, three-, and four-servers lie in the region between the single and the five-server curves. For a given traffic intensity, the overflow probability decreases exponentially with buffer size. For a typical traffic intensity of 0.8, a buffer of twenty-eight character length will achieve an overflow probability in the order of 10<sup>-6</sup>. A larger buffer size is needed for  $\rho_u > 0.8$ in order to achieve the same degree of buffer performance. For a given  $\rho$ , the queuing delay increases as the overflow probability decreases (or the buffer size increases). When the overflow probability is less than  $10^{-4}$  (for  $\rho_u = 0.8$ , this overflow probability corresponds to a buffer size of about eighteen characters), the delay increment with buffer length becomes negligible and the delay can be approximated as independent of buffer size as shown in Figure 5.

For the data transmissions in time-sharing systems, the buffer overflow probability should be somewhat less than the line error rate. For currently available lines, the error rate is about  $10^{-5}$ . Therefore from Figure 5, we know that the queuing delay range of interest is almost independent of the buffer length. Figure 6 describes the queuing delays (at overflow probability =  $10^{-5}$ ) for various traffic intensities. The queuing delay increases exponentially with  $\rho$ : For a given  $\rho$ , the queuing delay decreases with the increase of number of servers. Figures 4 and 6 agree with our intuition that whenever multiple servers are needed, it is always advantageous to use a common buffer rather than using several single lines with separate buffers.

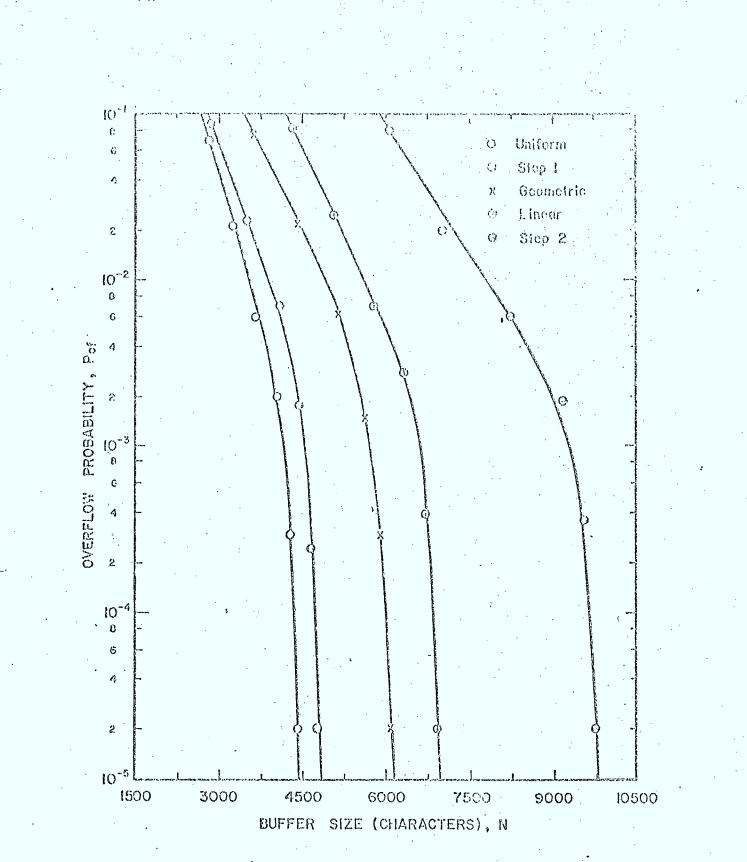

Next we shall discuss the computer-to-user buffer behavior. The overflow probability depends upon the buffer size, the traffic intensity, and expected burst length. For a given average buffer length, the overflow probability increases as the traffic intensity increases. For a given traffic intensity, and a desired buffer overflow probability, the required buffer size increases as the average burst length increases. Figure 7 provides the relationships between the average burst length and required buffer size to achieve an overflow probability of  $10^{-6}$  for selected traffic intensities.

When the average burst length equals unity, then the result reduces to the case of Poisson arrivals, single server and constant service time as had been analyzed.<sup>3,4</sup> For a given traffic intensity, required buffer size for average burst lengths  $\tilde{\ell}(\tilde{\ell} > 1)$ , N<sub>\ell</sub>, to

#### 676 Fall Joint Computer Conference, 1969

achieve the same degree of overflow probability is much greater than that for unity burst length, N1. In general,  $N_{\ell} > \tilde{\ell} \times N_1$ . As  $\tilde{\ell}$  increases, the difference between  $N_{\ell}$  and  $\ell \times N_1$  increases. For example, for  $\rho_c$ = .8,  $\overline{\ell} = 1$ , the required buffer size to achieve P'of = 10<sup>-6</sup> is  $N_1 = 28$  characters. When  $\ell = 4$ , then from Figure 7,  $N_4 = 212 > 4 \times 28 = 112$  characters. In the same manner, if  $\ell = 20$ ,  $N_{20} = 1200 > 20 \times 28$ = 580 characters. This is due to the fact that the variance of S is proportional to  $\overline{\ell}$  as shown in (17). Figure 8 portrays the relationship between expected burst queuing delay and traffic intensity for selected expected burst lengths. For a given expected burst length, the expected queuing delay increases as traffic intensity increases; for a given traffic intensity, the expected queuing delay increases with burst length. These are important factors that affect the delay.

#### Optimal design of multiplexing system

Let us first consider the design of the user-tocomputer multiplexer. Based on the user-to-computer traffic characteristics, the number of user terminals, maximum allowable queuing delay, and overflow probability, several different buffer system configurations might satisfy the desired requirements. Hence there are trade-offs among the number of transmission lines we might use, the transmission rates of the lines, and the buffer sizes. We would like to design the multiplexing system whose total cost (transmission cost and buffer storage cost) is minimum. One way to proceed with this is first to select the set of possible multiplexing system configurations based on the queuing delay requirements from Figure 6. Based on the maximum allowable overflow probability; we can obtain the, required buffer length for this set of possible multiplexing system configurations. The optimal user-tocomputer part of the multiplexing system can then be selected as that which minimizes the cost of the system.

Next, we shall consider the optimizations of the computer-to-user multiplexer. Data collected from several operating time-sharing systems<sup>10</sup> revealed that the average number of characters sent by the computer to the group of users is an order of magnitude greater than the number of characters sent by the group of users to the computer. Thus, using high transmission rate line for computer output data would significar thy reduce in buffer size and the queuing delay due to buffering. Further, the change in the computer system such as changes in the scheduling algorithm<sup>11-17</sup> in the contral processor can strongly influence the computer output traffic statistics, which will directly affect the buffer performance, and the design of the docoding system.

In practice, we would like to design a system that has minimum total cost yet satisfies all the requirements such as the inquiry-response delay, average holding time of each user, etc. Since the multiplexing system and the central processor intimately interact with each other, the multiplexing system should be treated as a subsystem of the time-shared computer system. The economical and performance optimization should be carried out jointly between the central processor and available communication facilities.

#### Example

Consider the design of a time-sharing system that consists of many remote terminals and that employs the ATDM technique with full duplex operation between the terminals and the central processor. Measurements of the traffic characteristics from several operating systems have revealed that the character interarrival time per user line can be approximated as exponentially distributed with mean about 0.5 seconds.<sup>10</sup> Thus, the character arrivals can be treated as Poisson arrivals with a rate of 2 char/sec. A reasonable conservative guess is that 50 percent of the transmitted information is sufficient for addressing and framing. Voice-grade private lines can easily transmit 240 char/ sec from users. Suppose this operating system consists of m = 48 terminals, all the terminals are assumed to be independent and have the same traffic characteristics. The buffer is designed such that the overflow probability is less than about 10-3. We shall use our model to determine the buffer size and the average queuing delay incurred by each character.

The traffic intensity is  $\rho_u = 1.5 \times m \lambda_u / c \mu_u = 1.5 \times$  $48 \times 2/240 = 0.6$ . To achieve the desired overflow probability, from Figure 4, the required buffer length is 14 characters. From Figure 6, the normalized queuing delay due to buffering is equal to 1.25 holding times. Since each holding time is equal to  $1/\mu_u = 1/240 = 4.16$ millisecond, the waiting time of each character is 5.06 milliseconds. Now suppose the number of terminals is increased from 48 to 96. In order that traffic intensity be less than unity, two transmission lines are required and the traffic intensity is still equal to 0.6. From Figure 5, the buffer length corresponding to the desired overflow probability for two transmission lines is about 14 characters. The waiting time is about 0.3 holding times which is equal to 3.33 milliseconds. Although the difference between 5.06 milliseconds and 3.33 milliseconds may not be detected by a user at a

terminal, a common buffer of the same size operating with two output lines can handle twice the number of input lines as with one output line. Thus, the common buffer approach permits handling a wide range of traffic without substantial variation in buffer size.

Next, we shall consider the buffer design problem that employs the ATDM technique to transmit data from central processor to remote terminals. The traffic statistics as well as the message length are different from that of the users. The burst interarrival time<sup>10</sup> can be approximated as exponentially distributed with a mean of 2.84 seconds. Thus, the bursts can be approximated as Poisson arrivals with a rate of  $\lambda_{\sigma} =$ 0.35 bursts/sec. Further, data collected in the same study indicate that the burst length can be approximated as geometrically distributed with a mean of  $\ell$ = 20 characters. Suppose we use a wideband transmission line that transmits 480 char/sec to provide communications from the central processor to 48 terminals. Assuming 20 percent of the transmitted information is used for addressing and framing, then the traffic intensity,  $\rho_o = 1.2\lambda_o l, \mu_o \approx 0.84$ . To achieve an overflow probability of 10-6, from Figure 7, we find that the required buffer size is 1,400 characters. From Figure 8, the expected queuing delay for each burst is 85 character-holding times, or 85/480 = 0.176 . seconds.

Suppose now we changed our transmission rate from 480 to 960 char/sec; then the traffic intensity  $\rho_c \approx 0.42$ . The corresponding required buffer size in order to achieve an overflow probability of 10<sup>-6</sup> is 480 characters, and the delay is 15 character-holding times or 16 milliseconds. Thus, these results also provide insight regarding the trade-off between transmission costs and storage costs.

The above example is based on the output traffic characteristics of a specific computer scheduling algorithm. As the output traffic statistics changes with different scheduling algorithms, the buffer performance in the multiplexing system is affected. To design an optimal system, we should jointly optimize the scheduling algorithm and the multiplexing system such that yield minimum total cost and also meet the required system performance such as maximum allowable inquiry-response delay, desired overflow probability, etc.

#### CONCLUSIONS

Queuing analyses indicate that for an allowable overflow probability and queuing delay, moderate buffer sizes can be achieved for asynchronous time division multiplexing for time-sharing computer systems. Further, when multiple transmission lines are required, better buffer performance will be achieved by using a common buffer rather than by using separate ones.

Because of the asymmetric nature of the traffic characteristics of user-to-computer transmission versus computer-to-user transmission, a much larger buffer is required for the computer-to-user multiplexer to handle the larger volume of data generated by the central processor.

The multiplexing system and the central processor in a time-shared environment directly interact with each other. To design an optimal operating system, we should jointly optimize the central processor and the multiplexing system (for example, the interaction between scheduling algorithm and buffer performance) to obtain a minimum cost system that meets the system performance requirements. It is apparent that closer coordination between the computer and communication system designs would be fruitful in terms of economics and technological improvements to the overall system design.

#### ACKNOWLEDGMENTS

The author wishes to thank E. Fuchs and D. Heyman of Bell Telephone Laboratories for their helpful discussions.

#### REFERENCES

- 1 K BULLINGTON J M FRASER

- Engineering aspects of TASI

- B S T J March 1959 353-364

- 2 B A POWELL B AVI-ITZHAK Queuing system with enforced idle time

- Operations Research Vol 15 No 6 Nov 1967 1145-1156 3 T G BIRDSALL et al

- Analysis of asynchronous time multiplexing of speech sources IRE Trans on Communications Systems Dec 1962 390-397

- 4 N M DOR Guide to the length of buffer storage required for random (Poisson) input and constant output rates IEEE Trans on E C Oct 1967 683-684

- 5 J D C LITTLE A proof of the queuing formula  $L = \lambda W$ Operations Research Vol 9 1961 383-387

- 6 R W HAMMING Numerical methods for scientists and engineers McGraw-Hill Book Co Inc N Y 1962 363-364

7 W M GENTLEMAN G SANDE Fast fourier transforms—for fun and profit

- Proc FJCC Vol 29 563-578 8 N U PRABHU

- Queues and inventories John Wiley and Sons Inc N Y 1965 42

- 9 P M MORSE Queues Inventories and Maintenance

678 Fall Joint Computer Conference, 1969

John Wiley and Sone Inc 1958 15-18 10 P E JACKSON C D STUBBS A study of multiaccess computer communications Proc SJCC Vol 34 1989 491-504 11 A L SCHERR An analysis of Time-Shared Computer Systems

- MIT Research Monograph No 30 MIT Press Cambridge Mess 1967

- 12 P E DENNING Effect of echeduling on file memory operations Proc SJCC Vol 30 1967 9-21

13 J E SHEMER Some mathematical considerations of time-sharing scheduling algorithms

J AOM Vol 14 No 2 April 1937 262-372

14 E G COFFMAN JR

- Analysis of two time-sharing algorithms designed for limiting swapping

- JACM July 1968

15 É G COFFMAN L KLEINROCK Feedback queuing models for time-shared system J ACM Vol 15 No 4 Oct 1968 549-576

16 L KLEINROCK Certain analytic results for time-shared processors Proc IFIP Congress 1968 Edinburgh Scotland Aug 5-10 1968 D119-D125

17 W W CHU

Optimal file allocation in a multicomputer information system Proc IFIP Congress 1968 Edinburgh Scotland Aug 5-10 F80-85

- CARLA STREET COMMENT Problems in the Optimization of Data Communications Systems October 13-16, 1969 Pine Mountain, Georgia \$ 35-60 Cha, Wenny W.

# Design Considerations of Statistical Multiplexors

# Wesley W. Chu

Computer Science Department University of California Los Angeles, California

# ABSTRACT

Design considerations for statistical multiplexors with Poisson message arrivals and the following three types of messages are considered: 1) constant length messages, 2) random length messages, and 3) segmented random length messages with fixed-size blocks. The operating costs of the multiplexors can be divided into transmission costs and storage costs. The transmission costs are dependent on the transmission rates of the lines and the number of lines used. The storage costs are dependent on the buffer length required, the cost of overhead in buffer management, and the cost of waste spaces of fixed-size block messages. The queuing delays imposed by multiplexors are dependent, for example, on delays due to buffering and computer scheduling algorithms. The trade-offs among transmission costs, storage costs, and delays are described. An optimal multiplexor is the one that yields minimum operating costs yet satisfies the required performances (e.g., delays, overflow probabilities). Some design considerations of multiplexing systems are then illustrated via examples.

This work was done while the author was with Bell Telephone Laboratories, Holmdel, New Jersey.

### INTRODUCTION

In order to reduce the communciations costs in timesharing systems and multiple computer communications systems, multiplexing techniques have been introduced to increase channel utilization. A commonly used technique is synchronous time division multiplexing (STDM). In synchronous time division multiplexing, each terminal is assigned a fixed time duration-for the transmission of messages from the terminal to the computer. After one user's time duration has elapsed, the channel is switched to another user. With appropriately designed synchronous operation, required buffering is limited to one character for each transmission line, and addressing is usually not required. The STDM technique, however, often has certain disadvantages. As shown in Figure 1, it is inefficient in channel capacity, and so transmission cost, to permanently assign a segment of bandwidth that is utilized only a portion of the time. Data collected from several representative operating time-sharing systems [1] revealed that during an average call, 95 percent of the user-to-computer channel and 65 percent of computer-to-user channel are idle. These idle periods could be made available for additional A more flexible system that efficiently uses the transusers. mission facility is to statistically multiplex the data. With such an arrangement, each user will be granted access to the channel only when he has a message to transmit. This is

known as asynchronous time division multiplexing system (ATDM) [2]. The crucial attributes of such a statistical multiplexing technique are: 1) an address is required for each transmitted message, and 2) buffering is required to handle statistical peaks in random message arrivals.

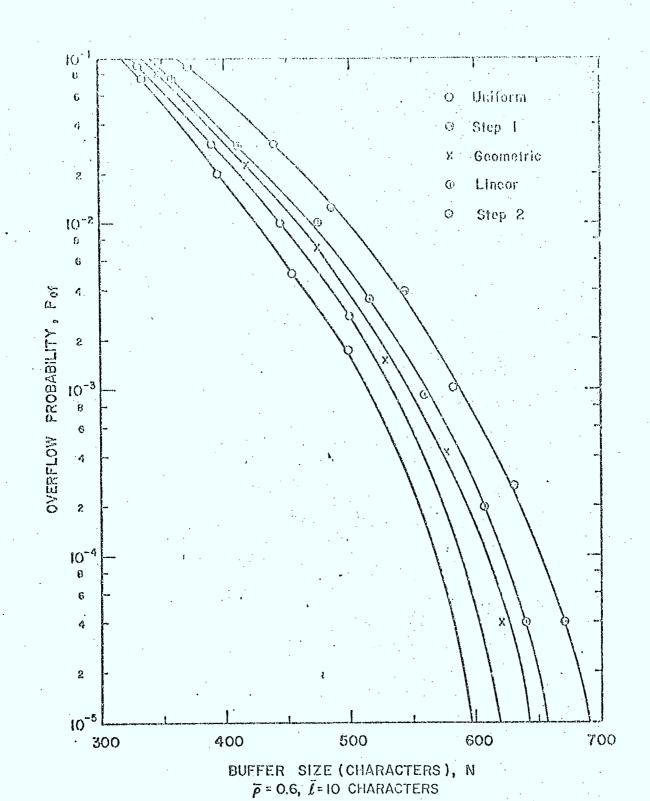

If the buffer is empty during a transmission interval, the channel will be idle for this interval. Queuing analyses indicate that an allowable overflow probability and queuing delay can be achieved by a moderate size buffer [2]. Design trade-offs among such parameters as transmission rates, number of lines used, buffer lengths, queuing delay, and computer scheduling algorithms are discussed in the following sections. ANALYSIS OF STATISTICAL MULTIPLEXORS

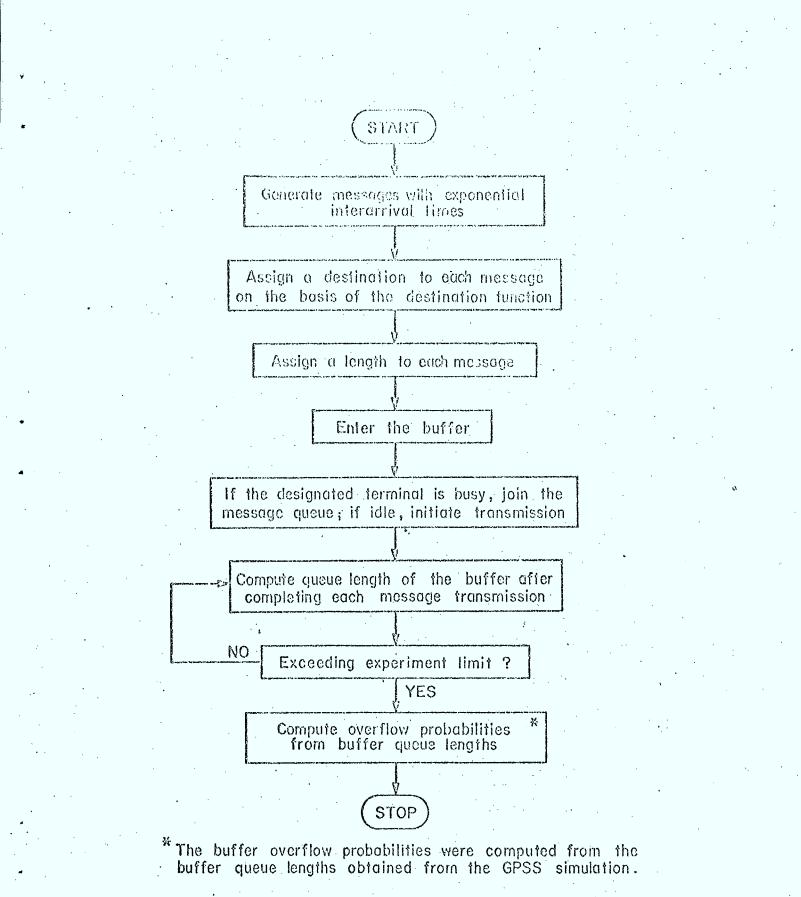

A statistical multiplexor consists of a buffer, coding/decoding circuit, and a switching circuit (in the case of multiple lines). The buffer behavior can be analyzed by queuing models with finite waiting lines. Data measured from several operating time-sharing systems shows that the message arrivals can be approximated as a Poisson process [3]. The three types of messages (Figure 2) considered are: 1) constant length messages, 2) random length messages, and 3) segmented random length messages with fixed-sized blocks.

There may be other reasons for providing buffering such as: tolerating momentary loss of signals (e.g., fading), momentary interruptions of data flow, permitting error control on the line, etc. Under these conditions, the buffer should be designed to satisfy also the above specific requirements. The parameters of interest in describing the buffer behavior are: the buffer behavior overflow probabilities,  $P_{of}$ , which is the average fraction of the total number of characters that overflow from the buffer; traffic intensity,  $\rho$ , which gives a measure of the degree of congestion of the multiplexed channel(s); expected queuing delay, D; buffer size, N; and average burst (a string of characters) length,  $\overline{k}$ .

For reliability and simplicity in data transmission, synchronous transmission is assumed. The data are taken out synchronously from the buffer for transmission at each discrete clock time. When the buffer and server are empty (transmission facility is idle) at the beginning of a clock time, data arriving at the buffer during the period between clock times have to wait to begin transmission at the beginning of the next clock time. In queuing theory terminology, the above system implies there is a gate between the server and waiting room which is open at fixed intervals.

The constant length message model corresponds to the user-to-computer traffic where users type characters one at a time at the terminals. The service time,  $1/\mu$ , corresponds to the time to transmit a constant length character. The relationships among the overflow probabilities, number of transmission lines used, traffic intensities, and buffer sizes are portrayed in Figures 3 and 4 [2]. We noted that when multiple transmission lines are required, better buffer performance will be achieved by using a common buffer rather than by using separate ones.

The random length messages correspond to the computer-to-user traffic. The central processor of a timesharing computer sequentially performs fractions of each user's job and the output traffic to the users is strings of characters which we shall call bursts. The lengths of the bursts can be approximated as geometrically distributed [3]. Again, the service time is the time to transmit a constant length character. The number of characters arriving at the buffer during a unit service time is compound Poisson distributed [2]. The buffer behavior can be analyzed by a finite waiting room queuing model with Poisson batch arrivals and constant service The relationships, at  $P_{of} = 10^{-6}$ , between the time [2]. average burst lengths and buffer sizes for selected traffic, intensities are portrayed in Figure 5.

When the average burst length equals unity, then the result reduces to the case of Poisson arrivals, single server and constant service time as previously have been analyzed [4,5]. For a given traffic intensity, the required buffer size, N<sub>g</sub>, for average burst lengths  $\overline{k}$  ( $\overline{k} > 1$ ), to achieve the same degree of overflow probability is much greater than that of unity burst length, N<sub>1</sub>. In general, N<sub>g</sub> >  $\overline{k} \times N_1$ . For example, for

$\rho = 0.8$ ,  $\overline{k} = 1$ , the required buffer size to achieve a  $P_{of} = 10^{-6}$ is  $N_1 = 28$  characters. When  $\overline{k} = 20$  characters, then from Figure 5,  $N_{20} = 1400 > 20 \times 28 = 580$  characters. Further, as  $\overline{k}$ increases, the difference between  $N_k$  and  $\overline{k} \times N_1$  increases. This is due to the fact that the variance of the total number of characters arriving at the buffer during a unit service time is proportional to  $\overline{k}$ . Figure 6 shows the relationships between expected queuing delay for each burst with various traffic intensities.

In the above, we have discussed the buffer behavior for random length message inputs. The random nature of the message length, however, greatly complicates the problem of storage allocation. A way to simplify this problem is to segment messages into fixed-sized blocks [6]. An address as well as linking information to subsequent blocks is assigned to each block as shown in Figure 2. Since each block has an address and is uniform in size, a block can be stored in any vacant position in the buffer. It is not necessary to rearrange the Buffer to obtain an adequate space for the entire Thus, the storage allocation problem is greatly simpliburst. fied. The wasted storage space created by segmentation is: 1) some number of address characters, b, to identify each block and to link the subsequent blocks, and 2) the unfilled space of the last block.

When the message length is geometrically distributed, the optimal segmented block size, B', that minimizes the waste

mace [6] is

$$B' = \sqrt{2b\overline{L}} - b/3 + \frac{31b^{3/2}}{9\sqrt{2\overline{L}}} + 0(1/\overline{L})$$

(1)

The actual block size B is equal to the sum of the segmented block size and the required address length; that is

$B = B' + b \tag{2}$

We shall now study the buffer behavior for the segmented fixed-size block inputs. It can be shown that when burst lengths are geometrically distributed with parameters p and q = 1 = p, and when the burst is segmented into fixed-sized blocks B', then the number of blocks per burst is also geometrically distributed with parameter  $Q = q^{B'}$  and P = 1 - Q. Each block consists of many characters. Although each character is synchronously transmitted, service for the block may be assumed to be asynchronous (i.e., if the channel is idle, the message arriving at the buffer is transmitted immediately) as a good approximation.<sup>\*</sup> For Poisson burst arrivals with geometrically distributed burst lengths, the number of segmented

When the block is very short then we should assume the block service is synchronous and the buffer behavior is the same as the random message case, except characters now should be viewed as blocks. blocks arriving during unit service interval (the time required to transmit a fixed-sized block of characters) is compound Poisson distributed. Using the finite waiting room queuing model with compound Poisson arrivals, and asynchronous constant service [7], the relationships among block overflow probabilities (the average fraction of the total number of blocks that overflow from the buffer), average number of blocks per burst,  $\overline{n}(\ell)$ , and buffer sizes are portrayed in Figure 7. The average delay of each block for selected traffic intensities is shown in Figure 8.

# DESIGN TRADE-OFFS