# RAF 2 AN ASSOCIATIVE PROCESSOR FOR DATA BASES

S.A. SCHUSTER H.B. NGUYEN E.A. OZKARAHAN K.C. SMITH

# FINAL REPORT TO DOC - CONTRACT 0SU5-0205

UNIVERSITY OF TORONTO JANUARY 1978

P 91 C655 R36 1978

Þ 91 C655 R36 1978 RAP 2: an association processory for data bases ! final report to DOC/ Industry Canada Library Queen MAR-8 1978 135 Industrie Canada Bibliothèque Queen COMMUNICATIONS CANADA **K198**3 SFP

LIBRARY - BIBLIOTHNUE

. . .

..

Pal 655 C655 R368 R378

Ċ,

#### TABLE OF CONTENTS

- O. OVERVIEW

- INTRODUCTION 1.

- 1.1 DATA BASE MANAGEMENT SYSTEM REQUIREMENTS

- 1.2 PROBLEMS WITH CONVENTIONAL IMPLEMENTATIONS

- 1.3 THE ASSOCIATIVE/ARRAY PROCESSOR APPROACH.

- 1.4 BASIC ARCHITECTURE OF RAP

- 2. THE ABSTRACT MACHINE

- 2.1 DATA STRUCTURE 2.2 INSTRUCTION FORMAT

- 2.3 DESCRIPTION OF RAP INSTRUCTIONS

- 2.3.1 SELECTION

- 2.3.2 RETRIEVAL 2.3.3 STATISTICAL COMPUTATIONS

- 2.3.4 UPDATE

- 2.3,5 INSERTION AND DELETION 2.3.6 DATA DEFINITION

- 2.3.7 REGISTER MANIPULATION

- 2.3.8 DECISION AND TRANSFER

- 2.4 SUMMARY OF PERFORMANCE

- 3. IMPLEMENTATION

- 3.1 HISTORY

- 3.2 PHYSICAL DATA ORGANIZATION

- 3.3 GLOBAL ARCHITECTURE AND COMMUNICATIONS

- 3.4 INSTRUCTION SET EXECUTION

- 3.5 CELL STRUCTURE

- 3.6 SOME STATISTICS

4. DBMS UTILIZATION OF RAP

- 4.1 SYSTEM ORGANIZATION

- 4.1.1 RAP AS AN ACCESS PATH PROCESSOR

- 4.1.2 DATA BASE PARTITIONING

- 4.1.3 PAGING AND VIRTUAL MEMORY

- 4.2 SUPPORTING MULTIPLE LOGICAL VIEWS

- 4.3 A NOTE ON PROTECTION, SECURITY AND INTEGRITY

- 5. RAP AND CONTIUNICATIONS

- 5.1 COMMUNICATIONS PROBLEMS

- 5.2 THE INHERENT CONFLICT BETWEEN DBMS AND

- 5.3 RAP AND COMMUNICATIONS

- 5.4 DATA BASE PROCESSORS AT THE NODES OF A COMMUNICATIONS NETWORK 5.4.1 A SOCIETAL PROBLEM

- 5.4.2 A TECHNICAL PROBLEM 5.4.3 A TOTAL SOLUTION

- 5.5 RAP IN A COMMUNICATIONS ENVIRONMENT

- 5.5.1 REMOTE DATA BASES 5.5.2 DISTRIBUTED DATA BASES

- 5.5.3 PRIVACY AND SECURITY

- 6. ACKNOWLEDGMENTS

- 7. REFERENCES

- DESIGN/PERFORMANCE APPENDICES

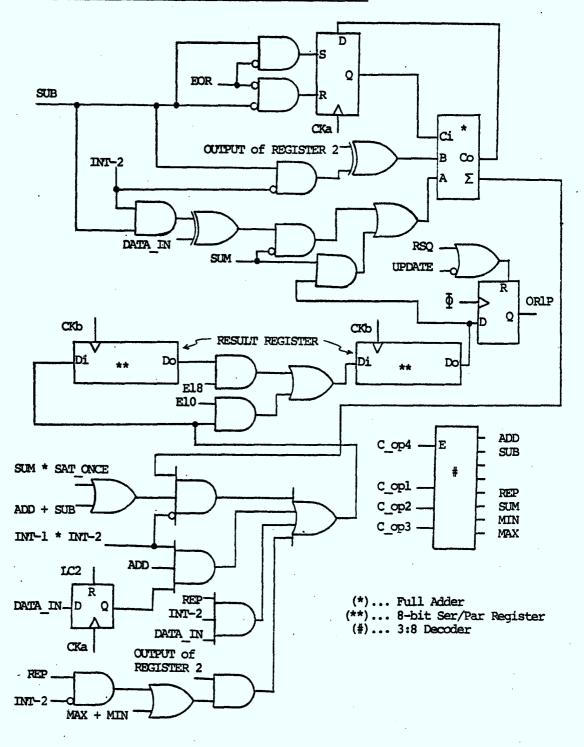

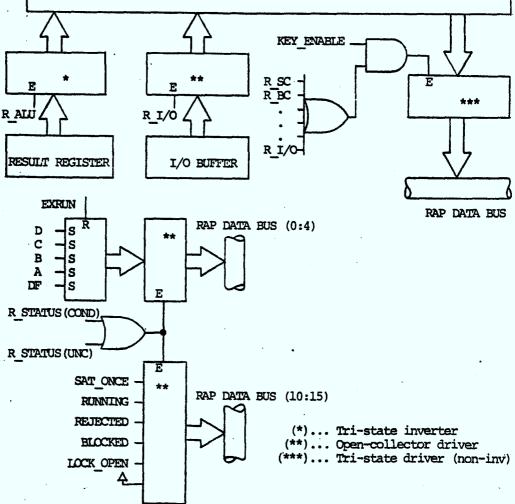

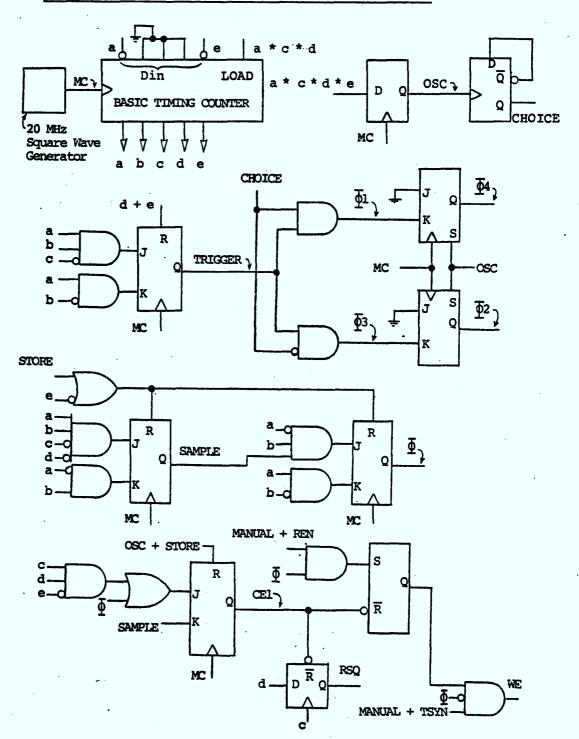

- 8.1 RAP 2 CELL LOGIC DESIGN

- 8.1.1 GENERAL

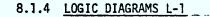

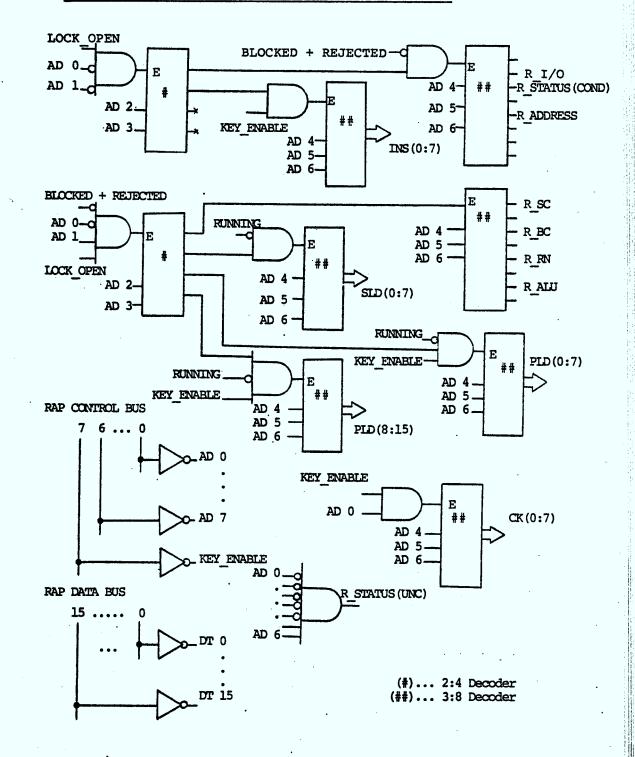

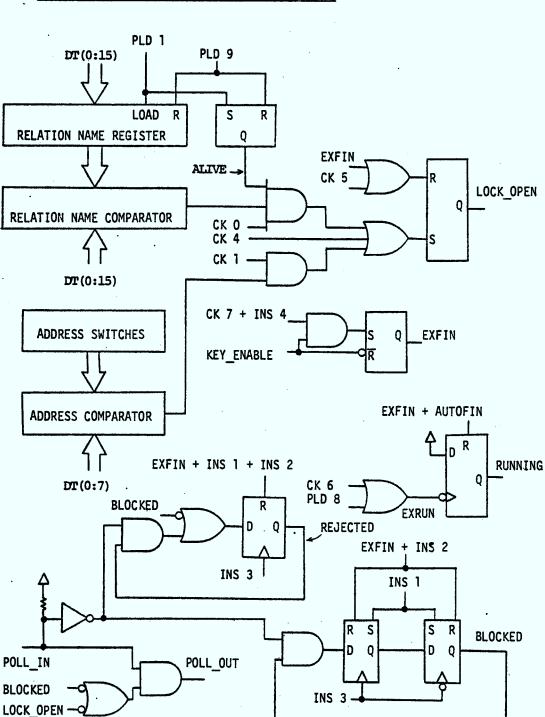

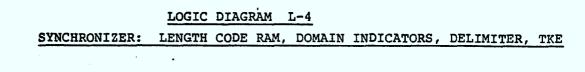

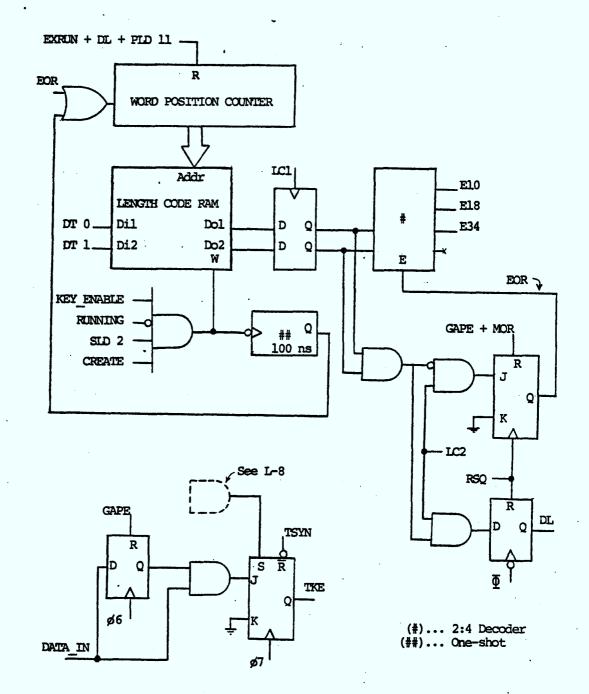

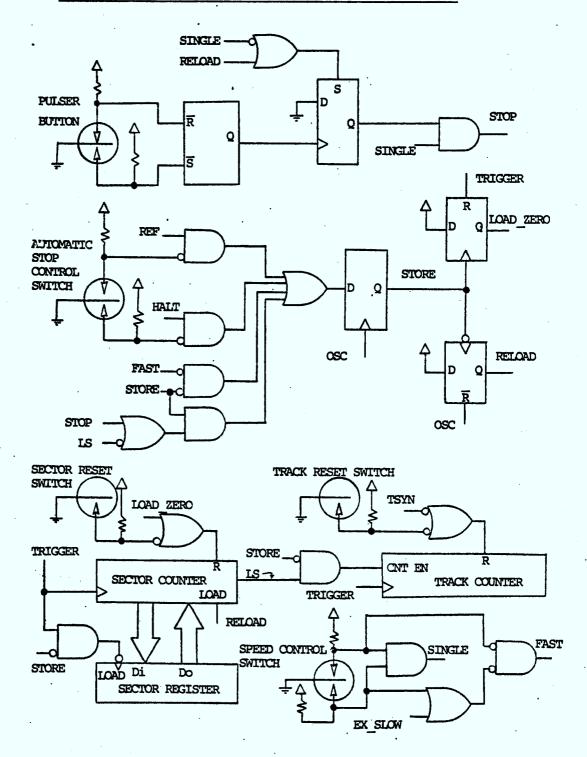

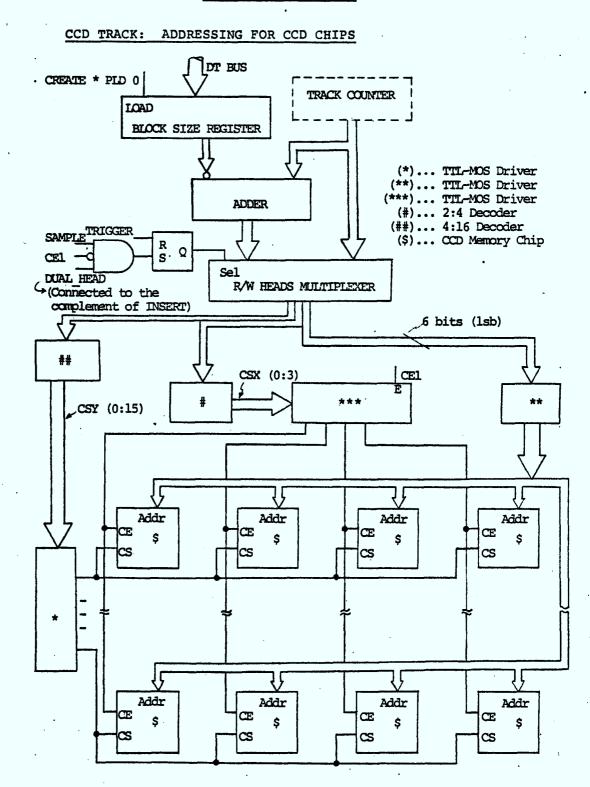

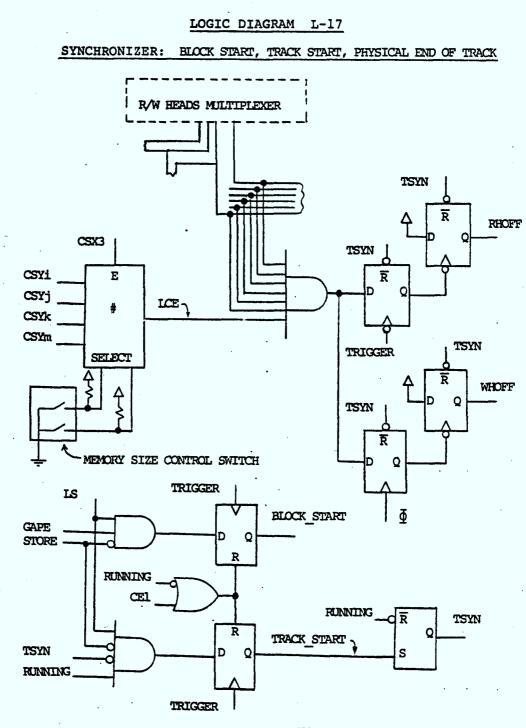

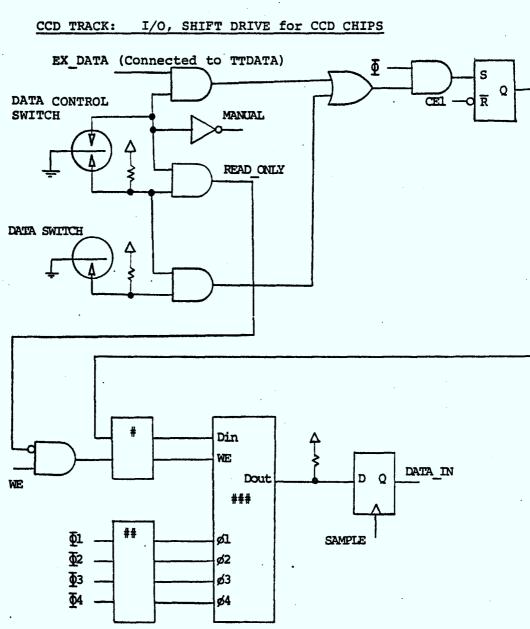

8.1.2 FUNCTIONAL DESCRIPTION 8.1.2.1 LOGIC DIAGRAM L-1 8.1.2.2 LOGIC DIAGRAM L-2 8.1.2.3 LOGIC DIAGRAM L-3 8.1.2.4 LOGIC DIAGRAM L-4 8.1.2.5 LOGIC DIAGRAM L-5 8.1.2.6 LOGIC DIAGRAM L-6

8.1.2.7

8.1.2.9 LOGIC DIAGRAM L-9 8.1.2.10 LOGIC DIAGRAM L-10

8.1:2.11 LOGIC DIAGRAM L-11 AND L-12

Sec. 4 Sec.

- 8.1.2.12 LOGIC DIAGRAM L-13

- 8.1.2.13 LOGIC DIAGRAM L-14 8.1.2.14 LOGIC DIAGRAM L-15

- 8.1.2.15 LOGIC DIAGRAM L-15 8.1.2.16 LOGIC DIAGRAM L-17

LOGIC DIAGRAM L-7 8.1.2.8 LOGIC DIAGRAM L-8

- 8.1.2.17 LOGIC DIAGRAM L-18 8.1.2.18 LOGIC DIAGRAM L-19

GENERAL-PURPOSE COMPUTING

- 8. 8.1 8.1.3 LIST OF SIGNALS USED IN LOGIC DIAGRAMS L-1 TO L-19

- 8.1.4 LOGIC DIAGRAMS L-1 THROUGH L-19

- 8.2 RAP 2 SYSTEM CHARACTERIZATION AND MEASUREMENT

- 8.2.1 OVERVIEW

- 8.2.2 SOFTWARE CHARACTERIZATION

- 8.2.2.1 DEFINITION OF CHARACTERISTIC TIMES

- COMPILATION TIME INPUT FORMATTING TIME

- OUTPUT FORMATTING TIME RESPONSE TIME

- 8.2.2.2 MAJOR PROGRAM STEPS

- 8.2.2.3 PROCEDURES FOR TIME ESTIMATION

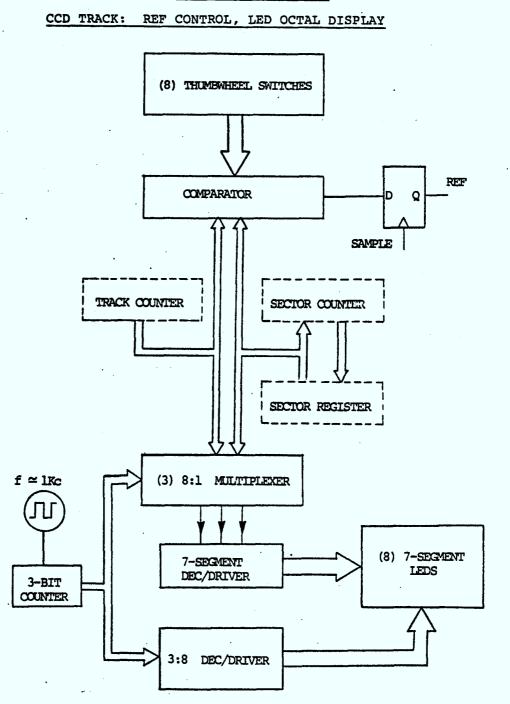

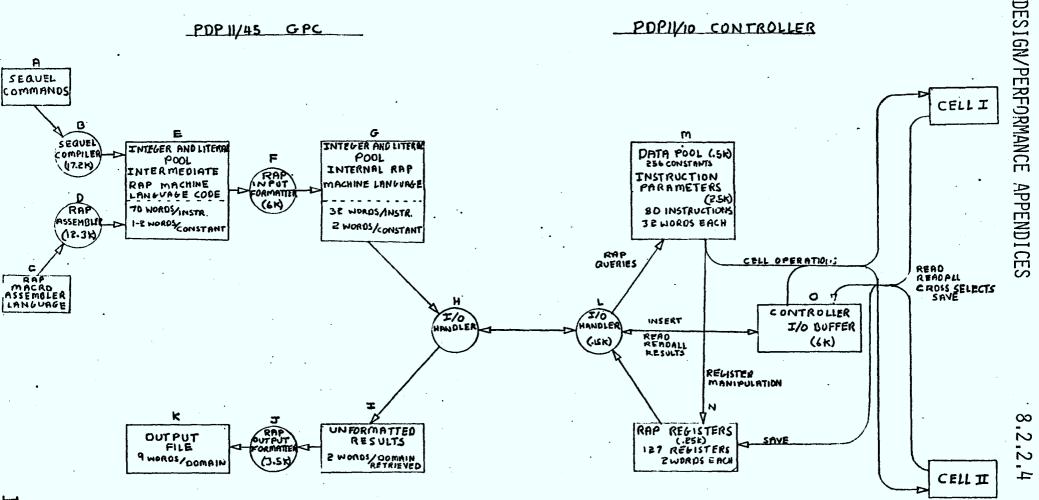

- 8.2.2.4 SOFTWARE COMMUNICATION BLOCK DIAGRAM

- 8.2.2.5 EXECUTION TIME ESTIMATES

- 8.2.2.6 DEMONSTRATION QUERY STATISTICS

- 8.2.3 HARDWARE CHARACTERIZATION

- 8.2.3.1 MODULE DEFINITION

- UNIBUS

- DHB INTERFACE

- CELL INTERFACE

- CELL 1, 11

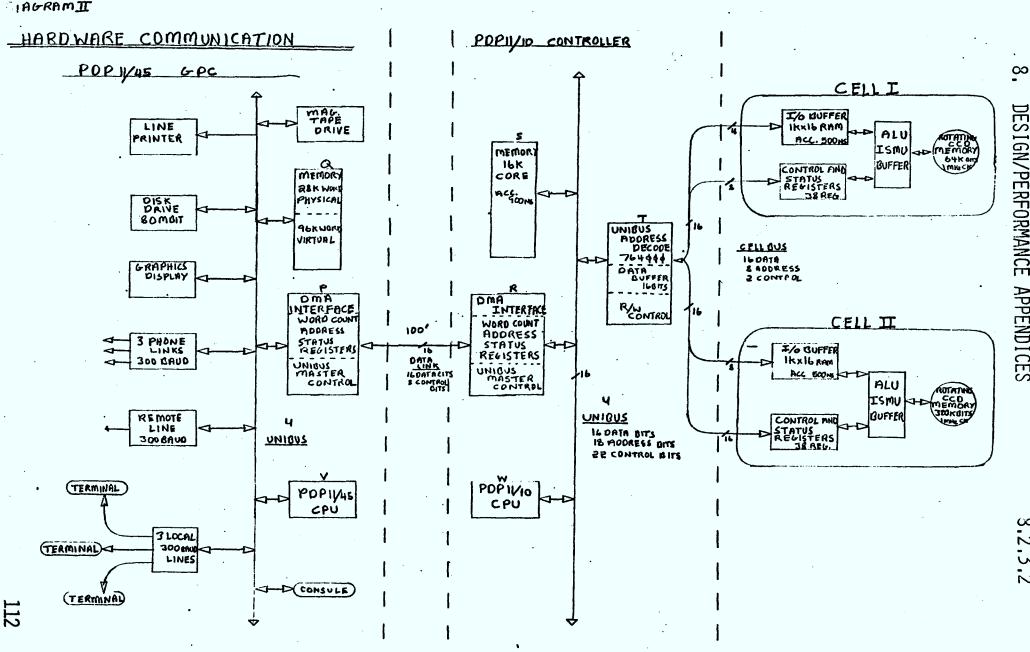

- 8.2.3.2 HARDWARE COMMUNICATION BLOCK DIAGRAM

- 8.2.3.3 DMA RATES 8.2.3.4 RELATIVE SPEEDS

- 8.2.4 RAP DEMO

- 8.2.5 DATA MANAGEMENT BY RAP

- 9. MISCELLANEOUS

- 9.1 DOCUMENTATION CATALOGUING SYSTEM

- 9.2 INTEL PRODUCT PROSPECTUS "A DATA BASE COMPUTER"

- 9.3 PHOTOGRAPHS

- 9.3.1 RAP CELLS AND MEMORY

- 9.3.2 RAP CONTROLLER PDP 11/05 9.3.3 HOST MACHINE PDP 11/45

- 9.3.4 RAP II CELL BOARDB

- ALU .

- 111 300290 FORMATT 1 FORMATT II I/O BUFFER CONTROLLER I

- CONTROLLER II DATA MANIPULATOR

- 9.3.5 RAP II MEMORY BOARDS CONTROLLER (FOR 1.5M BITS) MEMORY (320K BITS)

- 9.3.6 RAP II INTERFACES CELL TO CONTPOLLER CONTROLLER TO HOST

- 9.3.7 SOME OF THE RAP TEAM (FROM THE LEFT NOUVEN, PEREIRA, PATKOW, HUDYMA, SMITH, SOONG, SCHUSTER, RADACZ, HAWKINS, KLEBINOFF.

### 0.0.0

1

### **O. OVERVIEW**

### 0.0.0. Overview

This report is intended to summarize, in a modest way, a jor effort conducted at the University of Toronto by the Computer Systems Research Group • with staff and students of the Department of Computer Science, the Department of Electrical Engineering and staff and resources of the Computer Research Facility (CRF). The project received direct support of \$199,065 via the Department of Supply and Services (DSS) and the Department of Communications (DOC) of the Government of Canada. In addition it has benefitted by close relationships with a variety of individuals and organizations who have provided a great deal of assistance both motivational and tnagible. Very high on the long list of individuals and organizations are, Dr. A.R. Elliott of the Department of Communications, Dr. R.F. Webb of R.F. Webb Corporation LTd. and Gordon Moore of Intel Corporation.

Direct costs of the RAP project from all sources including those supported by National Research Council (NRC) operating grant funds are estimated to be \$218,000. Not included are expenditures by DOC on market studies through R.F. Webb Corporation Ltd. and by INTEL on various associated studies (see Section 9.2).

The RAP project itself occupied an elapsed time of 23 months following the original 15 month period of definition by E.A. Ozkarahan in preparing his Ph.D. thesis entitled "An Associative Processor for Relational Data Bases RAP", presented in Jaunary 1976. A total of 21 persons worked on the project at the University of Toronto providing a total of more than 12 man years since 1975 and 1 1/2 (largely by EA) before than time.

The summary presented here is a very brief distillaion of a large amount of documented concept, design, experiment, and interacion with others. Estimates of its statistics include:

- a) A 350 page thesis.

- b) 6 CSRG reports of 225 pages in total.

- c) A categorized documentation system estimated to hold 1,500 pages. The cataglouging system and table of contents is included in Section 9.1 for interest.

- d) 8 conference/workshop presentations.

O. OVERVIEW

0.0.0

2

- e) 6 papers published in journals/proceedings, of 60 pages in total.

- f) Visits by RAP staff to 18 organizations as part of an industrial liason program leading to the study reported by R.F. Webb.

- g) Visits by 30 individuals from 10 organizations to view the RAP work.

- h) 75 written enquiries and requests for RAP information.

- i) 15 interim/progress reports to DOC.

- j) 12 terminal demonstrations of RAP locally.

- k) 1 terminal demonstration of RAP elsewhere.

- 1) 3 M.Sc. completed.

- m) 1 Ph.D. completed.

The present status of RAP is a physical system demonstrable within the boards of timescale and availability characteristic of a multiple user system of the computer-hardware consisting of:

- One communications-linked input terminal running SEQUEL or RAP connected to a:

- 2) PDP 11/45 well-equipped processor running UNIX, connected to a:

- 3) PDP 11/10 controller via a 100 foot, 3 byte-paralle link, driving a:

- 4) CELLBUS with 250 cell capacity to which is attached:

- 5) Two CELLS each having:

- 6) CCD Memory of 320K bits capacity, all controllable also from

- 7) an input terminal to the PDP 11/10 controller communicating in RAP ASSEMBLER.

#### Read on!

1. INTRODUCTION

### 1. INTRODUCTION

1.

3

RAP - a Relational Associative Processor - is a back-end or peripheral device designed to augment a general purpose computer for implementing a data base management system (DBMS). Its architecture is based on the fact that data base operations are inherently set-oriented and data base addressing is best accomplished through associative reference to achieve high data independence. RAP utilizes these characteristics by combining the features of associative and array processors.

Previous publications on RAP have dealt separately with the details of the first version of its architecture (1,2,3,4), language interface (5,6,), and performance evaluation (7,8,9,). Also, these topics were discussed strictly from the point of view of the relational model of data. This report provides details on the recently evolved, faster, and more flexible architecture and discusses RAP's applicability to a wider range of data base models and its various uses and roles within a complete DBMS implementation. Further its role in communications is highlighted. In this introduction, we will try to motivate the need for a RAP-like device in DBMS implementations. First, we review some important requirements for these systems. A discussion follows of the limitations of conventional computers in meeting these requirements. The philosophy of using array/associative machines for data base management is then presented. The introduction concludes with the global organization of the RAP processor.

### 1.1 Data Base Management Systems Requirements

Data base management systems attempt to isolate the details of data storage and manipulation from the application programmers that use the data (10). This is accomplished by providing users a <u>logical view</u> of a data base distinct from the details of its physical realization, a <u>query</u> or <u>data manipulation language</u> by which users can specify or program the retrievals and updates of data, and a <u>data definition</u> language to define and control access to data. The success to which DBMS can realize the above goals depends heavily upon meeting the following three important requirements. First, query languages must be sufficiently high-level and powerful to permit non-procedural specifications of complex data manipulation. Such languages allow users to specify manipulations in a set-oriented fashion (e.g., retrieve or update all employees...) and addresses of the data associatively by qualifying items stored in the data base (e.g.,... employees who work in the furniture department). The higher the level of query language, the faster and easier it is to code understandable and reliable application systems. Also, high-level query languages can easily be extended to provide stand-alone interactive facilities to users, e.g. engineers, physicians, financial analysts, etc., who are not computer specialists but who are technically oriented and specialize in the semantics of the data being processed.

Secondly, fast response is required because the majority of DBMS will be required to operate in on-line and concurrent user environments which support users at terminals, batch application programs running within multi-tasking systems, and communication and networking systems providing access to distributed data bases.

The third requirement concerns the technical administration of data base systems. The separation of the logical view of data from its physical reality, as provided by data base systems, forces the responsibility of providing efficient performance to be delegated to the data base administrator of the system. This responsibility was originally distributed over several users and distinct file processing systems. Now the data base administrator must make decisions, often conflicting with individual user requirements, for all users. The complexity of this task is enormous in current implementations. It is imperative that tuning of data base systems be effectively and easily achieved.

1.1

### 1.2 Problems with Conventional Implementation

Using conventional computers and traditional secondary memories to implement data base systems makes it difficult to realize the requirements of data base systems and contributes greatly to the high cost of using data bases. The problems of conventional computers arise because of their processing and addressing structure. Conventional machines are designed to process data serially (i.e., the execution of one instruction on a single data item at a time) and that accessing of the data to be processed is accomplished by specifying its location or hardware address. Unfortunately, this is in direct conflict with set-oriented processing and associative addressing in data base systems.

The lack of set-oriented and associative features in conventional architectures force the implementors to achieve equivalent operations by simulating them with software. Accordingly, to implement efficient access to a data base, large complex programs must be written to provide <u>mapping</u> <u>mechanisms</u> that map the users view into the structure of the hardware and provide <u>access paths</u> to facilitate fast location of arbitrary portions of the data base. Access paths refer to both indexing data and software designed to provide access to specific items of the data base. Additional software must also be provided to maintain access paths. Some of the problems caused by the use of access paths and mapping mechanisms in conventional computer implementations of DBMS are:

a) Unbalanced Performance:

Access paths provide fast retrieval of data at the expense of slower updates because updates to the data base must also be reflected in the access paths.

b) Poor Generalized Performance:

Generalized systems based on access paths rely on multi-level software do not permit sufficiently tunable generalized systems that respond to

1.2

### 1. INTRODUCTION

widely varying applications in dynamic user environments.

- c) Reduced Potential for Exploiting Concurrency:

Because access paths must be updated whenever the data base is modified,

they become additional critical resources that require synchronization

to avoid interference in a shared environment. The additional synchronization

adds overhead to a data base system.

- d) Reduced Reliability:

System failures, especially during updates, can cause the access paths and mapping mechanisms to become inconsistent with the data base. Detection and recovery can be very complex and time consuming.

e) Extra Storage Requirements:

Access paths are often implemented by "inverting" the values occurring in the data base. This technique organizes the physical addresses of data items into search data base creating a second data base requiring extra storage.

f) Software Complexity:

As a consequence of added data structures for implementing access paths and mapping techniques, large complex software is required that is unreliable and dificult to maintain and administer.

A major consequence of these problems is that only those queries whose formulation were preconceived can be conveniently and efficiently processed. The result is that general purpose data base management systems, which must meet the requirements of many applications over broad user environments, perform in a limited fashion in practice. The traditional approach to solving the performance problem has been to acquire faster CPUs and larger primary memories at, of course, tremendous expense. Clearly, this solution does not solve any data base administration problems.

1.3 The Associative/Array Processor Approach

A solution to the limitations of conventional computers for implementing

and administrating a DBMS would be to establish a computer architecture that eliminates, or, at least, reduces the dependency on complex software. The new architecture should close the gap between the users logical view and processing requirements and the way the data is represented and processed physically. This can be partially accomplished by utilizing a high degree of parallelism for both processing and addressing. If the parallelism is achieved by repeated cellular logic each operating on its own memory, then the data base system requirement of performing the same operation on many data item operands can be efficiently accomplished. Inexpensive associative memories can be achieved by using block addressable serial memories and searching their contents at high speed in parallel.

Furthermore, if such device were designed to augment, rather than replace, a conventional computer, it would have a greater chance of overcoming the natural resistance to a radically new technology by providing a evolutionary approach to total DBMS architecture. Other benefits of moving the majority of data base processing to a back-end organization can be found in (11). We will discuss them with respect to RAP shortly. Designs other than RAP, that prescribe to this approach in various degrees, can also be found in the literature (12-16).

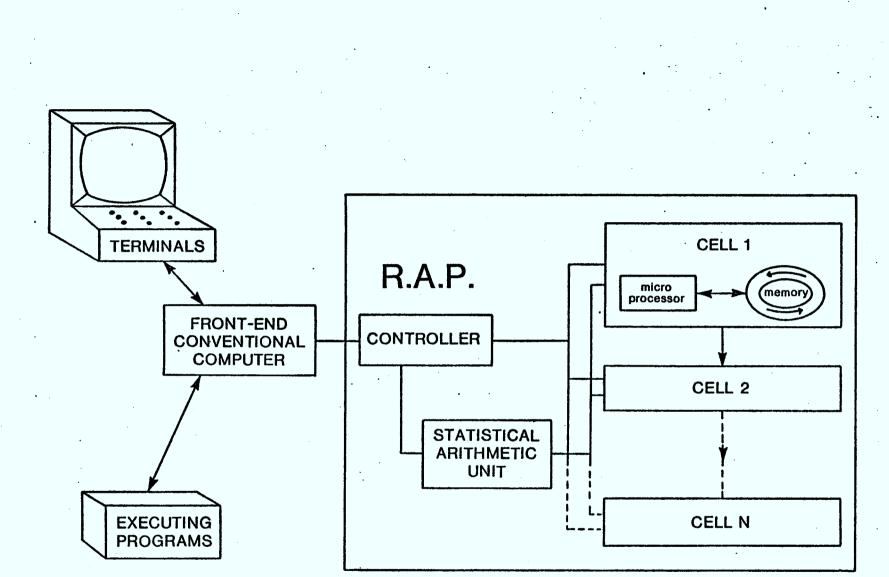

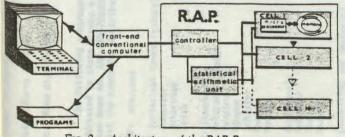

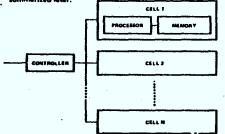

1.4 Basic Architecture of RAP

The basic architecture of a RAP device consists of a "chain" of parallel components called <u>cells</u>, a statistical arithmetic unit, and central controller. This organization is shown in Figure 1. Each cell is composed of a processor and block addressable memory. The processor is specifically constructed for data base definition, insertion, deletion, update, and retrieval primitives. Logic for each processor has been designed to be compatible with LSI circuit implementation technology. The memory can be implemented by a rotating magnetic device such as the track of a disk or drum, semiconductor CCD, or bubble memory. The statistical arithmetic unit is designed for computing summary statistics (e.g. totals, averages, etc. over the combined contents of the cell memories. The controller is responsible for

# 1. INTRODUCTION

receiving instructions in RAP machine format from a general purpose front-end, gomputer decoding them, broadcasting control sequences to initiate cell execution, and passingretrieved or inserted items between the front-end and RAP. Each RAP instruction is executed within the cells which operate in parallel directly on the data. Simple intercell communication for priority polling is implemented along the chain. Each memory contains data formated into a sequence of records containing values of data items. The details will be given shortly.

A cell is composed of several logic units. The most important being involved with searching. Several comparitor elements form the basis of the associative addressing architecture of a cell. The comparitors can independently test the contents of one item in the data base against several literals or several items each against different literals. The true or false results of comparison tests on a record can be combined into a disjunctive or conjuctive result to determine if the record associatively qualifies for further manipulation.

The front-end computer supports high-level user functions. It interfaces users to to RAP by supporting communications via interactive terminals or through programming language CALL and I/O statements for application programs running in batch multiprogramming operating systems. The translation of various query languages into RAP programs will also be accomplished in the front-end. Data base system software responsib for coordinating multiple and diverse secondary storage devices other than RAP, scheduling of queries, and maintaining protection, security, and integrity must also be supported in the front-end but can be aided by the data processing capabilaties of RAP.

1.4

. . .

The RAP system has a machine-oriented yet high-level and complete instruction set for manipulating its data base. Most macro-assembler instructions correspond to one machine instruction which involves severa! cell micro-code instructions. In this section, an explanation of the RAP macro-assembler instructions will be presented. A programmers view of the RAP data structure will be given first. Then the basic structure of a RAP instruction will be given followed by the description of each individual instruction.

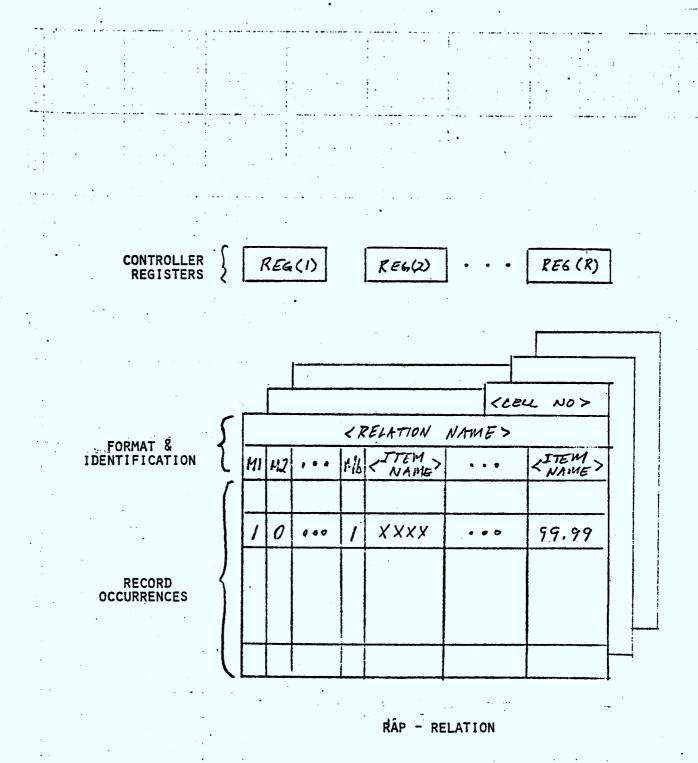

2.1 Data Structure

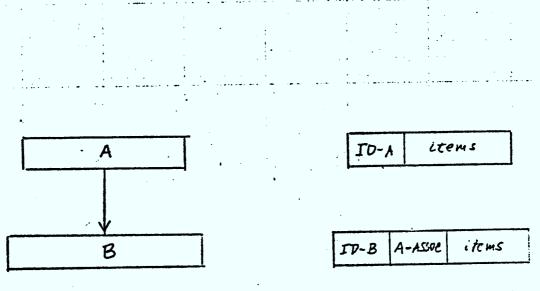

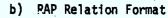

From a programmer's view, RAP stores data as unordered occurrences of records defined by a <u>RAP relation</u> as shown in Figure 2. A relation can be envisioned as a formatted table of data where rows of the table represent a set of record occurrences sometimes called <u>tuples</u> in relational terminology. The occurrences of a relation stores data about a set of similar entities (e.g. persons, places, things, or relationships). The name of a relation identifies the set of entities. The format of record occurrences is defined by naming the <u>data items</u> whose concatenated values occur in each record and specifying their length. The length of each item in the relation is fixed according to a users choice of one of several sizes. Each occurrence of a relation stores data which describes a particular entity by assigning a value to each of the items according to the format of the relation The values are treated internally as simple bit patterns for non-numeric data and as integers in twos - complement format for numeric data.

Each relation and its occurrences are augmented by several special one bit items called <u>mark bits</u>. These items can be set to 0 or 1 under user control through various marking instructions or by the intermediate operations of other instructions. The bits are used primarily as a work area to temporarily indicate subsets of record occurrences so that the results of one instruction can be used in subsequent instructions. This is done by treating the mark bits as normal data items to be tested during associative addressing.

2.

FIGURE 2 - RAP LOGICAL DATA STRUCTURES

11

The occurrences of a relation can occupy one or several cell memories, but each cell can only store occurrences from one relation. Therefore, a single RAP device can contain occurrences from one large relation or from N relations, one for each of N cells. The programmer of a query need not be aware of the cell location or number of cells occupied by the relations. However, there are occasions, such as during garbage collection or bulk loading, where the user needs to control the device at a cell level. To permit this, a user can refer to registers containing an integer address for each cell.

Several registers are also available in the controller. These can be used to store intermediate computations or retrieved data from relations and used as search values or tested in subsequent instructions to executed complex queries.

A RAP relation is an intermediate-level abstraction of large data bases. Although it has a flat tabular structure, it is not quite relational as defined by Codd. For example, duplicate records are permitted and their existence is not automatically detected. There are physical limitations on sizes and numbers of items. Also, the special hardware operations for mark bit manipulation is a form of hardwired "access method" that a user must control via program instructions to select desired data for further processing. What RAP does is to provide a data view or model that is high-level but flexible or general enough to easily support software implementations of set-oriented versions of common user views such as hierarchies, networks, and relations. An outline of how RAP can do this is presented later.

2.2 Instruction Format

The general format of most RAP instructions is:

<label> <opcode> <mark option> (<object> : qualification> ) (<parameter> )

Exceptions will be noted as they arrive. The label is an optional symbolic

instruction address, the opcode specifies the data manipulation operation.

A mark option can take one of the following forms:

2.1

- a) <null>, implies no marking is done.

- b) MARK <bit specification>, Sets (to 1) the mark bit data items specified in the bit specification of the qualified tuples.

- c) RESET <bit specification>, resets (to 0) the mark bit data items specifiedby the bit specification of the qualified tuples.

2.2

The individual mark bits will be donoted M1, M2, ..., Mb where b is the hardware parameter limiting the number of mark bits. A bit specification is simply a list of mark bit names. An object has one of the following formats and is used primarily to specify which cells are to be manipulated by the instruction:

- a) n(D1, ..., Ds) where Rn is a relation name and (D1, D2,...Ds) is a list of data item names associated with relation Rn. The data item list is optional or not relevant in many instructions. The index s is a hardware limit on the number of domain names that can be included for certain instructions.

- b) List of cell address, CELL(i), where i the integer address of the i-th cell.A qualification in the RAP instruction format can take one of the following forms:

a) <null>,implying every tuple of the relation qualifies.

- b) Q1& Q2& Q3 ... & Qp denoting the conjunction of simple conditions Qi.

- c) Q1 1 Q2 1 Q3 ... LQp denoting the disjunction of simple conditions Qi.

A simple condition Qi can be any one of the following:

a) <Di> <comparator> <operand>

where i) Di is a data item name

- ii) comparator is one of:=,#,<,<,>,>

- iii) operand is one of REG (i), <integer>, '<literal>', where REG(i)

refers to the contents of the i-th controller register.

- b) MKED (Mi) denoting the mark bit test Mi = 1.

- c) UNMKED (Mi) denoting the mark bit test Mi = 0.

- d) CELL (i) indicating that the cell address is tested as part of the qualification.

A qualification has certain restrictions which are not apparent from the description of its syntax. A qualification can have at most k simple conditions of type (a) (i.e., data item comparisons) and fimple conditions of types (b) and (c). Only one simple condition of type, may be included in any qualification.

The format of parameter varies greatly and will be explained along with each instruction that requires additional information not supplied above.

2.3 Description of RAP Instructions

2.3.1 Selection

<u>Select</u>:

<label> Select <mark option> (Rn : <qualification>)

This instruction selects qualified tuples from the relation Rn and sets or resets the mark bits of these tuples according to the mark option given. For example, the instruction:

Select Mark (M1M2) (R1 : D1 = 'a')

will set mark bits M1 and M2 of tuples in R1 which have D1 = 'a'. Whereas the instruction:

Select Reset (M1M2) (R1 : D1 = 'a')

will reset the mark bits M1 and M2. A null operation occurs when the mark option is omitted.

Cross Select:

<label> Cross\_Select <mark option on R1> (<R1> <D1> <comparator> <R2>.<D2>)

(<R2> <mark option on R2> : <qualification>)

This instruction involves operation between two relations called source (R2) and target (R1). It works like a repetitive select instruction on the target relation with the exception that qualification for each selection is obtained from the source relation data item values. That is, in order to select a target relation (R1) tuple, the items D1 and D2 respectively of target and source relation must have comparable values (i.e., values from the same domain) that satisfy the comparison between them.

The source tuples participating in the comparison are those which satisfy the second qualification.

For example:

Cross\_Select Mark (M2) (R1 : D1 < R2.D2)

(R2 Reset (M1) : D4 = 8)

Source tuples participating in the comparison are those which satisfy the qualification D4 = 8. Notice the M1 mark bit of the participating tuples of the source relation will be reset due to the mark option on R2. In order for tuples of R1 to be M2 marked, it must have values of the D1 item less than the value of one D2 item of the participating source tuples. To further illustrate this, suppose R1 and R2 have the following values:

#### R1 (target relation) R2 (source relation) Tuple # D1 Tuple # D2 D4 1 15 10 7 1 2 6 2 4 8 3 9 3 11 8

The participating source tuples are tuple 2 & 3 from R2 since they satisfy the condition D4 = 8. The tuples of the target relation that will be M2 marked are tuples 2, 3 and 5 because they meet the condition on R1 that D1 < R2.D2. A null operation will result if both mark options of R1 and R2 are missing.

#### 2.3.2 Retrieval

#### Read All:

30

T

4 5

<label> Read-All <mark option> (Rn (D1, ..., Ds) : <qualification>) (<work area>)

This instruction transfers data from all tuples of Rn satisfying the qualifications

to the supporting processor's storage address as specified by work area. This could

be a seugence of primary memory addresses or a file designation. If the object

data item list is present, only those item values are read out, otherwise, the

entire eligible tuple is transfered. If the mark option is present, the mark bit items of the eligible tuples will be set or reset according to the given mark option. For example:

Read-All Reset (MIM2) (RI (D1,D2):mked (MI) & mked (m2) & D3 = 10) (file.0) Eligible tuples in this case are those which are MIM2 and marked and have D3 = 10. Notice only DI and D2 of eligible tuples will be read into file .0. MI and M2 mark bits of the eligible tuples will be reset.

Read:

Save:

<label> Save (n) <mark option> (Rn(D1,...,Ds):<qualification>) (<register list>)

Save (n) transfers data items from qualified tuples of a relation to registers of

the RAP controller. Only items from the "first" n or less eligible tuples are

transfered. If the mark option is present, the mark bits of the tuples will be set

or reset according to the mark option. If the data element list is not present,

the entire tuple will be transfered, otherwise, only those items in the list are

read into the registers. Values will be stored left justified and padded on the

right with blanks. Data elements with arithmetic domains will be assumed to be a

fixed word length in twos-complement format.

Register list can take on any combination of the following 2 forms:

a) Reg (i), Reg (j),..., Reg (k)

b) Reg (i) - Reg (j), i < j

where Reg (i) - Reg (j) means Reg (i), Reg (i + 1),..., Reg (j). The transfer is done in the order given, that is, the first item in the object list is read into the first register designated in the register list, second item into the second

register, etc. The n items are read from each tuple, the first item of the second eligible tuple will be read into the n+l register in the register list.

2.3.2

17

Read Reg:

<label> Read\_Reg (<Reg\_list>) (<work area>).

This instruction transfers contents of the specified RAP registers to the supporting processor. Register list has the same format as the register list in the save instruction.

2.3.3 Statistical Computations

Sum, Count, Max, Min:

<label> <sopr> <mark option> (Rn(Dn):<qualification>) (Reg (i))

where sopr is one of the statistical function operators sum, count, max or min.

The opcode count counts eligible tuples in the relation Rn and places the result

in the register specified. (Dn) is omitted for this statistical function. The

other instructions compute the specified function over the numeric domain of item

Dn from qualified tuples. Mark bits of the qualified tuples can be set or reset

by the presence of the mark option.

2.3.4 Update

<label> <opr> <mark option> (Rn(Dn):<qualification>) (<opd> )

where opr is one of the operators add, sub or replace and opd is either a constant, a data item name, or a RAP register. Item Dn in every eligible tuple is operated on by opr. Like previous instructions, the mark bits of the eligible tuples can be set or reset by the presence of the mark option.

2.3.5 Insertion and Delection

Delete:

<label> Delete (Rn : <qualification>)

Tuples of relation Rn qualifying for deletion has their delete flag bit set causing the tuple to be ignored in subsequent operations.

### <u>Colgrbg</u>:

<label> Colgrbg (<relation list> and/or <cell list> )

This instruction initiates the physical deletion of all delete-flagged tuples

of thelisted relations and/or listed cells. The data is packed towards the

beginning leaving garbage accumulated towards the end of the cell memory. The

cell list has the same format as a register list. The relation list has the

following format:

(R1, R2, ..., Rn)

Space Count:

<label> Space\_Count (Rn : <cell list> ) (Reg (i))

This instruction will examine the cells of relation Rn and returns a value indicating the number of available spaces in these cells. This value is stored into the given register. Available spaces include both empty tuples and the delete-flagged tuples. If the optional cell list is present, only those cells in the cell list will be examined. All cells in the cell list must belong to relation Rn. This instruction is usually used to test for space before an Insert instruction is used.

Insert:

<label> Insert (n) (Rn : <cell list>) (<work area>)

Work area is the front-end processor's program storage location containing the

n tuples to be inserted. If the optional cell list is given, the n tuples will

be inserted in those cells only. There is an arbitrary hardware upper limit

on the number of characters that can be inserted in one INSERT instruction

which places a limit on n.

2.3.6 Data Definition

Destroy:

<label> Destroy (Rn : <cell list>)

This instruction deletes the tuples, format, and names of the specified cells of

a relation. If a cell list is not present, the relation is removed from all the cells it occupies. A special null relation name is reserved for all blank cells.

#### <u>Create</u>:

<label> Create (Rn : <cell list>) (<format>)

One execution of this instruction formats each cell in the cell list for relation Rn. Empty tuples are delete flagged on the created cells. Format contains parametric data about the length of the data items stored in a relation. 2.3.7 <u>Register Manipulation</u>

**Only** registers containing valid integer values will result in meaningful numeric computations. All register arithmetic will assume word length operands on the **left-most** bits of controller registers.

### Insert Reg:

Dec Reg, Inc Reg:

<label> Dec\_Reg (Reg (i))

<label> Inc\_Reg (Reg (i))

The instruction Dec\_Reg performs the following operation:

**Reg** (i) = Reg (i) - 1

The instruction Inc\_Reg does the following:

**Reg (i)** = Reg (i) + 1

### **Register** Arithmetic:

<label> <ropr> (Reg (i)) (<ropd>)

where ropr is one of the operators; Radd, Rsub, Rmul Rdiv and ropd can either be an integer or another register.

### 2.3.8 Decision and Transfer

### <u>BC:</u>

<label> BC <label> , <boolean expression of conditions>

where BC is the abbreviation for "branch on condition". Condition can be

one of the following :

a) null -- this implies the instruction is treated as an unconditional branch

b) Reg (i) <comparator> Reg (i)

c) Reg (i) <comparator> <constant>

d) Test (Rn : <mark qualification>)

If the boolean condition is true, branching will take place, otherwise control is given to the next instruction.

Condition type (d) tests each individual mark bit of specified by the mark qualification separately and if the test is met for at least one tuple (not necessry) the same one) of relation Rn then the test is true, otherwise, the test is false. Mark qualification can be either disjunctive or conjunctive. For example:

Test (RI. : MKED (M1) & MKED (M2))

is true if the M1 mark bit is set to one for at least one tuple and the M2 mark bit is set to one for at least one tuple (not necessary the same one), otherwise the test is false.

E0Q:

<label> E00

This indicates the end of a RAP program.

### 2.4 <u>Summary of Performance</u>

Execution times depend on the speed of the cell processor and the capacity of a cell memory. These could vary greatly depending on choice of technology and architecture of the processor and memory. Therefore, we give a summary in terms of the number of searches or scans of the memory are required to execute on instruction.

TYPE OF OPERATION EXECUTION TIME (IN # OF SEARCHES) INSTRUCTION Select Selection 1 + (# of source tuples/k) Cross\_Select Retrieval 1 + transfer time Read-all Read (n) 2 + transfer time Read\_Reg 0 Save (n) 2 1 Statistical Functions Sum 1 Count Max 1 Min Update Add Subs 1 1 Replace Insertion & Deletion Delete 1 1 Colgrbg Space Count 1 Insert ('n) 1 Data Definition Create 1 Destroy 0 Register Manipulation Insert\_Reg ٥ Inc\_Reg Δ Dec\_Reg n

| INSTRUCTION | EXECUTION TIME (IN # OF SEARCHES)  |

|-------------|------------------------------------|

| Radd        | 0                                  |

| Rsub        | 0                                  |

| Rmu 1       | 0                                  |

| Rdiv        | 0                                  |

| BC          | 0                                  |

| EOQ         | 0                                  |

|             | Radd<br>Rsub<br>Rmul<br>Rdiv<br>BC |

An important feature of the RAP instruction set is that it is <u>relationally</u> <u>complete</u>. This means that any query expressable by the relational calculus can be implemented entirely within the RAP processor. This eliminates the need to transfer extensive amounts of data derived from the intermediate results of query processing between RAP and the supporting computer.

It is important to note that each high-level instruction operates on at most two entire relations during its execution. The hardware is naturally locked during an instruction execution. Thus all software schemes concerned with mutual exclusion of update operations can simply implement synchronization mechanisms at the relation level. This eliminates much of the operating system overhead incurred by conventional implementations.

Studies have been conducted to compare the hypothetical performances of the original RAP architecture relative to a conventional computer system for implementing a relational data base (8). Both appoaches were modeled analytically. The models considered resident data bases for the original RAP architecture and fast access paths in the form of inverted lists for the conventional system. The results show that significant gains in query execution speed can be achieved by the RAP architecture over the conventional system. Furthermore, the newer architecture improves this gain substantially. The model studied queries of the form: retrievals and updates on rows of relations selected with respect to simple and complex boobon qualifications, retrievals that include statistical criteria in the

selection qualification, and retrievals involving the implicit join of two or more relations. This study indicates that, under many circumstances, on-line retrievals and updates of large data bases may only be possible with the use of RAP-like Systems.

23

### 3. IMPLEMENTATION

### 3.1 <u>History</u>

The RAP project was started in 1975 in the computer systems Research Group at the University of Toronto in order to implement a data base system based on the on the relational model in hardware. It started with the direct implementation of the logic specified in Ozkarahan's thesis (4) and in 1976 resulted in a system (hereafter called RAP.1) consisting of two cells. The RAP.1 system consisted of a hardwired controller and where each cell had its own memory <u>track</u> where a portion of a relation is stored. The format and timing of a track is modeled on disk technology.

In RAP, 1, all components of the system were required to be synchronized by one single clock, all tracks had to be of equal length, and inter-cell communication required data flow between all cells. Every operation concerning data on the track took one or many "revolutions"; a revolution is the time it takes to serially scan a track.

During the project two important decisions were made to change the architecture of RAP.1 which resulted in the design and implementation of RAP.2. First, the controller was to be implemented by a mini/micro computer. Second, the data track was designed around the capabilities of emerging block addressible technology instead of disk. A hardwired implementation of the controller was found to be inflexable and speed was not an issue. The Development of a disk system that meets the requirements of a RAP system was difficult because of synchronization and error correction problems. Furthermore, there is a widespread belief CCD, bubbles and/or electrom beam technologies will eventually cause disks to be phased out.

The use of a general purpose computer as the controller resulted in dramatic changes in the RAP architecture. Due to the flexibility of the computer, a major

redistribution of the work-load became feasible. In RAP.2, the cells are greately simplified and asked to do only those tasks related directly to their tracks while the controller takes care of the rest. Because the controller is inherently slow and cannot cope with the speed of the cell, it became important to decouple cell synchronization from the controller. The new work-load distribution also frees every cell from the task of sending data directly to other cells. This can be done through the controller. Each cell can operate independently of other cells and the controller. As a by-product each cell can have its own track length. RAP.2 looks like a conventional computer system with the controller coordinating the tasks of many cells which are treated as independent peripheral devices attached to bus lines.

3.1

25

In summer of 1977, a RAP.2 prototype of 2 cells and query language software were demonstrated. Each cell contained a million bit CCD track built from Intel's 2416. The controller was a PDP11/10. The RAP.2 was interfaced to a PDP11/45 as a DMA device. To make the transistion from RAP.1 to RAP.2 as fast as possible, it was decided that only essential changes were allowed. Consequently, RAP.2 is far from perfect and its performance can be greatly improved. In this paper we refer to enhancements not yet implemented as features of a future RAP. 3 system. 3.2 <u>Physical Data Organization</u>

In review, data is organized into files called <u>RAP relations</u>. A relation is a collection of records called <u>tuples</u>. Each tuple is a string of many concatenated fields called <u>data items</u> in some fixed order. The number of fields per tuple of a given relation is a constant. Every relation and each of its fields have a name stored in a compactly coded form. In RAP, the length of each item must be constant. In other words, all tuples of a relation share a common FORTRAN-like format. In the RAP.l and RAP.2 prototypes, each tuple can have up to 255 domains and the length of a domain can be either one, two or four bytes of encoded data. In RAP.3, this length can be anywhere from one to n bytes (where n should be 32 bytes or greater). Each cell stores only one relation. If a relation has too many tuples, they can be allocated in many cells.

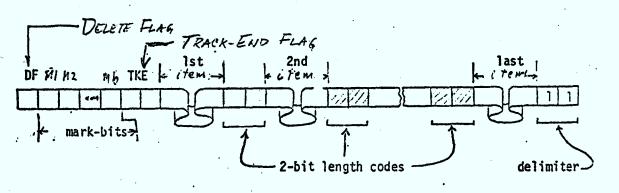

In RAP.1, a cell stores the relation name as well as the cell address at the track head followed by tuples separated by gaps (Fig. 3). Each gap must be at least the size of the longest domain and furthermore, must be such that the block size (i.e., tuple length + gap length) is either 256, 512, 768 or 1024 bits. A tuple is preceded by 7 mark-bits and ended by a 2-bit length code (Fig. 4).

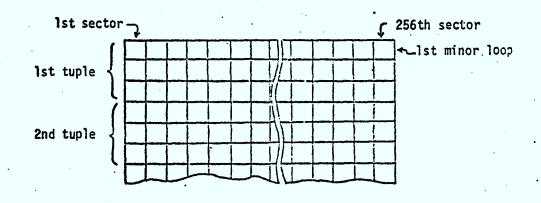

In RAP.2, the cell address is defined by an 8-contact switch set by an operator. The relation name is stored in a 16-bit register and is defined by the programmer. Both the cell address and the relation name can be read out. The CCD memories of each cell behave like a very long drum with many small tracks. of 256 bits each. Due to historical reason, in the remaining part of this paper, by "track" we mean the entire CCD drum and each 256-bit circumference will be called a minor loop. The format for each tuple remains unchanged except that the two-bit space between 2 consecutive domains are left blank since all the length codes are stored in a register called the LENGTH CODE RAM. As for gaps, the only requirement is that each tuple must fit in an arbitrary integral number of minor loops (Fig. 5). RAP.2'simulates a disk read head by the use of a counter which points to the "current" location. The write head can be calculated from the read head by using an adder. For most instructions, the write head is one block behind the read head, in some instructions the two heads are identical. Because of the randomly accessible nature of minor loops, access time is small (the worst case is 256 bit-times). When a cell is not doing anything, it is "on" the first minor loop. In operation, each instruction requires the heads to scan just enough space to complete the job. After an instruction is completed, the heads immediately return to the first minor loop. Due to this property, it is more appropriate to use the term "pass" or "search" instead of "revolution" to indicate the time required to do an instruction. In the worst case, a pass is one revolution. Typically, a pass is porportional to the length of the track portion containing data. Sometimes, as in data retrieval or insertion, a pass

3.2

| Gap | Cell<br>Address | Gap | Relation<br>Name | Gap | lst Tuple | Gap | 2nd Tuple | Gap |   | 7 |

|-----|-----------------|-----|------------------|-----|-----------|-----|-----------|-----|---|---|

|     | 1441 633        |     | ITUING           |     |           | ŀ   |           |     | 1 | 2 |

Fig. 3. RAP. I's data track.

RAP.1 tuple. RAP.2 still keeps the same tuple's space distribution but the 2-bit spaces after domains are left blank.

Fig 5. RAP, 2 "dissected" drum. Drawing shows a file with 3x256-bit tuples. 3.2

ends immediately when enough tuples have been retrieved or inserted.

In RAP.3, storage efficiency is maximized. There is no inter-item space and no gap. A more sophisticated delay mechanism is employed to write data in proper spaces. There is a "return from halt" option (analogous to the "return from subroutine" instruction of some microprocessors) that allows the cell to resume scanning at some previous spot. This option greatly improves execution time where a very large volume of data is inserted or retrieved.

#### 3.3 Global Architecture and Communications

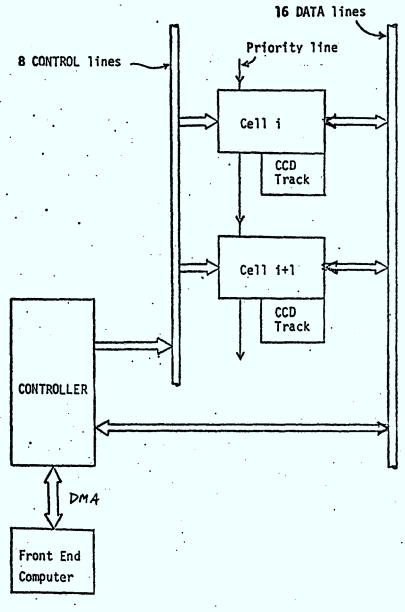

The RAP.2 system is organized as shown in Fig. 6. There are eight control lines and data is exchanged between the cells and controller via a bilateral 16-line bus. There is no direct data link between cells. A DMA link is established between the data bus of the controller and front-end computer.

There is a priority line that runs through all cells to allow fast pulling of individual cells. This is used to control cell access to retrieved intermediate computation, retrieval qualified records or perform bulk loading. The line is not essential but in a large RAP system, the it reduces access time and storage space in the controller. As a variation it is also possible to "fragment" this line; the cells can be grouped where each group has its own priority line.

The reason why the direct data communications between cells lines was dropped in RAP.2 is multifold. First, expensive drivers were required because each cell was able to drive all others. Second, there was the classical transmission line problem requiring the entire RAP.1 system to be crammed into a physically small space. Third, we wanted to desynchronize the system. Last, reliability was questionable when data is sent automatically from any cell directly to all others. If one cell is malfunctioning, the whole system would suffer and diagnosis would have been an extremely difficult task. Furthermore, the amount of information to be exchanged was usually too small to justify the cost of any direct communication link.

DE DATA 16-

Seven of the control lines allow a maximum of 128 micro-code commands called "keys". The eigth control line is named "key enable" and is similar to the "valid data/address" line of microprocessors. In the absence of key enable, the cells ignore everything on the bris lines. Each combination of the seven control lines is interpreted as a command. In practice, these lines are connected to the least significant part of the address bus of a PDP 11/10 controller and the key enable line is decoded from the most significant part and from some other lines. Therefore, each reference to one of 128 ficticous memory locations are reserved for RAP and is interpreted as a key. Some keys are accompanied by an operand which must appear on the data bus, some expect data from cells to be put on the data bus and others are not associated with any data at all.

Commands are broadcasted indiscriminately to all cells of the system. Establishing a scheme to restrict selectively the commands to only one or a few cells is handled by the creation of three state-variables called "open", "blocked" and "rejected". A cell must be open but neither blocked nor rejected to be sensitive to all commands; it ignores most commands otherwise. There are three different ways to open a cell. In the simplest case, the controller can open all cells simultaneously by referring to special keys. The controller can also open any particular cell by its integer designation by storing that value in one key location. Finally, cells can be opened by referencing the name of the relation stored in the cell.

Under some circumstances, it is necessary to restrict the communication to only one cell. For example, in Insert, it is not desirable to have a same tuple to be written in several cells of a same relation. A simple way to achieve this is to open by cell address. This requires, however, that the controller either has to keep track of an address table or to poli all the cells one after another and is therefore suitable only in small systems. The states "blocked" and "rejected"

together with the priority line and the "get next cell" command are intended for this purpose. Consider the following analogy. A number of persons forming a line to buy a ticket in a theatre. Those who have bought one are "rejected"; those who still have to wait are "blocked". The one who is buying is neither blocked nor rejected. Each time the line moves corresponds to "get next". Only open cells are sensitive to a get next cell key. This command rejects the current non-blocked cell and unblocks the first blocked cell. For example, to serve all cells of a relation Rn sequentially, the controller must first open all Rn cells and then block them which is achieved by reffering to another location. It then sequences through a program loop starting with a get next cell and followed by the service routine.

There must be some way allowing the controller to know if there is any cell "listen" to its commands. This is possible by assigning the value "l" to the most significant bit of a cell status register which can be read either selectively or collectively. The controller simply has to read the status to know if its audience is non-existent.

For a cell to respond to a command, the cell must be in a proper state: it must be open, neither blocked nor rejected, and furthermore, not running. The last condition is a measure of protection against any erroneous attempt to change the parameters of a query or the nature of the instruction being executed. Also, the controller has to store relevant data into appropriate reserved memory locations. Many single bit items are grouped in bytes to save time and space.

For I/O each cell has a (1K-word) RAM called the I/O buffer and a pointer which is resettable by the controller. As far as the controller is concerned, for loading, the I/O buffer looks like a single reserved memory location. Every time a word is stored in this location, it is sent to the I/O buffer where pointer is incremented automatically. In this implementation, to insert a set of tuples, all the controller has to do is repeatedly store two bytes at a time in the reserved location.

3.3

# 3. IMPLENTATION

It indicates how many tuples to be inserted by writing this number in another reserved location. After the cell is initiated to run, it will look for enough vacant slots on its track and pull data from its I/O buffer to fill them.

During data retrieval, the opposite is done. The cell looks for desired data on its track and puts them in its I/O buffer. Since the buffer size is limited, the controller must also indicate how many tuples to be retrieved. As far as the controller is concerned, for reading, the I/O buffer also looks like a reserved memory location. The buffer pointer is automatically incremented every time this location is read out.

Besides track data, many other kinds of information of a cell are also available for retrieval by the controller: processing status, cell address, relation name, buffer pointer, result register for computations and the S-counter which contains the number of satisfied tuples in the most recent pass. Access to the buffer pointer allows the establishing of a future DMA link with any cell attached to the data bus for mass transfer of inserted/retrieved data. This could permit DMA transfers directly between cells and the front-end computer.

### 3.4 Instruction Set Execution

An important feature of RAP.2 is that many micro-instructions can be overlapped or carried out simultaneously. After the controller has initiated some cells to do one instruction, it is free to prepare other cells for a new instruction. Since a pass is typically much longer than preparation time, there is virtually no limitation to the degree of concurrency. Software is being developed to exploit this property.

Each macro-instruction is divided into many smaller parts called "tasks". There are three distinct classes of tasks:

(a) The principle class consists of tasks involving the scanning of a track (e.g., writing on a track, finding a blank space on a track, etc.)

These tasks are performed strictly by the cells after being initiated

3.3

to run by the controller. Every cell determines when to stop the execution of a track (e.g. when the physical end of the track is reached). Each task is completed in one single pass which is, under the worst condition, one revolution time.

- (b) The second class consists of tasks done by the controller to the cells (e.g., opening cells, sending operands, etc.). As mentioned before, each task of this kind is carried out by referring to one of the reserved memory locations. Typically, each task of this type takes 1 µsec to be executed.

- (c) The last class does not involve the cells (e.g. register manipulation, DMA communication, etc.). These tasks are accomplished within the front-end computer and/or the controller.

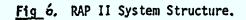

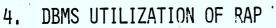

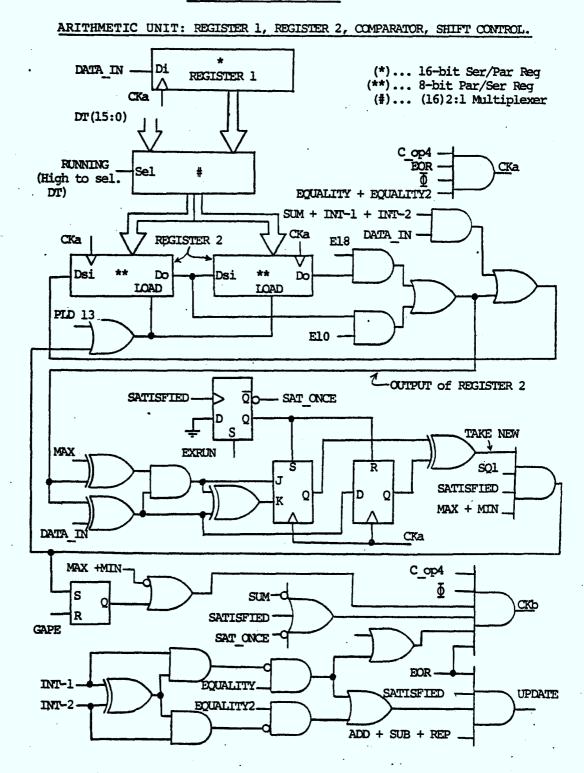

## 3.5 Cell Structure

The structure of a cell can be divided into eight units as shown in Fig. 7. In the following, we will describe briefly the functions of each.

## <u>Cell Interface</u>:

This unit is the part of a cell that "listens" to the outside world. It contains bus receivers and a large decoder that decodes the contents of the control bus. This decoder is prohibited by some states of the cell to make restricted communication feasible. Some of the outputs of the decoder are for steering data from the data bus to appropriate registers. Others are for reading from various places of the cell or for changing states.

The cell address is part of this unit and is defined by an 8-contact switch. The switch setting is constantly compared with the data bus by an address comparator. If matching occurs while the controller is referring to a reserved location the state "lock open" will be high indicating that the cell is open. Once a cell is open, it remains so until specifically told to close.

3.4

3. IMPLEMENTATION

3.

# IMPLEMENTATION

There is a 16-bit relation name register which behaves much the same way as the cell address. The main difference is that it is settable by the user via the controller. Another difference is that if the cell is "destroyed" the relation name comparator is negated, thus opening by relation name becomes impossible. When the cell is given a new name in a future CREATE instruction allowing again opening by relation name.

The logic for "get next cell" is also part of this unit. As mentioned before, every reference to a specific location will affect the states "blocked" and "rejected" of an open cell.

Finally there are also status states indicating whether, in the last pass, there is a mark on bits DF, M1, M2, etc. and a state indicating if there is a satisfied tuple. The most significant bit of the status is always a "1" and is used to indicate the presence of a cell.

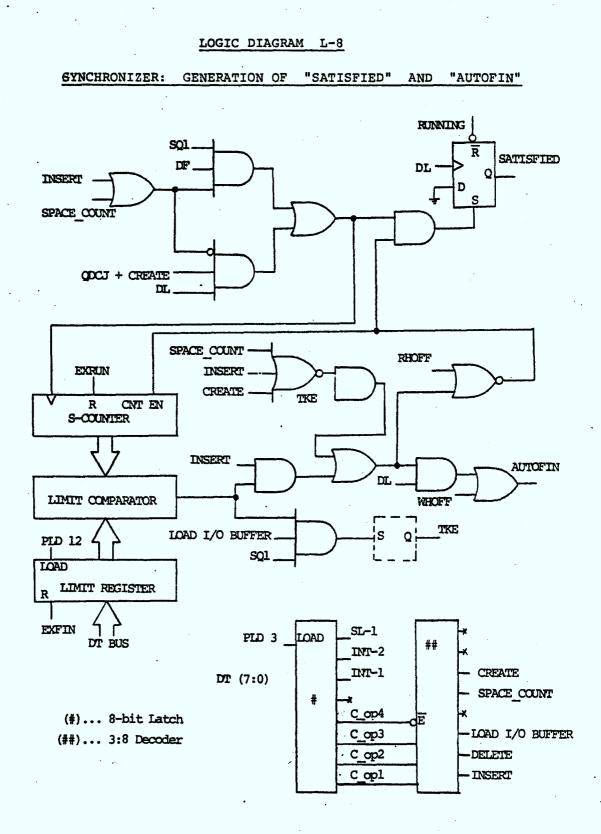

Synchronizer:

This is the largest logic unit of a cell. It provides all timing signals and shift clocks to the rest of the cell except the output multiplexer which does not need any. For simplicity and ease of testing, all basic clock signals are periodic. This implies that there is always a read phase and a write phase for the CCD memories. Consequently, the bit rate of RAP 2 is slightly below 1 MHz. (In RAP 3, read and write phases would be allowed only when necessary). The 1 MHz bit rate is a limit of the CCDs not the cell logic which has been rated at 10 MHz.

There is an 8-bit sector counter that keeps track of the current position on a minor loop. Another (extendable) counter points to the current minor loop. These two counters simulate the read head. The write head is calculated from the other by subtracting the contents of the block size register. A time multiplexing logic allows switching between the two heads. The block size register is loaded

# 3. IMPLEMENTATION

by the controller with the size (number of minor loops) of a tuple during a Create process. For self-testing purpose, some logic has also been incorporated in RAP.2 prototype cells to halt cells to implement the "single step" mode or to slow them down. This is possible by an appropriate manipulation of the read head.

Also, in a Create process, the format of the tuples must be loaded in a 256x2 RAM called the length code Ram (LCR). This allows a maximum of 256 data items per tuple and at most 3 different size of domains. In RAP.3, the width of the LCR is expanded to allow more choices. In operation, the LCR is sampled just before any domain is expected: The contents are passed to the word length counter which decides when to expect the end of the current domain and hence the next domain. These contents are also decoded and sent to the feedback control of various variable-length shift registers to allow their rotation.

• Every time the LCR is loaded or sampled, its pointer is incremented accordingly. The pointer is the contents of the word position counter which keeps track of which item is under scan. There are three 8-bit registers storing the data item number of up to three "specified" data items to be read out or that are operands in an arithmetic operation. A comparator is used with the word position counter to test sequentially the three registers to determine when a specified item is being scanned.

An important duty of the synchronizer is to stop the cell at the end of an instruction. As mentioned before, each instruction ends in a distinct way. There is a 4-bit op-code register associated with a reserved controller address storing the code of the current instruction plus the op-code decoder. The S-counter constantly gets incremented every time a satisfied tuple is found. Typically, a "satisfied tuple" means a tuple satisfying the qualification; but this is not always true. In particular, Insert and Space-Count look for vacant tuples and Create for spaces being large enough to define a tuple. Thus, after Space-Count and Create, the S-counter indicates the number of vacant spaces on the track;

3.5

after Insert it indicates the number of new tuples just inserted. Due to the finite size of the I/O buffer, only a limited number of tuples can be read/inserted per pass. This number must be supplied to the limit register. This register is constantly compared with the S-counter to determine when enough satisfied tuples have been processed so that the instruction can be terminated (for Insert and Read only). Other instructions except Space-Count terminate when the logical end of the track is reached. The logical end is indicated by a vacant tuple bearing a mark (TKE) on its 6th and 7th bits. If the whole track is used, no logical end exists and all instructions terminate when the physical end of the track is reached.

Finally, there are several single-bit registers that sample the value of the mark bits that are required for the query analyzer.

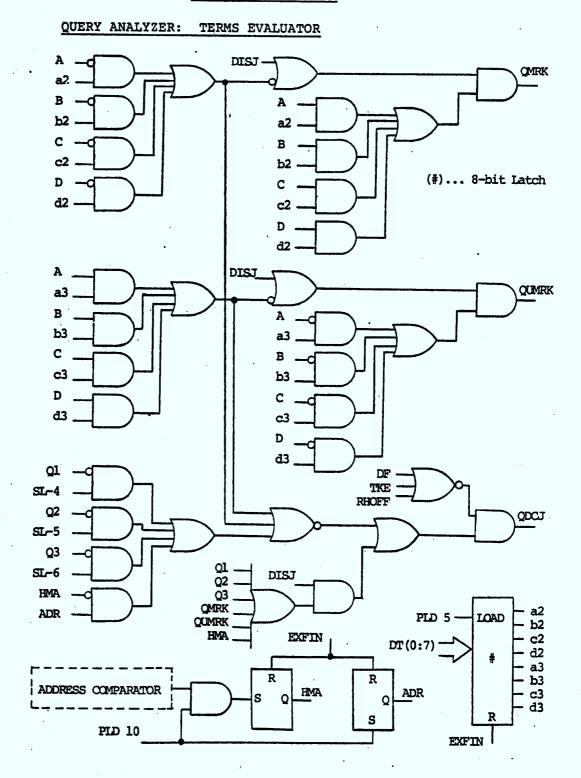

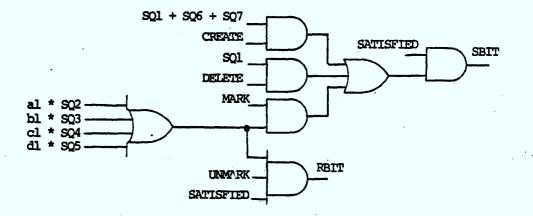

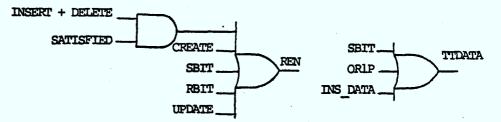

Ouery Analyzer:

This is the heart of a cell and is the only unit that remains essentially unchanged from RAP.1. It determines whether a tuple satisfies the qualification. A query list has one of two forms: either disjunctive or conjunctive. A tuple qualifies if either no term is false (conjunctive form) or at least one term is true (disjunctive form). RAP.3 in addition allows the comparison of two data items of a same tuple as well as other forms of qualification.

The QUERY ANALYZER has two parts: the terms evaluator and three identical data item comparator units. Each comparator unit has an 8-bit register to store the item number of the relevant item a tapped 32-bit shift register for the externally supplied constant, a 4-bit register which indicates the selection of the unit and the symbols (<, =, >) of the comparison and a serial comparator. In operation, a comparator is constantly used to compare the item number with the contents of the word position counter to signal the scanning of the selected item. When this happens, the constant is rotated and compared with data read from the track. By the end of the selected item, the serial comparator knows the truth value of the simple condition of the query list covering this data item.

3.5

The terms evaluator has a multiple single bit register to store the form of the query list as well as the criteria concerning mark bits. It also has a small logic to determine, from the rest of the query analyzer, if the current tuple qualifies.

RAP. 3 would not use shift registers to store constants (comparand in the comparator units and operands in the arithmetic unit). They are stored in a RAM for two reasons. First, long and tapped shift resisters are expensive. Second, there would be no need for a mechanism to rotate the registers. The pointer for this RAM is the contents of the word length counter.

I/O Buffer:

This unit is of prime importance to decouple a cell from the controller for data retrieval and insertion. The controller empties or fills up, at its convenience, the I/O buffer of each cell which loads or unloads its buffer whenever it can. It is not known what is the optimized size for the buffer, but the current prototype cells have a 1K x 16 RAM. Perhaps a size four times larger would be more suitable.

For data insertion, new tuples must be preloaded in the buffer. After the cell is initiated to run, it will look for vacant spaces which are marked at the 1st bit. When one is found, the cell erases all mark bits. New marks will be generated if the mark option is used. The data is pulled from the buffer. A 16-bit parallel-to-serial register is used to send one bit at a time to the update control unit for writing on the track. The cell stops when enough tuples have been inserted. If there are not enough spaces, the cell stops at the physical end of its track.

For data retrieval, data from the read head is shifted in a 16-bit serial-toparallel converter to be loaded into the buffer either once per every 16 bits of a item or once per every 8-bit item. If the tuple is found not to qualify, the cell back tracks its buffer pointer so that, in the end, the buffer holds only the selected items of qualified tuples. The cell stops when either enough qualified

# 3. IMPLEMENTATION

tuples have been read or when the logical or physical end is met. In RAP.3, since the read phase is allowed only when necessary, the retrieval procedure is different. The cell only reads the selected items of a tuple after it has been found to qualify.

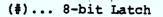

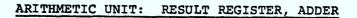

#### Arithmetic Unit:

This is the only unit that is not vital to the operation of the rest of the cell. It is necessary only for supporting arithmetic instructions (namely Add, Sub, Sum, Max, Min) and can be removed if they are not required. It contains three tapped shift registers to store operands and results. For lack of space, the prototypes were built to support 8-bit and 16-bit operands only. It is trivial to expand these registers for longer fields. As mentioned in query analyzer, RAP.3 supports much longer domains where a RAM would be more suitable than shift registers. A serial comparator similar to the one of the item - comparator units helps to implement Max and Min. A serial adder is used for Add, Sub, and Sum.

In operation, if the instruction involves only one item, the arithmetic is immediately performed while that item is being scanned. If two items are involved, the first one is stored in one of the shift registers until the second one is scanned. In Add, Sub, and Replace, the result is immediately stored in the result register to be written in the proper space later (i.e., during the next tuple-time) if the current tuple qualifies. For Max, Min and Sum, the result is transferred to the result register only after the tuple has been found to quality (i.e., in next tuple-time). It is up to the controller to probe the result register after the cell stops. Multiply and Divide are not implemented directly in RAP. 2 cells because of timing conflicts in the bit serial logic.

#### Update Control:

This is the smallest unit of a cell. It has a register to store information concerning the Mark and Reset option. It takes care of the marking and resetting of mark bits as well as the writing of new data supplied by the I/O buffer for Insert

3.5

# 3. IMPLEMENTATION

or by the arithmetic unit for Add, Sub and Replace. It also erases the track for Create or only selected tuples for Delite. It also erases the track for Create or only selected tuples for Delite.

### Output Multiplexer:

This is logically the simplest unit. Appropriate registers are connected to various bus drivers which are enabled by signals from the cell interface decoded from the control bus.

For most registers, it is the duty of the controller to assure that only one cell at a time is in the readable state otherwise information on the data bus is meaningless. The only exception is the reading of the status which is meaningful in an "OR"form.

### <u>CCD Memories</u>:

This unit is built in a very straightforward manner. Due to physical limitations, the 1-megabit drum occupies three identical boards. Each board contains all necessary drivers and 20 Intel 2416 CCD chips which are arranged in an X-Y matrix of 4 x 5. This arrangement is necessary to reduce the number of drivers. It is possible because the CS and CE inputs of the chips are internally "and-ed" together. Two different kinds of drivers are used: Intel's 5244 chips are used for shift inputs and Intel's 3245 chips are for addressing, these drivers are quite good but there is a small problem of mismatched speeds. The former type is about 70 ns slower and some compensation must therefore be made. Currently, all the CCD chips are driven at a same frequency. If the memory size is expanded much larger, it makes sense to use two different rates. Only one or two chips at a time are driven at the fastest rate and the rest at the minimum frequency to conserve power.

## 3.6 <u>Some Statistics</u>

Each cell (including the 1-megabit track) requires about 9 amperes at 5 volts, is spread over 13 boards and employs 412 IC packages (218 SSI + 117 MSI + 77 LSI). For each additional 1 megabit extension, 96 IC's are needed.

# 3.5

# 4. DBMS UTILIZATION OF RAP

### 4. DBMS UTILIZATION OF RAP

In this section we address four issues relating to total data base management system architecture and various uses of RAP as a systems component. First we consider systems approaches for data bases larger than RAP capacity. Next we show how RAP can be programmed to support multiple views of data. Last we consider RAP's applicability to protection, security, and integrity.

4.

### 4.1 System Organization

One might conceive of the day in which microprocessor logic and memory becomes so inexpensive that all secondary memories would have RAP-like processing capabilities. However, the first generations of commercial RAPs would have capacity limitations relative to the total data base storage requirements. In this case, all existing data base installations have significant capital already committed to conventional secondary memories.

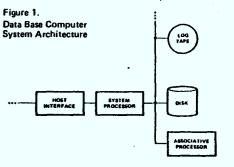

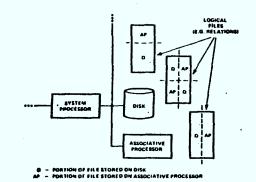

A complete cost effective system would therefore consist of a triad of component types: a front-end general purpose computer to interface with users and provide operating system and language processing functions, a RAP device used as a peripheral or back-end processor/memory, and one or more conventional secondary memories. The entire triad can also be considered as a back-end <u>data base computer</u> for further levels of front-end systems (11). We will briefly outline three approaches to the DBMS organization that exploit this organization at varying levels of complexity.

It is important to note that some of the problems alluded to in the section on limitations of conventional approaches are reintroduced with this approach. However, because the complex situations are handled by RAP, we would expect that an overall improvement in performance and a reduction in administration complexity would still be achieved.

## 4.1.1 RAP as an Access Path Processor

As stated before access paths are indexing methods used in conjunction with conventiona: DBMS implementation to speed the searching of large data bases. Two major types of access paths will be considered: inverted lists and links. An inverted list is a data

structure which extracts the values that occur in the data base and associates with each unique value the physical or relative addresses of the records that contain that value. The records which satisfy a boolean selection criterion of simple item conditions of the form "<item> = <value>" can be found by processing the inverted lists rather than searching the data base directly. The boolean AND operator between two conditions is satisfied by the intersection of the inverted lists addresses associated with the item <values>. The OR operator is satisfied by the merge or union of the address lists. The NOT operator can be implemented by the relative complement of the list's address. Arbitrary boolean expressions can be parsed into a trees and processed two or more lists at a time producing intermediate lists until the final list contains the addressed of the qualifying records.

It is possible to create an inverted list on several different items within a file at the same time. This is done by associating the addresses of the records in which a particular combination of values occur where each value is from a different item. This type of inverted list is called a <u>multi-key inverted list</u>. In this case a conjunctive boolean qualification has already been formed as part of the list structure. The records satisfying a general boolean qualification can be found by first placing the qualification into disjunction normal form and since there exists a list for each conjunction, the qualifying records can be computed by just merging the lists to satisfy the disjunction.

In dynamic update situations where the inverted lists are stored on conventional devices, the single values inverted lists are preferred because they are easier to maintain. In static non-update environments, the multi-key inversion gives better retrieval performance.

A link is a data structure which records instances of pairwise inter-record connections of records of different type. It is often used to record the existence of a particular relationship between the records and provides a fast access path for locating and accessing the linked record given the other record. Such structures are used to optimize <u>join</u> operations in relational data bases system or the implementation of <u>sets</u> in CODASYL Systems (10).

4.1.1

**Processing Inversions:**

Inversions can easily be stored in RAP relational format. For a single item inversion we could create a RAP relation for each item inverted. There will be two entries in the records -- one for the value and one for the address pointer. For multi-key inversions one would create a RAP relation containing an data item for each value and one for the address. In cases where the same value(s) occur at many addresses, we must duplicate the values for each address.

Two things affect the efficiency of RAP for processing inversions: the size of the record occurrences and the type of processing required. In the single inversion case, each record has only two items - a value and an address. Because a gap is sometimes required between each record, the utilization of space would not be very efficient (this is eliminated in RAP, 3). Secondly, the processing of single valued inverted lists required intersections or unions of data items between relations on RAP. This requires cross marking operations which are among the slower multirevolution execution instructions for large volumes of qualified RAP records.

The above processing is to be distinguished from the union and intersection of items in the same relation which is very fast on RAP. This fact can be exploited to solve both the space and processing problems by utilizing one multi-key inversion for each data base file. The storage of more values per RAP relation creates larger and fewer RAP records. Also the clustering of lists into one RAP relation representation of the multi-key inversion creates a structure efficient for RAP processing. As stated before all conjunctive queries are preprocessed by construction of the list. Conjunctive queries involving only some of the inverted items are processed naturally by the RAP marking and qualification logic. Disjunctions are then simply processed by reading the address items of the marked records. However, it should

# 4. DBMS UTILIZAITON OF RAP

4.1.1

be noticed that the list of address is not guaranteed to be in sorted order unless the storage or reading process is controlled.

### Processing Links:

A simple RAP relation for implementing links requires a pair of items. Each RAP record records the addresses of the pair of linked data base records where the first address item always points to one data base file and the second points to the other. By knowing the data base address of a record one can mark the RAP linkage records using the address as a condition on one of the items. All the addresses of data base records linked to first can be readily read.

In many cases the link would have been established from values already existing in the data base. These values could be added to the RAP linkage structure as extra items. The values can then be used to aid in updating the link on RAP when the data base is modified.

### 4.1.2 Data Base Partitioning

The major problem with the indexing approach is that the index data stored on RAP are duplicates of data on disk. Instead we can partition the data base files both horizontally, i.e. placing certain records on RAP and other on disk, and/or vertically placing clusters of data items on one device or the other. Because no duplication takes place, the technique is called <u>device partitioning</u>. Extra data items such as record id's may be required to link corresponding partitions.

This particular approach attempts to exploit the notion that not all data in a data base, at a particular point in time, requires the same processing capabilities. Data can be categorized by the system according to its usage characteristics and placed on the conventional secondary memories or RAP depending on processing requirements that best fit the data.

The implementation of such a system should include mechanisms for both user controlled and automatic migration of data between the various devices as usage of the

# 4. DBMS UTILIZATION OF RAP

45

data changes. Research into algorithms that exploit data base device partitioning

is under way at the University of Toronto.

A request would be processed by decomposing it into RAP and Disk subqueries and first executing the RAP subqueries. Access would then be made to disk only if the request can not be entirely serviced by RAP. In this case the response from the RAP subquery would be used to minimize the search over the disks portion.

### 4.1.3 Paging and Virtual Memory

This approach mimics the techniques of paging operating systems to provide a virtual associative address space for a RAP device. This requres all the data in the data base to be stored according to RAP memory format. The data is then divided into pages the size of one RAP cell. All data base queries are translated into RAP processing statements. Before execution, each query is directed through a software monitor executing on the front-end computer. The principal tasks of the monitor are to maintain a table that gives the location of the pages for each data base file, analyze which pages are required to execute a query, and then page the necessary data between the conventional secondary storage devices and the RAP processor. The query is then passed to the RAP processor for execution. It would be optimum to have a direct path between the secondary storage devices and RAP so that pages would not have to be transferred through the front-end.

As opposed to the indexed or partitioned approaches, all queries will be executed entirely within the RAP processor. This requires that all the data for a query be small enough to fit on the RAP device at any particular time.