# TECHNIQUES FOR IMPROVING THE RELIABILITY OF DATA TRANSMISSION OVER THE HF RADIO CHANNEL

FINAL REPORT /

Ъу

Alberto Leon-Garcia

Department of Electrical Engineering

University of Toronto

Toronto, Ontario

31 March, 1984

prepared for

Department of Communications, Canada under Contract OST83-00101

91 C655 L455 1984

P91 C655 L455 1984 DD 4589466 DL 4589533

# 1.0 INTRODUCTION

This report presents the results of several investigations concerning the application of Viterbi decoding to transmission over the Syncompex binary FSK modem. is organized as follows. Section 2 discusses the implementation of a real-time Viterbi decoder for use with the Syn-The organization of the software that implements compex modem. the Viterbi decoder is discussed in detail and documentation is included in Appendices. Speed and memory requirements are also discussed. Section 3 considers several performance issues of Viterbi decoding. Experimental and simulation results are presented for the performance of the decoder for various settings of decoder parameters. Simulation results are also presented for the performance of Viterbi decoding when combined with internal interleaving. Finally Section 4 considers the extension of the present transmission protocol to a system that utilizes a multi-FSK signal format. present transmission protocol is analyzed to establish a basis for the evaluation of the other protocols. mission protocol discussed by Lin is analyzed in detail in the context of Viterbi decoding. Methods are developed for evaluating the throughput performance. This protocol is then compared to selective repeat ARQ and to selective repeat ARQ with code diversity. A new adaptive protocol is proposed that achieves the performance of the Lin protocol while requiring a simpler implementation.

> Industry Canada Library Queen

방반 2 1 1998

Industrie Canada Bibliothèque Queen

### 2.0 REAL-TIME VITERBI DECODER

The first objective of the project was the implementation of a real-time Viterbi decoder for use with code-diversity transmission on the Syncompex modem. This allowed us to verify the attainable decoding speeds and enabled us to undertake more comprehensive experimental studies on the performance of Viterbi decoding as various system parameters are varied. This chapter describes the hardware and software developed to accomplish these goals.

The chapter is organized as follows. Section 2.1 gives an overview of the system. Section 2.2 describes the approach used in the software implementation of the Viterbi decoder. Section 2.3 describes the organization of the system software including brief descriptions of the main modules. Timing and memory requirements are also discussed. The chapter concentrates on the main ideas only but details are included in the appendices.

### 2.1 SYSTEM OVERVIEW

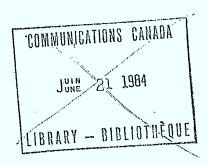

Figure 1 summarizes the signal processing required to obtain sequence of discrete-channel outputs suitable for Viterbi decoding. This processing is done by what we will refer to as the ADC board. The modem provides three analog output signals. outputs of Chips #1 and #2 are the noncoherently-demodulated baseband signals corresponding to the binary sequences produced by the convolutional encoding at the transmitter. signals have a baud rate of 75 symbols per second. Chip provides a clock signal recovered from the eye signals using selection diversity. This clock signal is offset with respect to the eye-signal baud period so a delay is introduced to obtain a clock signal suitable for controlling the integrate-and-dump operations. The integrator outputs are sampled at the appropriate instants and the digitized samples are then passed to the Viterbi decoder.

The Viterbi decoder is implemented in software using a Motorola 6809 microprocessor. The decoder software is written so that various system parameters, inclu the code, the channel-output quantization, and the decision depth, can be varied. The decoder outputs the estimates of the information sequence in a form suitable for analysis by a data error analyzer. The 6809 microprocessor is also programmed to process these outputs in order to compile error statistics. These statistics are displayed on a computer terminal as the real-time decoding takes place.

FIGURE 1

#### 2.2 DECODER IMPLEMENTATION APPROACH

In this section we will first discuss the Viterbi decoding algorithm in general and then we will outline how it was implemented in software.

The task of the Viterbi decoder is to estimate the information sequence that was fed into the encoder at the transmitter. This is equivalent to finding the sequence of encoder states that produces the encoded sequence that is closest to the observed channel output sequence according to some metric. The decoder stores two entries for each possible encoder state. The first entry contains the minimum-distance sequence of states leading to the given state up to the given time instant. We will refer to this entry as the "path history" of the given state. The second entry contains the distance of the corresponding encoded sequences to the observed channel output sequence. We will refer to this entry as the "state metric."

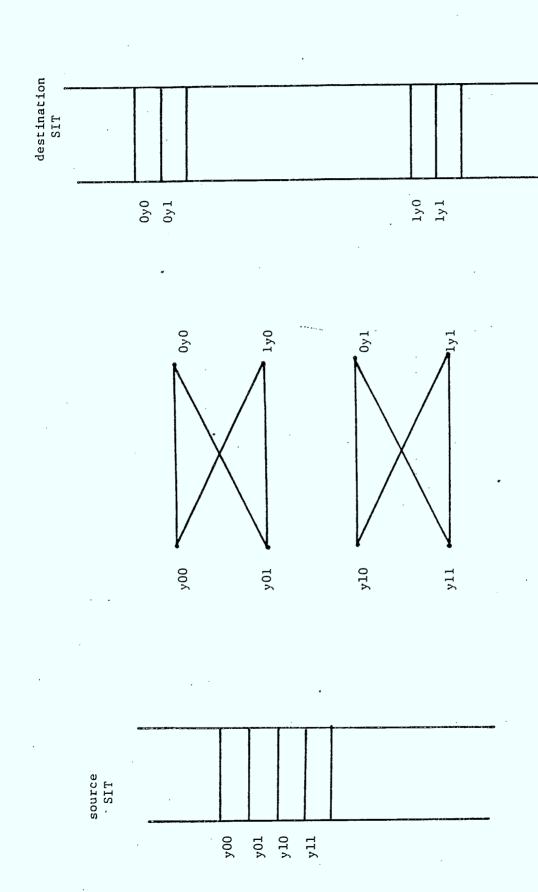

Each time a channel output pair is passed to the decoder, the entries for all possible states, henceforth referred to as the State Information Tables, are updated using the following sequence of steps (see Figure 2):

## 1. Branch Metric Computation

The distances ("branch metrics") of the new channel-output pair with respect to the four possible encoder outputs, namely 00,01,10,11, need to be found. This can be done by computation or by table-lookup depending on the complexity of the metric used. The four branch metrics obtained in this step will be used in the subsequent steps.

# 2. Add, Compare, Select (ACS)

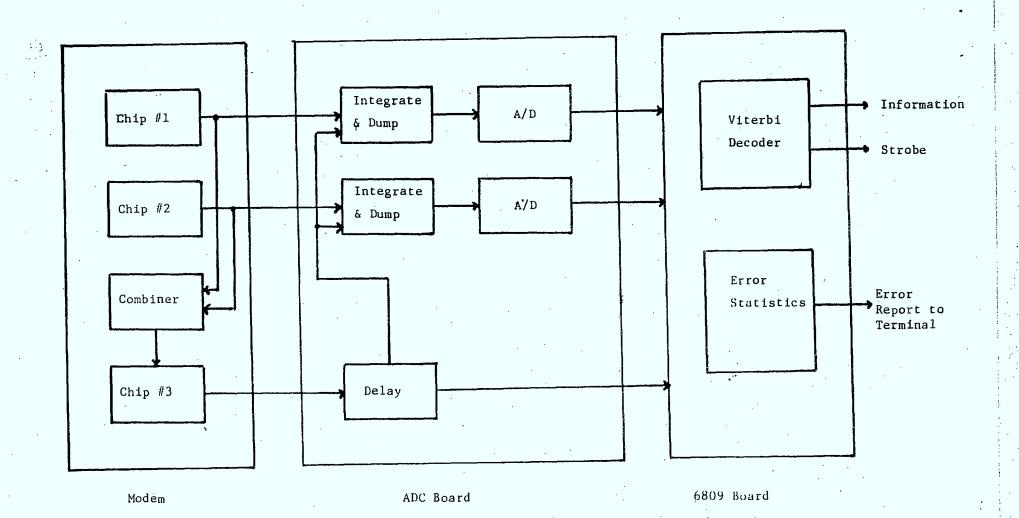

Each encoder state has only two possible ancestor states that can immediately precede it. The best new sequence leading to a given state is thus found by comparing these two ancestor states. The state metric of each ancestor state is added to the branch metric corresponding to the corresponding state transition; the two resulting metrics are compared; and the ancestor state with the smaller metric is selected. The best new sequ for the given state is found by concatenating the selected ancestor state to the path history of the selected ancestor state. The new state metric of the given state is given by the smaller of the two metrics used in the compare step. The ACS procedure is carried out for each of the possible encoder states.

Upon completion of the above steps, the State Information Tables will be completely updated and the decoder will be ready for another channel output pair.

The above two steps form the heart of the Viterbi decoding algorithm. Two additional steps are required because of

| Branch | Branch Metric |

|--------|---------------|

| 00     | metric        |

| 01     | metric        |

| 10     | metric        |

| 11     | metric        |

Branch Metric Table

metric(A) + branch metric(A)  $\geqslant$  metric(B) + branch metric(B)

FIGURE 2

FIGURE 3

# 3. Truncation of Path History

The length of the path histories need to be kept bounded in order to keep the decoding delay bounded and to keep the memory requirements reasonable. Periodically it becomes necessary to make a firm decision on the estimate for oldest segment of past history currently stored in order to free up memory. The optimum procedure involves finding the state with the smallest state metric at that time instant and the required segment of past history is then set to the corresponding segment in the "winning" state's path history entry. The memory space allotted to storing this segment of path history then becomes available for storing new segments of path history. The amount of time "wasted" in searching for the best metric can be kept proportionally small by making each segment consist of several information above view also suggests the partitioning and handling the path history as a ring buffer with each unit of path history equal to one segment. By selecting these segments be close to one byte in length, the need to perform bit manipulation is completely circumvented. This is a very important consideration in software implementations.

# 4. Scaling of State Metrics

As decoding proceeds the range of values occupied by the state metrics will steadily increase. In order to keep these values within the range that can be assumed within the finite precision of the machine, it becomes necessary to periodically reset the metric values so that they fall within the desired range. The rate at which the state metric values increase is proportional to the number of bits used in the branch metric calculations. If the number of bits is not too large, the state metrics will need rescaling very infrequently.

From the above discussion it is clear that the principal factor in determining the attainable decoding speed is the at of time required to carry out the ACS operation. We now examine this operation more closely.

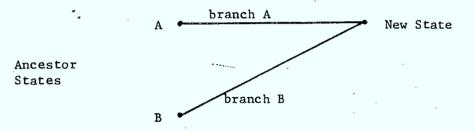

Let the state of the encoder be given by the binary representation of the contents of its shift register with the newest bit equal to the most significant bit. If the constraint length is v, the state is given by a v-1 bit binary number. To make the discussion concrete, consider the case v=7. The number of states is then 2\*\*6=64. Consider a destination state in the range 0 to 31, that is, a state with binary representation 0x, where x is 5 bit number. (See figure 3.) The source states for this destination state are x0 and x1. Furthermore note that destination state 1x has the same set of source states. Since the ACS opera-

tion for both of these destinations involve the same state metrics and state histories it is efficient to process the pair of destination states together.

Note that the source states in figure 3 have consecutive indices. Thus if the state metrics and path histories are arranged according to the numerical value of the state, the information required by the ACS operation of various states is obtained by working down the State Information Table.

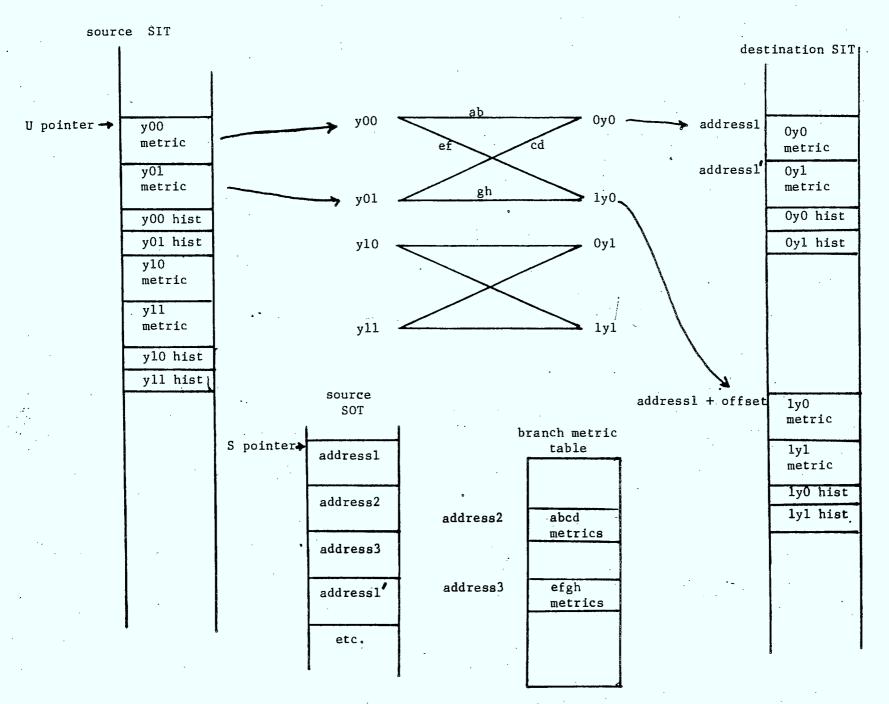

Before discussing how the State Information Table was organized we need one further property. Consider a destination state with representation 0y0, where y is a 4 bit number. Note that the state metric and path information of 0y0 and 0y1 will be required together when the next channel output is processed. It would thus be convenient to handle the ACS operations of destination states 0y0 and 0y1 at about the same time so that the results of the operations can be stored together. This suggests handling the ACS operations in groups of four as shown in figure 4. This is how the ACS operation was implemented in our project and it accounts for how the State Information Table was formed.

State Information Table contains two entries for The first entry is a two-byte word specifying the state. state The second entry is a one-byte word of recent history corresponding to one segment of path history. history is stored in a separate ring buffer which is updated when segment of recent history has accumulated. The information for pairs of source states is bundled together as shown in figure 4. Two State Information Tables were These tables alternate between being sources and destinations of information generated during the ACS operations. By using in-place storage techniques it is possible to function with only We found however that State Information Table. approach implied memory requirements implementation of this elsewhere larger than that of the Table itself.

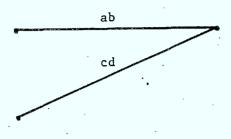

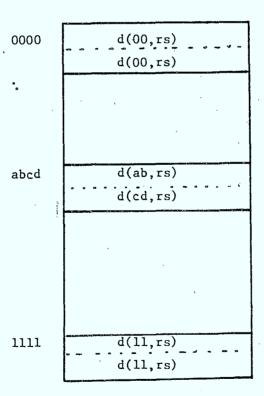

In omplementation of the Viterbi decoder, the ACS operais driven by a State Organization Table that provides locations where information is to be found or addresses of Before explaining the State Organization Table we consider how the branch metric calculations are carried and cd be the two branch labels associated with the operation of some given destination state as shown in figure branch label can take on 4 possible values so there are a total of 16 possible pairs of branch labels. Let rs be the pair output symbols that are to be processed. channel for the given destination state will then require branch metrics d(ab,rs) and d(cd,rs), where d(.,.) denotes metric function. The branch metric calculations are handled as As soon as the channel outputs rs are read in, all 16 possible pairs of branch metric values are computed and stored in some fixed locations where they can be readily accessed by the ACS operations.

FIGURE 4

Branch Metric Table

soon as the branch metric calculations have been completed and stored, the ACS operation for the states is initiated. The ACS operation for each state will require two sets of entries from a source State Information Table (SIT) and will generate two sets of entries to be stored in the destination SIT. The function of the State Organization Table (SOT) is to provide the addresses memory locations where the appropriate branch metric labels are to be found and where the destination state information to be stored. The State Organization Table consists of pairs groups of 3 two-byte words. The first group provides the addresses required by the ACS operation of states of the form 0y0 and The second group provides the address information states of the form Oyl and 1yl. Two State Organization Tables are required since the addresses involved will depend on which is acting as the source and which as the destination. SOT structure and the flow of information is shown in figure 6.

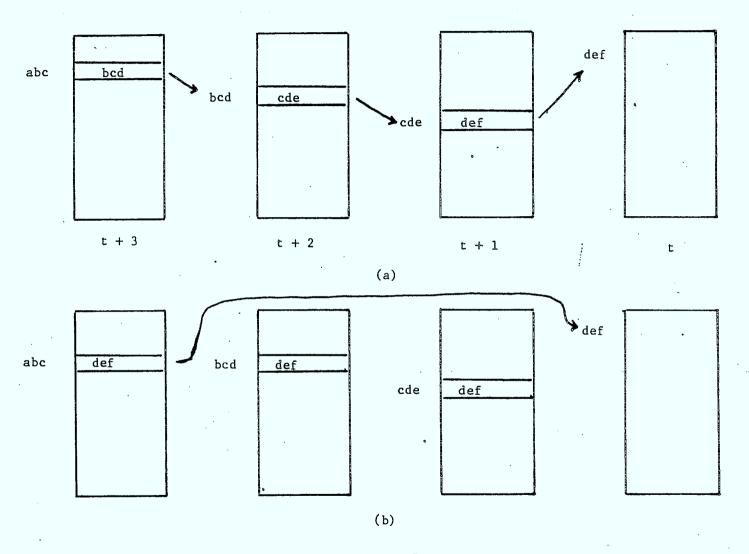

As indicated above the decoding of channel output symbols proceeds until one segment of recent history has accumulated. then necessary to output the oldest segment of history order to free up enough memory to store the next segment of path We now explain how this is done. history. It can be seen from figure 3 that the destination state and the source state have all one bit in common in their binary representations. conventional approach to history updating the identity of the previous "winning" ancestor state is stuffed into the path history of a given destination state. This is shown in figure 7a for a constraint length 4 code. When the time comes to output segments of history, a search is carried out for the state with the smallest metric, say state abc in the example, and then it is necessary to "trace back" to identify the segment that is to be output. The trace back is done by using the contents of the path history registers: the contents of abc point back to location which in turn points back to location cde, and so o

Now consider the following different procedure. At time t+1 we proceed as before and stuff the identity of the "winning" ancestor state into a recent path history register. However for the subsequent time instants up to t+v-1, we stuff the contents of the recent path history register of the the "winning" ancestor state. An example is shown in figure 7b. Note that figures 7a and 7b give the same information, namely the best sequence leading to abc has the three most recent bits def. In tracing back, however, the second approach can jump immediately from abc to location def v-1 time units earlier. The trace back operation

can thus be carried out much more quickly.

Once the trace back operation has been completed and a segment of v-1 bits has been selected for output, the contents of the recent path history entries in the State Information Table are transferred to the newly freed memory locations in the ring buffer containing the long term path history as shown in figure 8. The decoder is then ready to undertake another cycle of processing another segment of v-1 channel output pairs.

FIGURE 6

FIGURE 7

#### 2.3 SOFTWARE ORGANIZATION

The system software consists of two parts. One part implements the real-time Viterbi decoder. The second part carries out the error checking functions as well as the compilation of error statistics.

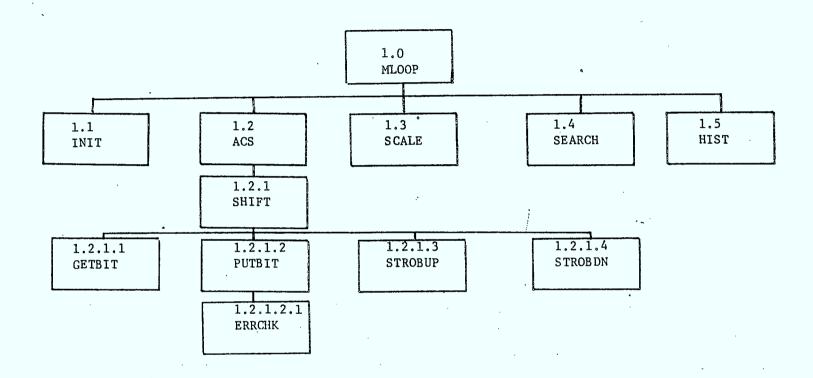

Figure 8 shows the hierarchy of software modules responsible for the real-time Viterbi decoding. The main program begins by calling the subroutine INIT to initialize program variables and storage areas, and it then enters a loop that defines one decoding cycle. One decoding cycle consists of the following subroutine calls:

Call ACS1

Call SCALE

Call ACS2

Call ACS1

Call ACS2

Call ACS1

Call ACS1

Call ACS2

Call ACS1

Call ACS2

Call ACS2

The above decoding cycle assumes a path history segment of 6 bits corresponding to a constraint length 7 code. The modules ACS1 and ACS2 implement the ACS operations. They differ only in which State Information Table and State Organization Table act source and destination for the ACS operations. The module SCALE makes sure that the values of the state metrics remain within the that can be handled. The module SEARCH identifies the with the smallest path metric and the module HIST the traceback operation and the transfer path history to long term path history. The module HIST returns the segment of 6 information bits that are selected for output the traceback operation. In order to produce a nearly synchronous output of information bits, these bits are output one at a time during the subsequent 6 ACS Subroutine calls.

The ACS subroutine begins by calling the module SHIFT. module begins by calling PUTBIT and STROBUP in order to output an information bit and set the strobe up in order to indicate valid data to the data error analyzer. Note that PUTBIT calls invokes the error checking and error compilation software SHIFT then calls GETBIT which reads the channel outputs modules. from the ADC board and then maps these vs through the table #MAP. The choice of entries in this table allows us to nonlinear quantization in addition to the usual quantization. SHIFT then calculates the 16 possible branch meand stores them in the direct page area starting tric entries the address label T0000. Finally SHIFT calls STROBDN to lower the strobe while the data is still valid. Upon return from SHIFT the ACS module proceeds to carry out the ACS operation for the states in groups of four as indicated in the previous section.

. FIGURE 8

The number of instruction cycles required to carry out the above modules is given by:

```

ACS 371 + 289 x 2**(v-3)

SEARCH 31 + 55 x 2**(v-2)

HIST 138 + 32 x 2**(v-2)

SCALE 23 + 46 x 2**(v-2)

```

and the number required by one decoding cycle is

```

(v-1) x ACS + SEARCH + HIST + SCALE.

```

The number of instruction cycles required by a decoding cycle for constraint length 7 code is 34,418 which is equal to 35.9 for the .96 MHz clock used in the current implementation. At the information rate of 75 bps, the 6 bits of a decoding cycle are produced in 80 ms. Thus for a constraint length 7 the microprocessor is idle more than 50% of the time. (This was observed experimentally by observing the strobe signal on an oscilloscope.) If the constraint length is increased to 8, number of cycles increases to 76,037 and the time to 79.2 The 7 information bits are produced in 93.3 ms, so the microprocessor is now busy decoding about 85% of the time.

An upper bound on the information rate that can be handled with this software can be obtained by assuming that modifications are made so that SEARCH, HIST, and SCALE become negligible. For a constraint length 7 code, the maximum information rate that can be handled is then 192 bps. For a constraint length 8 code the maximum is 100 bps.

A real-time dedicated microprocessor implementation of the decoding algorithm would have the following memory requirements. The principal components of ROM memory are the program, the two State Organization Tables, and the quantization map. The respective memory requirements are 600 bytes,  $2\times3\times2**(v-1)$  bytes, and 2\*\*(v-1) bytes. For a constraint length 8 code, this adds up to approximately 1.5 kbytes. The principal components of RAM memory are the two State Information Tables, and the path history ring buffer. The respective memory requirements are  $2\times3\times2**(v-1)$  and  $8\times2**(v-1)$ , where a history depth of 8 segments has been assumed. This adds up to 1.8 kby

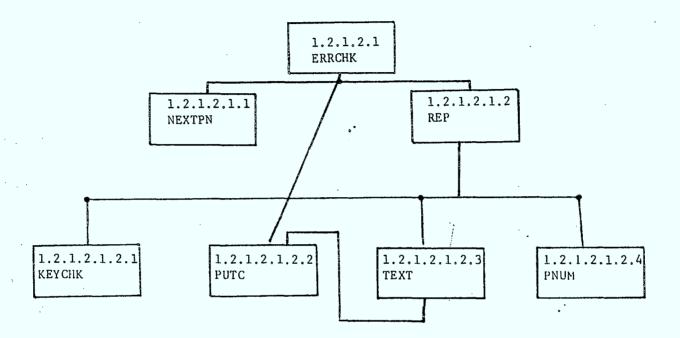

Figure 9 shows the module hierarchy for the error checking and error compilation software. When synchronized to the inforsequence, ERRCHK takes the information bit that has just output and compares it to that predicted by the NEXTPN which is designed to emulate the PN sequence generator that was used at the transmitter. The bit count and the bit error counts are then tallied. Statistics are compiled in blocks of length #BLOCKLEN. At the end of each block, character report is output to the terminal using module PUTC. the end of each block, the number of bit errors is compared If the number of errors is greater than this threshold, -#ERRLIM. resynchronization procedures are begun in the next block by

FIGURE 9

resetting the contents of the PN sequence generator in NEXTPN to that of the last v-1 information bit estimates.

The module REP implements the printing of the block error reports and counts on the terminal with text explanations and decimal output.

Appendix A contains the module descriptions and Appendix B contains the assembly language code along with detailed comments.

#### 3.0 VITERBI DECODER PERFORMANCE ISSUES

In this section we present results of two investigations of Viterbi decoder performance. The first investigation deals with the dependence of decoder performance on the values of several algorithm parameter values. Experimental and simulation results are presented for decoders with different number of quantization levels, different history depth values, and with linear and nonlinear quantization. The second investigation considers the performance of Viterbi decoder performance when combined with internal interleaving. Simulation results are presented for systems of different interleaving depths and for channels with different burst error characteristics. We begin the section by describing the simulation model used in our investigations.

## 3.1 SIMULATION MODEL

Simulation programs were written to provide a means for quickly and easily testing various Viterbi decoder configurations as well as for simulating various channel transmission conditions. A Viterbi decoder program was written in BASIC to run on the IBM PC. The program completely parallels the implementation of the M6809 real-time decoder in order to allow the simulation of changes in the real-time system. The details of the program therefore do not need to be repeated here.

A second program was written to simulate bursty channel conditions on dual parallel FSK channels. The model simulates independent fading on the two channels was well as simultaneous (flat) fading on the channels. At any given time instant each channel is in one of three states: Good, Bad, or Flat. At any given time instant the channel pair can be in one of five states:

- 0 Good-Good

- 1 Good-Bad

- 2 Bad-Good

- 3 Bad-Bad

- 4 Flat-Flat

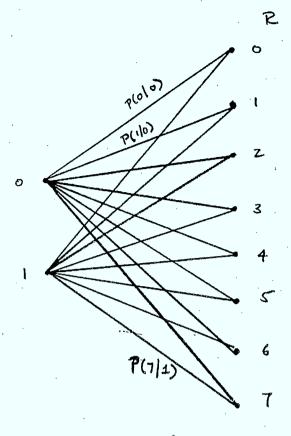

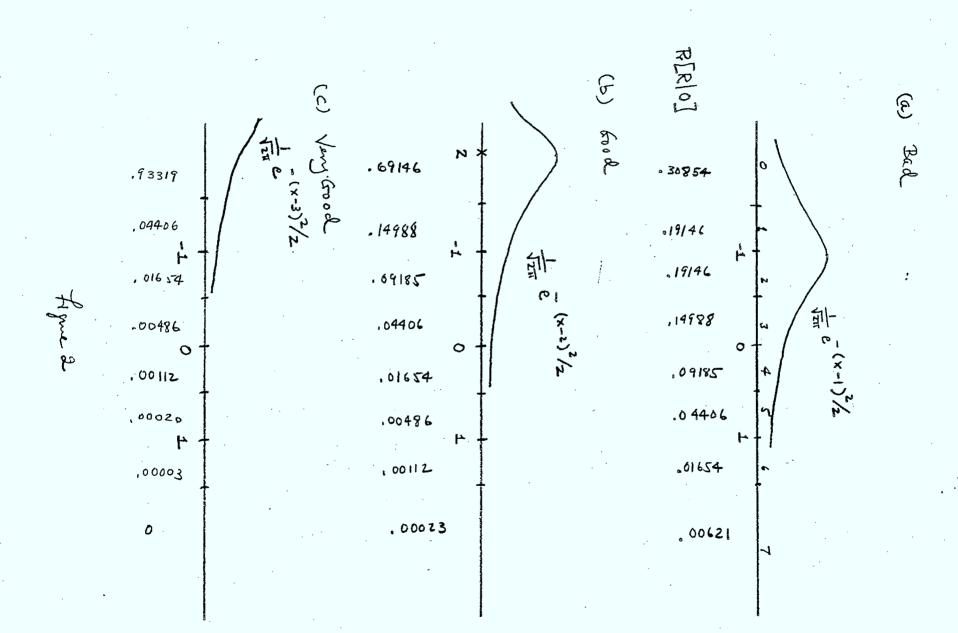

While a channel is in the good state, it randomly generates octal output symbols R for each binary input b according to the transition probability shown in Figure 1. The octal output is intended to represent the output of a 3-bit quantizer. Similarly when a channel is in state bad or flat, it generates outputs according to predesignated transition probabilities.

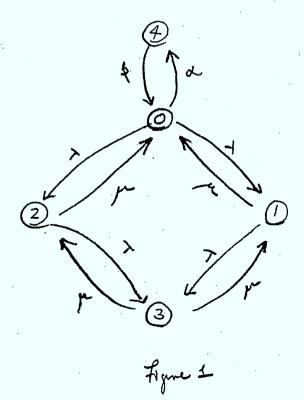

The time evolution of the channel state pair follows a continous-time Markov chain with transition-rate diagram shown in Figure 2. Here  $\lambda$  is the rate at which an individual channel goes from the good state to the bad state, and  $\mu$  is the transition rate in the opposite direction;  $\alpha$  is the rate at which the channel state pair goes jointly from the good-good state to the flat state. The simulation program generates random, exponentially distributed holding times X (in bits) for each state, and then rounds them up to the next integer greater than or equal to X. The next state is selected according to the state transition probabilities that correspond to the transition-rate diagram.

All the simulations discussed in this report simulated independent fading only. The bad state was always represented by the 3-bit quantized Gaussian channel shown in Figure 2a. This (single) channel has a raw bit error rate of .159 and a 128-bit block error rate of essentially 1. The good channel was chosen to be either that shown in Figure 2b or that in 2c. The channel in 2b, hereafter called the good channel, has a raw bit error rate of .023 and a block error rate of 94.7%. The channel in 2c, hereafter called the very good channel, has corresponding rates of .00135 and 15.9% respectively. It should be emphasized that the error rates for these channels are relatively high because they correspond to single channels; when the two channels are combined the performance improves considerably.

The channel parameters used in a given simulation will be specified by prefixing each state with its mean holding time. Thus 250G/50B denotes a channel in which the subchannels fade independently with the good state having a mean holding time of 250 bits, and the bad state a mean holding time of 50 bits. The mean holding time of a state pair is given by the reciprocal of the sum of the rates out of the state pair. Thus the mean holding time of the bad-bad state is 25 bits and that of the good-good state 125 bits.

## 3.2 EFFECT OF DECODER PARAMETERS ON DECODER PERFORMANCE

The software of the real-time decoder was written so that the number of quantization levels and the history depth could be changed easily. Instructions for carrying out these changes are included in the documentation. An arbitrary nonlinear quantization scheme can be produced by changing a 64-entry table through which the A/D samples are mapped. The convolutional code can also be changed, but this requires changing the longer state organization tables. Here we will report on the results of experiments that vary the number of quantization bits, the history depth, and the quantization mapping.

-13 -11

The software of the real-time decoder includes modules that implement error counting and reporting functions. block size for block error counts is programmable and was The output of the decoder is arranged in set to be 64 bits. blocks of this size and the number of errors counted. If no errors are found, a dot is printed on the screen and simultaneously stored on floppy disk of an IBM PC running CROSSTALK. If errors are found, the number of errors is compared to a threshold, ERRLIM, which is also programmable. If the threshold is exceeded, a resynchronization operation is initiated in the next block and an 'S' printed. Otherwise the number of errors is printed. The duration of the experiments is also programmable, and the error count is displayed at the end of each experiment. Figure 3 is a sample printout of one of the experiments.

The present system has the following nominal settings: 6-bit quantization, linear mapping, history depth 8, and 133/171 rate 1/2 convolutional code. A series of experiments were conducted where the nominal system was compared to systems in which one of the settings was changed to:

- -- 1-bit quantization

- -- 3-bit quantization

- -- Mu-law mapping

- -- Inverse Mu-law mapping

- -- history depth 4

- -- history depth 6

Each experiment involved changing the software and then demodulating and decoding the (approximately) same segment of tape recorded audio signal corresponding to 1728 blocks of information. To control for fluctuations in the results due to factors other than the change in parameter, the nominal system was interspersed among the other experiments.

Each experiment was run twice. Table 1 shows the results of each experiment. The experiments are listed in the order in which they were carried out because significant variations were observed in the performance of the control (nominal system) experiment. The results are also displayed in Figue 4 where it can be seen that the control experiment varied in error rate from 0.75% to 2.78%. The error rates of all the other experiment except one fell in this range. The one exception was for the system with 1-bit quantization which was clearly inferior. The printout for one of the 1-bit experiments is shown in Figure 5. This printout can be compared to that of Figure 1 which corresponded to the control experiment that had the best performance. Thus the only conclusion that can be made from the experimental results is that 1-bit quantization is significantly inferior to soft decision systems.

The simulation programs were used to investigate the effect

| *<br>*<br>38 | j<br>SS | 1 : | S |   |     |   |          |    |          |     |    |     |   |   | • |   |   |   |   |   |   |   |   |     |   |   |     |     |     |   |     |   |   |   |            |    |   |   |    |   |   |   |   | • |   |    |   |   |   |     |      |     |     |    |   |   |            |   |   |          | -    |

|--------------|---------|-----|---|---|-----|---|----------|----|----------|-----|----|-----|---|---|---|---|---|---|---|---|---|---|---|-----|---|---|-----|-----|-----|---|-----|---|---|---|------------|----|---|---|----|---|---|---|---|---|---|----|---|---|---|-----|------|-----|-----|----|---|---|------------|---|---|----------|------|

| • •          |         |     |   |   |     |   |          |    |          |     |    |     |   |   |   |   |   |   |   |   |   |   |   |     |   |   |     |     |     |   |     |   |   |   |            |    |   |   |    |   |   |   |   |   |   |    |   |   |   |     |      |     |     |    |   |   |            |   |   |          |      |

| • •          | +       | +   | ÷ | ٠ | •   | • | ٠        | •  | •        | • • | •  | • 1 | ٠ | • | ٠ | + | + | ٠ | ٠ | ٠ | ÷ | * | ٠ | •   | ٠ | • |     | , ( | •   |   | ٠   | ÷ | ÷ | ٠ | ÷          | +  | ٠ | ٠ | ٠  | ٠ | ŧ | ٠ | • | ٠ | ٠ | ٠  | • | 0 | • |     | ٠.   | •   |     | •  | • | • | •          | * | ٠ | • •      | , 1  |

| • •          | +       | +   | + | ٠ | ٠   | + | 4        |    | •        |     | +  | ,   | ŧ | ٠ | ٠ | ٠ | ٠ | ٠ | ÷ | ٠ | • | ę | • | •   |   | ٠ | ,   |     | ,   |   | +   | ٠ | ٠ | • | ÷          | ٠  | ٠ | • | ٠  | ٠ | • | + | + | • | ٠ | •  | • |   |   | , , |      |     | •   | ٠  | ٠ | * | •          | ٠ | ٠ | • •      | , ,  |

|              | ٠       | ٠   | ٠ | ٠ | ÷   | + | ٠        | Ŷ  | ,        |     |    |     | ÷ |   |   | ٠ | ٠ | • | ٠ | ٠ | ٠ | ٠ | • | +   | + |   |     | . 4 |     | , | •   | ÷ | ٠ | + | ٠          | ÷  | ٠ | ŧ | ٠  | • | ٠ | ٠ | ٠ | ٠ | ٠ |    | 4 |   |   |     |      | •   |     | ٠  | • | • | ·+         | ٠ |   | • •      | , ,  |

|              | ٠       | þ   | + | ٠ | ₽,  | • | , ,      | 4  |          |     |    | •   | ţ |   |   | ٠ | ٠ | ٠ | ٠ | ٠ |   | + | + | ¢   | ٠ |   | , , |     | ,   | • | ٠   | + | ٠ | é | ٠          | •  | • | ٠ | ٠  | ÷ | • | ٠ | • | ¢ | ٠ | ٠  |   |   |   |     |      |     | ٠   | ç  | ٠ | ٠ | +          | ٠ |   | • •      | , ,  |

|              | ٠       | •   | ٠ | é |     | + | ٠        | +  | • •      |     |    |     | ٠ | ٠ | ٠ | ٠ | + |   | + | ٠ | + | • |   | ٠   | ٠ |   |     |     |     |   | •   |   | + | + |            | ٠  | ٠ | + | ٠  | + | + | ÷ | • |   | + | +  |   | • |   |     |      |     | ٠   |    | ٠ | + | ٠          | + | ٠ |          |      |

|              |         |     |   | - |     | - |          |    | •        |     | •  |     |   |   |   |   | - |   | - |   |   |   | - |     | - |   |     |     |     |   |     |   |   |   | •          |    |   | • |    |   |   |   |   |   |   |    |   |   |   |     |      |     |     |    |   |   |            |   | - |          |      |

|              |         | ٠   | + | • | ٠   | + |          | ٠  |          | ٠.  |    | +   | ٠ | ٠ | ٠ | ٠ | ٠ | ٠ | ٠ | ٠ | • |   |   | +   | 6 | • | , . |     |     | • | ٠   |   | + | ÷ | +          | 6  | ø | ø | +  | ٠ | • | ٠ | + | ٠ | ÷ | +  | + | • |   |     | , .  |     |     | ٠  | + | • | +          | + |   | + +      |      |

|              | ٠       | +   | ٠ | • | ٠   | + |          | +  |          |     |    | +   | + | ŧ | ٠ | + | ٠ | + | • | 4 | þ | , | 4 | +   |   |   | , . | >   | ,   | ÷ | 4   | : | ٠ | ٠ | ٠          | ٠  | ÷ | + | ٠  | ٠ | ٠ | • | ÷ | ٠ | ÷ | ٠  | • | 4 |   |     | , .  | , 4 |     |    | • | ٠ | •          | ÷ | ٠ | • 1      |      |

| • •          |         | ٠   | ٠ | ٠ | ٠   | • | ٠        |    | •        |     |    |     | • | 2 | + | ٠ | ٠ | + | ŀ | ÷ | * | ÷ | , | ÷   |   | ÷ | , , | ,   | ,   | + | +   | ٠ | + | ÷ | •          | +  | • | ٠ | ٠. | • | ٠ | + | ÷ | ٠ | ٠ | +  | + | • | ÷ |     |      |     | •   | ٠  | • | • | ٠          | ٠ | ٠ | + 1      | . 1  |

|              |         | ٠   | ٠ | • | ,   | + | •        |    | ÷ ·      |     |    | e · | • | 4 | 4 | ٠ | ¢ | , | 8 | ٠ | ÷ | 4 | • | ÷   |   |   |     |     |     |   | ÷   | • | ٠ | ÷ | ٠          | +  | ٠ | ٠ | ٠  | ٠ | ٠ | + | , | ٠ | ٠ | •  |   |   |   |     |      | •   | ٠   |    | + | + | ٠          | • | ٠ |          | , 1  |

|              |         | ٥   | + | ÷ |     | , | ÷        | ý  | ę .      | ٠.  | ş  |     | + | ٠ | ٠ | + | ٠ | ٠ | • | ÷ | • | • | • | +   | ٠ | • | , , |     |     |   | ų   | + | ٠ | + | ٠          | ø  | ٠ | ٠ | +  | ٠ | ٠ | + | ٠ | ÷ | + | ÷  |   |   | • |     |      |     |     | ÷  |   | ٠ | ٠          | + | + |          | , i  |

|              | +       | ٠   | ٠ | + | ٠   | ٠ |          | ٠. |          |     |    | +   | • | * | ę | + | ٠ | ٠ | + | + | • | • | ٠ | . • | ٠ |   | ,   | , , | , . | • | +   | 4 |   | + | ٠          | ÷  | + | ٠ | ٠  | ÷ | ٠ | ŧ | ŕ | ÷ | + | +  |   | ٠ |   | , , |      | , , | . + | +  | ÷ | ٠ | ; <b>*</b> |   | ٠ | + 4      | . 1  |

|              | ٠       | ٠   | ٠ | + | ٠   | 0 | ٠        | •  | ٠        |     | ٠. |     | • | ٠ | ٠ | ٠ | + | ٠ | • | ٠ | ٠ | • | ٠ | •   | 6 | • |     | • 1 | ,   | ÷ | ,   | ÷ |   | • | +          | ٠  | ٠ | ٠ | ٠  | + | + | ٠ | ٠ | ÷ | + | è. | + | 6 |   | , ( |      | 1 0 |     | +  | ٠ | • | ٠          | ٠ | ٠ |          | F, 4 |

|              | ٠       | +   | ÷ | + | ¥   | ٠ | ÷        | +  | 4        | •   |    | •   | + | ٠ | ٠ | • | ٠ | • | ٠ | + | + | ÷ | + | ٠   | • | • | , , | ۱ ۱ |     | 4 | +   | ÷ | ÷ | ÷ | ٠          | ٠  | 4 | ÷ | ÷  | ÷ | ٠ | + | + | ٠ | ٠ | +  |   |   | ÷ |     | ٠. • |     | ٠   | ٠  | ٠ | ٠ | •          | ٠ | ٠ |          |      |

|              | •       | ٠   | ٠ | * | ÷   | ٠ | •        | ٠  | ٠        |     | +  |     | ٠ | + | • | ٠ | ٤ | ٠ | ٠ | • | + | ٠ | + | ٠   | ٠ |   | +   | ,   | ,   | ď | ÷   | ÷ | ٥ | • | ٠          | ÷  | ÷ | ٠ | ٠  | ş | , | 4 | + | , | ٠ | ٠  |   |   | + | ٠,  |      |     |     | +  | ŧ | + | ٠          | + | ٠ | • -      |      |

| ٠.           | ٠       | +   | • | , | ٠   | ٠ | +        | •  | •        |     | ,  |     | + | ٠ | ٠ | ٠ | + | ٠ | ٠ | ٠ | + | ÷ | ÷ | +   | ę |   | r 1 | , , | ,   |   | ÷   | ÷ | 4 | ÷ | ٠.         | 1. | ٠ | ٠ | 6  | • | ٠ | + | • | ÷ | • | •  |   | • |   |     |      |     |     | •  | + | ٠ | ٠          | ٠ | ٠ | • •      | , 1  |

|              |         | +   | ٠ | • | ٠   | + | ٠        |    | +        |     | ٠. |     | • | ٠ | + | 0 | + | ٠ | ¢ | , | ٠ | ٠ | ٠ | ,   | ٠ |   | ;   | ٠,  |     | • | •   | • | ٠ | ٠ | ٠          |    | ٠ | ٠ | ٠  | ٠ | • | ٠ |   | ٠ | ٠ | +  |   | + | • |     | , ,  | , , |     | ٠  | ŧ | + | *          | ٠ | ٠ |          | , ,  |

|              | ٠       | ٠   | + | ٠ | •   | , | ,        | ŕ  | ٠.       |     |    | ٠   | , |   | • | ٠ | + | + | + | ٠ | + |   | + |     | + |   | ٠,  | ,   | ,   | ٠ | . : | S |   | 2 | ŧ          | ٠  | ÷ | ٠ |    | ٠ | ٠ |   | ÷ | ŧ | ÷ | +  |   |   | ٠ |     | , 4  |     |     | •  | + | • |            | • | ٠ |          | , ;  |

|              | •       | ÷ . | ŧ | ٠ | +   | ٠ | +        | +  |          |     | ٠. | ,   |   | ٠ | + | • | ٠ | • | ٠ | ÷ | 4 | ŧ | ٠ | ٠   | ٠ |   | , . | ٠,  |     |   |     | ÷ | ٠ |   | 4          | 2  | ٠ |   |    | ٠ | ٠ |   |   | ŧ |   |    | 4 | ŧ |   |     | , ,  |     |     |    | ٠ |   | ٠.         | ٠ | ٠ |          |      |

|              |         | ٠   | • |   |     | ٠ | <b>,</b> |    | +        | ç . |    |     |   | 4 | ٠ |   |   | + |   |   | ٠ | + |   | ٠   | + |   | , . |     |     |   | +   | + | ٠ | ٠ |            | ŧ  | ŧ | ٠ | +  | + |   | ٠ | ¢ | * | ٠ | ٠  | , |   | ٠ |     |      |     |     | ٠  | + |   |            | 3 | , | * (      |      |

|              |         |     | ٠ | + | ٠   | + |          |    | ٠        |     |    |     |   | ٠ |   | , | , |   |   |   |   |   | + | ٠   | , |   | , , | , . |     | 6 |     | , | , | , | <b>,</b> . | ,  | , | ٠ |    |   | , |   |   | ٠ | ė | ٠  | ٠ | + | ÷ | , , | , ,  |     |     | ١. |   | ٠ | ٠          |   | ٠ | <b>.</b> |      |

|              | 5       | ٠   |   |   |     |   | ,        |    | <b>.</b> |     | ů. | 4   |   | , |   |   |   |   |   |   |   |   | ٠ |     | , |   |     |     |     | ÷ | +   |   | , |   |            |    |   | ٠ |    |   | ٠ |   |   | ٠ | ٠ | ٠  |   | ٠ |   |     |      |     |     |    |   | ٠ |            |   |   | <b>.</b> |      |

|              |         |     |   |   |     |   |          |    |          |     |    |     |   |   |   |   |   |   |   |   |   |   |   |     |   |   |     |     |     |   |     |   |   |   |            |    |   |   |    |   |   |   |   |   |   |    |   |   |   |     |      |     |     |    |   |   |            |   |   | •        |      |

|              |         |     | , |   |     | ٠ |          |    | ,        |     |    |     | ٠ |   |   |   |   |   |   |   |   |   | ٠ |     |   |   |     |     |     |   |     |   |   |   | ·          |    |   |   |    |   | ٠ |   |   |   |   |    |   |   |   |     |      |     |     |    |   |   |            |   |   |          |      |

|              |         |     |   |   |     |   |          |    |          |     |    |     |   |   |   |   |   |   |   |   |   |   |   |     |   |   |     |     |     |   |     |   |   |   |            | -  |   | • | -  | - | - | - | - |   |   |    |   | - |   |     | _    |     |     | -  |   |   |            | - | - |          |      |

|              | -       | •   | • | • | •   |   | •        | -  | -        | -   | -  | •   | - | - | • | - | • | • | • | - | • | - | - | •   | - | _ |     |     | •   | - | •   | • | • | - | •          | •  | • | - | •  | • | • | • | • | • | • | •  | • | • | • | •   |      |     | •   | •  | • | - | •          | ٠ | • | ٠.       |      |

|              | •       | •   | • | • | *** | • | •        | •  | •        |     | *  | ٠   | • |   | • | • | • | ٠ | • | • | ٠ | 4 | • | •   | • |   | '   |     |     | * | •   | * | * | • | *          | •  | • | * | •  | • | • | • | ٠ | • | * | 4  | * | * | 4 | • 1 | , ,  | , • | •   | •  | • | • | •          | • | • | • •      | , ,  |

TOTAL BLOCKS READ 1728

NUMBER OF ERROR FREE BLOCKS 1715

NUMBER THAT HAD BAD BITS 12 NUMBER THAT CAUSED RE SYNC 1

Figure 3

Table 1.

**强(%)** ~ 5 4... I I I I I (m)TEOL

(m)TEOL

MU-113V

MU-113V

MU-113V

MU-113V HIST = 6 Figure 4

\*EXPT. 1.2: 1 BIT. ŁЖ S .8....7...5SS......SS...3..

TOTAL BLOCKS READ 1728

NUMBER OF ERROR FREE BLOCKS 1634

NUMBER THAT HAD BAD BITS 60

NUMBER THAT CAUSED RE SYNC 34

Figure 5

of decoder parameter settings on the error rate performance. It was expected that the simulation results would give a better indication of the relative importance of each setting since it is easier to control for variations in each trial. Each simulation was run for 40,000 bits which had previously been established to be sufficient to produce a representative relative frequency count for each of the state pairs on the 250G/50B channel introduced in section 3.1. The 40,000 bits correspond to approximately 330 128-bit blocks. The running time of each simulation on the IBM PC running compiler BASIC is approximately 4 and 1/2 hours. The performance of the decoder for the 171/133 code is shown below:

| setting:        |     | PB    | P <sub>b</sub>        |

|-----------------|-----|-------|-----------------------|

| 1-bit qtn, hist | : 8 | 9.25% | $8.00 \times 10^{-3}$ |

| 3-bit qtn, hist | : 2 | 7.76% | $2.90 \times 10^{-3}$ |

| 3-bit qtn, hist | : 4 | 4.20% | $3.73 \times 10^{-3}$ |

| 3-bit qtn, hist | : 8 | 4.52% | $2.88 \times 10^{-3}$ |

Single bit quantization again has the worst performance in both bit- and block-error rate. Decreasing the history depth from 4 to 2 results in an increase in block error rate, but decreasing from 8 to 4 does not result in a significant change (the two simulations differ by 1 block error only). Decreasing the history depth does not necessarily increase the bit error rate. The printouts of the simulations revealed that the history depth 2 system had numerous short bursts of errors whereas the longer history systems had fewer but much longer bursts. From a block error rate point of view a history depth 2 system is not unacceptable. As well, it appears that the history depth can be decreased from 8 without incurring a loss in block error rate performance.

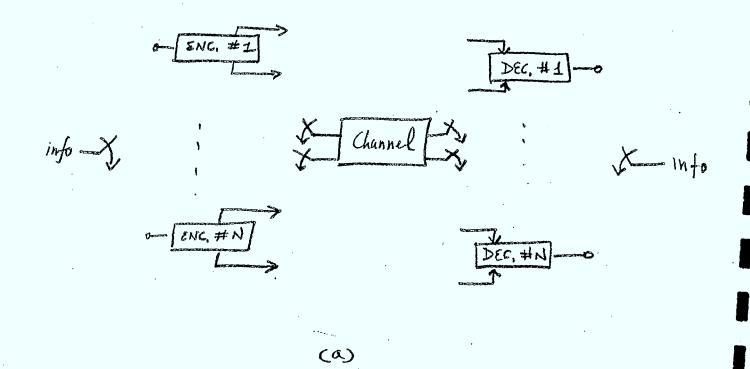

#### 3.3 VITERBI DECODING WITH INTERLEAVING

In this section we present results on the performance of Viterbi decoding with internal interleaving. The basic idea of internal interleaving is to split the transmission of data into a number of parallel streams that are encoded and decoded separately as shown in Figure 6a. In practice it is not necesary to replicate the encoders and decoders, but instead the logic needed to carry out these operations is time-shared among the N streams. Consequently interleaving is achieved without introducing a frame structure and at only a linear increase in the memory requirements. Indeed the combined encoder-interleaver is equivalent to the longer constraint length code shown in figure 6b. It can be shown that this

Figure 6

code has the same minimum distance as the shorter code, so that its performance in a random error environment will be the same. In a burst error environment, however, the longer code will have the better performance.

The same computer simulation programs discussed in the previous section were used to investigate Viterbi decoding with internal interleaving. It is clear that only one of the encoder-decoder pairs needs to be simulated so no change is required in the Viterbi decoder program. The only change required in the channel simulation program is that only every L-th output of the channel is passed to the decoder if the degree of interleaving is L.

In the simulation the channel was considered to be in a burst error mode if the channel was in the bad state. burst error statistics were specified by fixing the mean holding time in the bad state, and the percent of the time spent in the nonburst mode was specified by selecting the mean holding time to be some multiple of that of the bad Each simulation consisted of approximately 330 128 bit In the first set of simulations the mean burst error length was 50 bits and the proportion of time spent in the burst mode was 1/6. By introducing degree 5 interleaving, the effective channel seen by the decoder is approximately a 50G/10B channel. The block error rate is reduced by a factor of 3.5 and the bit error rate by a factor of 6.5. (See Table 2.) The third experiment in this set simulated a 50G/10B channel without interleaving. It can be seen that the results are quite close to those of the channel with the same effective parameters after degree 5 interleaving.

In the second set of experiments, the mean burst length was increased to 100 bits and the proportion of the time spent in the burst mode was reduced to 1/3. The system without interleaving performs quite poorly and the introduction of interleaving introduces only some improvement. The degree 10 interleaving system has a mean holding time of 5 bits in the bad-bad state, the same as the degree 5 system in the first set of experiments. The mean holding time in the good-good state however is only 10 bits so the decoder does not have enough good samples, on the average, to get back on the correct path.

For a given fixed ratio of time spent in the good state to time spent in the bad state, the Viterbi decoder will span the following two extremes. When the bursts are very long the decoder will encounter 4 modes of sustained duration corresponding to the 4 possible state pairs. The performance will be the weighted average of the performance during each of these modes. For the cases considered above the performance will be dominated by that of the bad-bad state. The bit error

| Channel         | <u> </u> | Effective | Block Em | Bit Emr<br>Rate        |

|-----------------|----------|-----------|----------|------------------------|

| 2504/2018       | 1        | 250G/50B  | 4,5%     | z.9×10 <sup>3</sup>    |

| 2504/508        | 5        | ~ 504/103 | 1,2%     | 4,3×/0                 |

| <i>१०६/इ</i> ०८ | 1        | 50 K/10B  | 0.97%    | 2,8 × 10 4             |

| 2006/100B       | <u>.</u> | 2004/1008 | 11.7%    | 1,4 ×102               |

| 200G/100B       | 5        | 404/205   | 8.1%     | 5,2×103                |

| 200G/100B       | 10       | 204/10B   | 5.4%     | 2.6 × 10 <sup>-3</sup> |

Table 2.

rate for this code has been found to be .14 by simulation. The proportion of time spent in the bab-bad state for the first set of experiments is 1/36, so the average bit error rate should be about 3.9x10-3 when the burst length is very long. This is close to the figure obtained for the 250B/50B system without interleaving. For the second set of experiments the predicted bit rate is 1.55x10-2 which again is quite close to that of the system without interleaving.

As the degree of interleaving is increased until it exceeds the mean burst length, the decoder will reach a plateau with performance of that of a system in which the channel randomly selects one of the two modes (good or bad) with probability equal to the proportion of time spent in the given modes. No attempt was made to establish what the limiting performance for this extreme would be.

## 4.0 TRANSMISSION PROTOCOLS FOR MULTITONE MODEM

An objective of the project was to extend the present transmission protocol to increase the information rate that can be reliably achieved using a multi-FSK signal format and combining code diversity with ARQ techniques. In this section we present an analysis of the present transmission protocol; then we present an analysis of a protocol proposed by Shu Lin and an adaptive protocol that combines the Lin protocol with a code diversity ARQ system.

## 4.1 PRESENT TRANSMISSION PROTOCOL

The present transmission protocol defines a sequence of packet exchanges that effect the transfer of a message from a sender terminal to an acceptor terminal. The channel is shared by both terminals so transmissions are constrained to be half-duplex with packets travelling in opposite directions alternately accessing the channel. The terminals set up the transfer of a message by exchanging calling and response packets. The message transfer is carried out through the exchange of message and acknowledgment packets. The message transfer is ended with the sender terminal transmitting termination packets.

The present protocol handles the transmission of one message at a time. A message may consist of up to 1280 bytes. Prior to transmission the message is segmented into subblocks of 16 bytes. The acceptor terminal is given the number of such subblocks during the set up phase. Each subblock has a sequence number byte and a CRC byte attached to it to form a subpacket, which forms the basic unit of retransmission. Subpackets are transferred to the acceptor terminal in fixed-length frames that can accomodate 8 subpackets. Each frame consists of a header followed by 8 subpackets, with padding used to fill up unoccupied subpacket slots if necessary. Thus by design each subpacket is bundled separately and thus its retransmission can be handled separately from that of other subpackets.

Fixed-length frames, called message packets, and fixed-length acknowledgment packets alternate in using the channel. The message packets consists of an 11.5 byte header followed by the 8 subpackets. Of the 1244 bits in the message packet at most 1024 can be used for information. Acknowledgment packets of 148 bits follow each message packet transmission. The propagation and software delays add an equivalent of 10 bits at 100 bps transmission rate. Barring errors, after the exchange of one message packet at most 1024 information bits will have been transferred in the time 1402 bits could have been transmitted on the channel. Thus the present protocol has a maximum throughput efficiency of 73%.

We now present an analysis of the present transmission protocol. The purpose of carrying out such an analysis is to lay the framework within which any extended protocol should be evaluated. In this analysis we will neglect the effect of errors in the acknowledgment packets. Let Kbe the message length in subpackets,  $1 \le K \le 80$ , and suppose that a frame can accomodate up to L subpackets. Let e be the probability that a subpacket is received in error (using hard decisions) and assume that subpacket errors occur independently. The sequence of message packet transmissions can be divided into two phases: in mode A the number of outstanding subpackets at the transmitter is greater than or equal to L so frames carry a full set of subpackets in each transmission; in mode B the number outstanding is less than L so each frame transmitted is partly empty. Clearly mode B transmissions introduce inefficiencies in the use of bandwidth and the purpose of the analyses is to quantify these inefficiencies.

Suppose that K = QL + R, where  $0 \le R < L$ ; then at least Q mode A transmissions will be required. Let MF(K) be the total number of mode A transmissions rquired for a message of length K. In Appendix C we show that the mean of MF(K) is:

$$E(MF(K)) = Q + \sum_{i=Q}^{\infty} (\sum_{j=0}^{K-L} Pr(s_i=j))$$

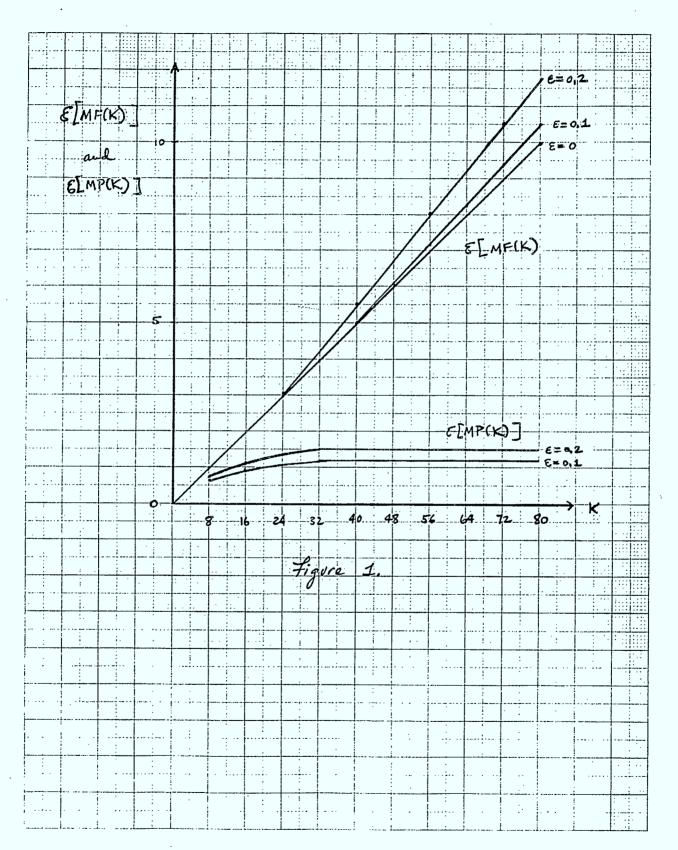

where  $s_i$  is a Binomial random variable with parameters iL and e. The over the Binomial terms can be approximated by the error function (i.e. integral over a Gaussian) and only a few terms in the infinite series turn out to be significant. Figure I displays the mean of MF(K) versus K.

Mode B transmissions will commence when the number of subpackets remaining for transmission becomes less than L. Suppose that this number is r,  $0 \le r < L$ . Partly empty frame transmissions will continue until all r subpackets have successfully been transferred to the acceptor terminal. Let MP(r) be the number of frame transmissions required to accomplish this. In Appendix C we also show that the mean of MP(r) is given by:

$$E(MP(r)) = 1 + \sum_{j=1}^{r} {r \choose j} \frac{e^{j}}{1-e^{j}} (-1)^{j+1}$$

Figure 2 shows E(MP(r)) as a function of r. As expected the number of transmission increases with r. Since the range of r depends on L, Figure 2 can be used to quantify the loss in efficiency due to too large a value of L.

The number of outstanding subpackets r during the first mode B transmision is a random variable that depends on K.

. ...

!

In the Appendix we derive the distribution of r conditioned on K, and we then compute the mean of MP(r) averaged over r. For large values of K, r becomes uniformly distributed in the interval 0 #r#L-1. Figure 1 shows this mean as a function of K.

The two curves in figure 1 can be added to obtain the mean number of total frame transmissions required to transfer a message of length K, that is E(M(K)). The throughput efficiency is then given by:

$$EFF = \frac{K}{E(M(K))(L+H)}$$

$$= \left(\frac{K/L}{E(M(K))}\right) \left(\frac{L}{L+H}\right)$$

= EFFREL x MAX EFF

where H is the overhead incurred in each message packet/acknow-ledgment cycle, and where EFFREL is defined as the relative efficiency. Figure 3 shows the relative efficiency as a function of K. It can be seen that as K increases the relative efficiency approaches that of selective repeat ARQ, namely 1 - e. In effect for large K, the inefficiencies due to mode B transmissions are negligible. Thus if we are considering very long messages, we can directly analyze the transmissions of subpackets and ignore the frame structure of the system.

The relative efficiencies shown in Figure 3 correspond to three values of subpacket error probabilities, e=0,e=0.1. and e=0.2. It can be seen that for this range of values the relative efficiencies do not differ greatly. In experiments conducted last year subblock error rates of 10-2, 10-1, and 2x10-1 were observed for code diversity, frequency diversity, and single channel transmissions. One concludes from Figure 3, that the combination of code diversity with selective repeat ARQ, henceforth denoted by ARQCD, for this range of error probabilities is not worthwhile since code diversity incurs 50% overhead, and thus a higher throughput is achievable if this overhead were replaced by additional subpacket transmissions. On the other hand, as the error rate increases diversity transmission can be expected to keep the throughut from deteriorating to zero much longer than single channel FSK because of its ability to correct errors. Clearly what is needed is a transmission protocol that dynamically varies between these two extremes as the channel error conditions vary. We will introduce such a protocol in the last section.

E = 0, 1 EFFREL ε= 0, **1** -0.8 = 42 E=0,2 K `..**.** .

### 4.2 A DIVERSITY-ON-DEMAND TRANSMISSION PROTOCOL

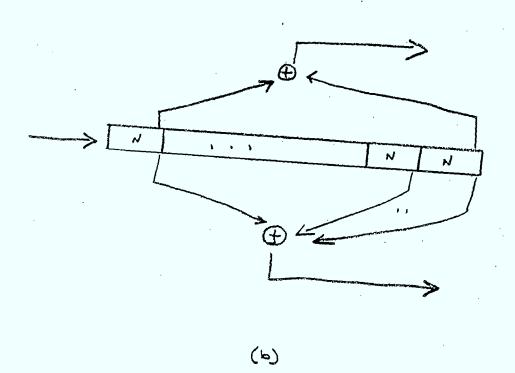

Suppose that M FSK signals are available for information transmission and that each signal is organized as in the existing transmission protocol but with the headers combined into one single header as shown in Figure 4. The first part of the header up to the software sync byte would remain the same. The second part would be capable of carrying more information than presently required so it could be shortened or modified as necessary. Similar considerations would apply to the acknowledgment packets.

Once the message packets header and acknowledgment packet lengths are seleceted (and here we are assuming that they will remain fixed), the maximum achievable throughput will be fixed and the particular form of ARQ will affect the performance only through the relative efficiency. We will assume that the transmitted messages are very long so that mode B transmissions can be neglected. The relative efficiency will be given by E(N), where N is the number of transmissions required by a given subpacket.

The basic mechanism of ARQ schemes, retransmision, is essentially a diversity technique, namely time diversity without combining. Viewed this way it is clear that ARQ schemes do not make use of all of the information available at the receiver and that better performance should be possible by using some form of combining. We will consider the use of code diversity as the means of utilizing the extra information. The scheme considered has been discussed by Wang and Lin (Trans. on Communications, May 1983). We will henceforth refer to the scheme as ARQDD.

For throughput analyses purposes we can consider the protocol as if a single subpacket is being retransmitted at a time. The protocol employs a cyclic code for error detection and a rate 1/2 convolutional code for code diversity. Each information subpacket (including the sequence number) is encoded using the cyclic code. The resulting block is convolutionally encoded with the encoder intialized to the zero state and enough zeros appended to the block so as to drive the encoder back to the zero state. Each subpacket is thus bundled separately so that its retransmission can be handled independently of that of other subpackets.

The upper and lower branches of the encoder output are buffered separately and only the upper branch is transmitted at first. At the receiver the received sequence is divided by the appropriate polynomial that allows the recovery of the cyclically encoded block when errors have not been introduced in transmission. The outcome of this division and the subsequent check of the recovered block are used to detect errors. If none are found the subpacket is accepted. If the block is found to have some errors, the receiver sends a negative acknowledg-

|              | 1 | 2   |                                              | <u>て</u> |    |

|--------------|---|-----|----------------------------------------------|----------|----|

| . ц.         |   |     |                                              |          | 工工 |

| E            |   | ·   |                                              |          |    |

| A            | , | , , |                                              |          |    |

| <b>&amp;</b> |   | 8   | <b>\</b> \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |          |    |

| 15           |   |     |                                              |          |    |

|              |   |     |                                              |          |    |

|              |   |     |                                              |          | M  |

figure 4

ment requesting a transmission of the other branch. The second branch is processed in the same way: it is divided, checked for errors and accepted if none are found. If at this point errors are found, both received branches are used to carry out Viterbi decoding. The sequence output by the decoder is then checked for errors using the cyclic code. At no extra cost in bandwidth we have obtained an extra opportunity to correctly decode the information. Note that all decoding prior to Viterbi decoding uses hard decisions, but that Viterbi decoding itself can use soft decisions.

If the second transmission and subsequent Viterbi decoding fail, a request for a retransmission of the first branch is made. The branch is processed as the second branch was processed in the previous step. In Lin's version of the protocol, the older version of a branch is discarded. However if soft decision decoding is used, the old and new versions of a branch could be combined prior to Viterbi decoding. The alternate transmission of branches continues until the subpacket is successfully transferred or until some upper limit is reached.

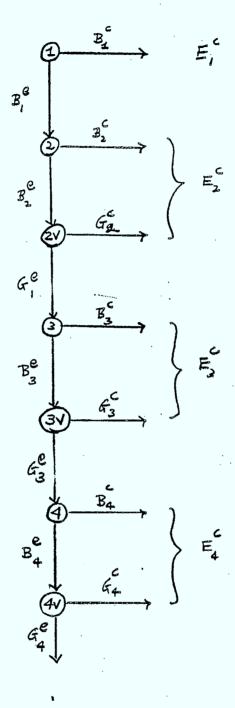

The possible sequence of events for ARQDD is shown in Figure 5 where Bc(i) is the event that the ith transmission is received errorfree and Be(i) is the event that it is found in error. We will assume for simplicity that the probability of failing to detect errors is negligible relative to the probabilities of the other events. Gc(i) is the probability that Viterbi decoding successfully decodes a pair of erroneous branches after the ith transmission. Assume that block errors occur at independently and with the same probability:

$$P_c = Pr(Bc(i))$$

and

$$1 - P_c = Pr(Be(i))$$

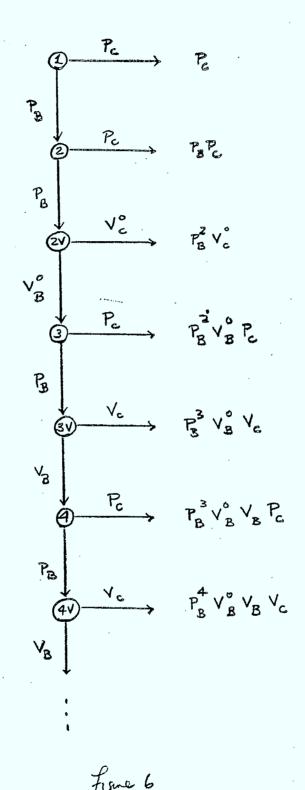

Let  $V^{C}$  be the probability that the first Viterbi decoding is successful and let  $V^{C}$  be the probability that subsequent Viterbi decodings are successful. Note that the first probability is conditioned on the two branches having had errors detected on them, whereas the second probability in addition has the condition that one of the brances participated in a previous unsuccessful Viterbi decoding. Thus the second probability will be less than the first. The corresponding sequence of event probabilities is shown in Figure 6. To calculate the mean number of transmissions we need only consider the event Ec(i) and the event Ec(i) that correspond to the ith transmission being successful and unsuccessful respectively. Since Ee(i) occurs if the ith transmissions has errors and the subsequent Viterbi decoding fails, we have that

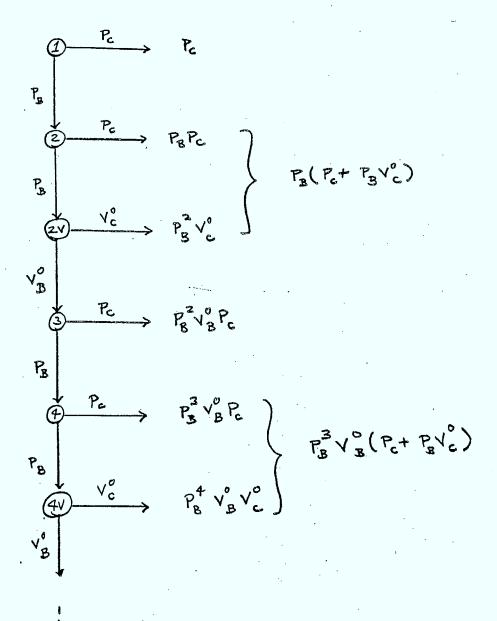

Figure 5

$$Pr(Ee(i)) = Pr(Be(i)) Pr(Ge(i))$$

$$= (1 - P_c) (1 - V^c)$$

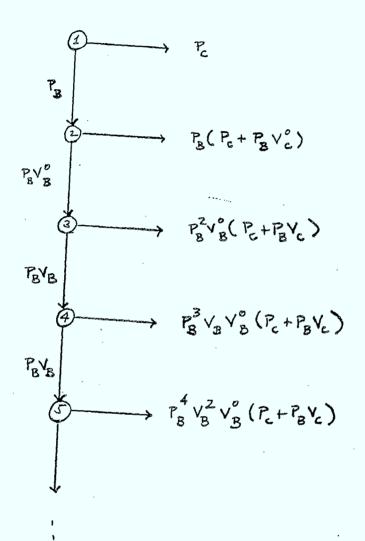

The simpler sequence of event probabilities is shown in Figure 7. The probabilities of N are given by:

$$Pr(N=i) = \begin{cases} P_{c} & i=1 \\ P_{B}(P_{c} + V_{o}^{c}) & i=2 \\ P_{B}^{i-1}V_{B}^{o} V_{B}^{i-3} (P_{c} + P_{B} V^{c}) & i \ge 3 \end{cases}$$

where  $P_B = 1 - P_c$  and  $V_B = 1 - V_c$ . The mean number of transmissions is then found to be:

$$E(N) = P_{c} + 2P_{B}(P_{c} + P_{B}V_{c}^{O}) + \frac{1 + 2(P_{c} + P_{B}V_{c})}{P_{c} + P_{B}V_{c}}$$

and the relative throughput efficiency is then 1/E(N).

The evaluation of the throughput efficiency requires the transmission error probability  $P_B$ , and the two probabilities of successful Viterbi decoding,  $\quad V^{c}_{c}$  and  $V_{c}_{c}$ . Note that  $P_{B}_{c}_{c}$  is the error probability that results using hard decisions. Later in this section we will estimate these parameters for a bursty channel by computer simulation. We will find that  $V_{c}_{c}$  requires much computation to estimate so it would be useful to have bounds on E(N) that depend only on the other two parameters.

An upper bound is obtained for E(N) by analyzing the inferior system posed by Lin where Viterbi decoding always uses a new pair of branches and thus can take place only during every other transmission. The sequence of event probabilities is shown in Figure 8 and the resulting mean is an upper bound to E(N):

$$E(N) < \frac{1 + P_B}{1 - P_B^2 V_B^0}$$

We can also obtain a lower bound as follows. Since V is always less than  $V^c$ , we can replace V by  $V^c$  in the exact formula for E(N) and obtain an optimistic estimate. Combining the upper and lower bounds we have:

Figure 7

Figure 8

$$\frac{1 + \frac{P_B}{1 - P_B V_B^0}}{1 - P_B V_B^0}$$

$\angle E(N) \angle \frac{1 + P_B}{1 - P_B^2 V_B^0}$

When the channel is very good we have  $\mathbf{P}_{\underline{B}}$  much less than 1 and the bounds yield

$$E(N) \approx 1 + P_R$$

which intuitively agrees with the fact that Viterbi decoding would seldom be required. When the channel is very noisy the  $P_{\rm R}$  approaches 1 and

$$\frac{2 + V_{B}^{O}}{1 - V_{B}^{O}} < E(N) < \frac{2}{1 - V_{B}^{O}}$$

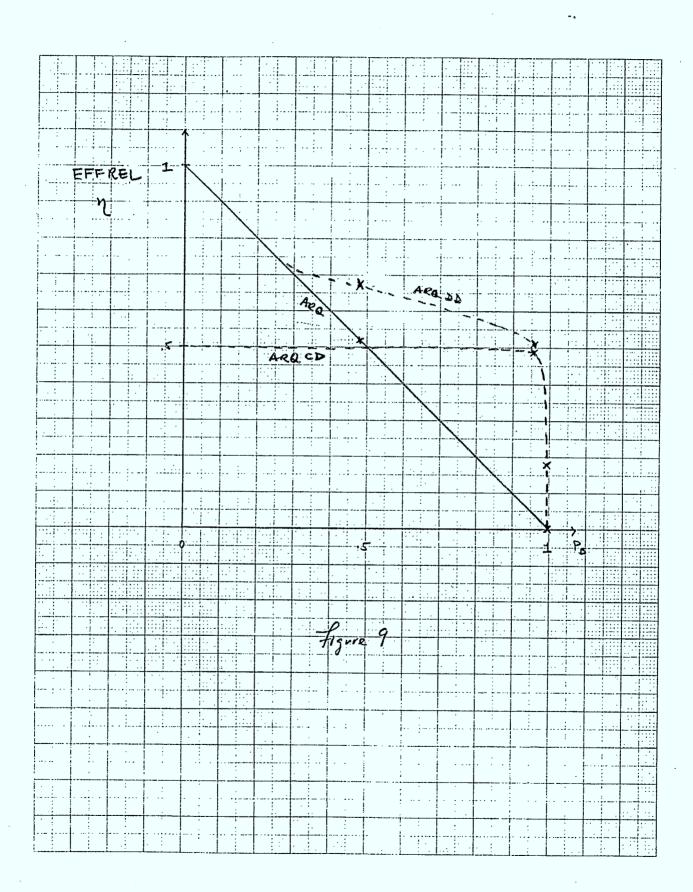

In order to obtain the parameters required to estimate the performance of ARQDD, we modified the simulation programs to estimate the required parameters. An information block of 120 bits (all zeros in the simlation) was "encoded" using the 171/133 code and the resulting encoded branches (two blocks of 126 zeros) were produced. The first branch was passed through the bursty channel. The resulting sequence was inspected for hard errors and if none was found the block was counted as correct on the first transmission. Otherwise a new branch was "requested." In producing the new branch the initial state of the channel was reselected at random in order to simulate the time diversity nature of the retransmissions. The ARQ protocol was followed in the prescribed way and a tally of the various events was kept. Table 1 shows the results of three simulation experiments and Figure 9 shows the corresponding results in graphical form.

In the first two experiments the channels alternate between periods of good error conditions and periods of bad error conditions. The first experiment corresponds to the 250VG/50B channel introduced earlier in the report. In this experiment the channel is relatively "very good" in that a significant (51%) of the blocks are recieved error free after the first transmission. The bounds for ARQDD are very tight in this case and the throughput for ARQDD is 67%, a 16% improvement over selective repeat ARQ which would have a throughput of 51%. In the second experiment the channel is 250G/50B and only 4% of the packets get through on the first transmission. Thus the throughput has collapsed to nearly zero for selective repeat ARQ. The bounds for ARQDD are again very tight and

throughput is 51%, a tremendous improvement over selective repeat ARQ. The difference of course is due to the error correcting capability of the scheme. For this range of channel conditions the block error rate is nearly 1 with error detection only, but the convolutional code is chable of correcting most of the error patterns, so that most blocks are recieved correctly after the two transmissions required to carry out Viterbi decoding. Essentially the system has switched to code diversity operation with the diversity branch being provided by time diversity. This is equivalent in throughput to ARQCD which provides the diversity branch in simultaneous frequency diversity. Note however that ARQCD entails a smaller delay in delivering a given block to the receiver.

The third experiment has the channel continously in the bad state. The throughput efficiency of selective repeat ARQ is zero, but the efficiency of ARQDD is 19%. Note that in this case, the bounds were not tight and it was necessary to run a second simulation to estimate V<sub>C</sub>. Because of the large number of errors in the transmissions, many Viterbi decodings are required before a block is successfully decoded at the receiver. The simulation to estimate this parameter took about 11 hours on the IBM PC. This experiment demonstrates that ARQDD continues transmitting information through the very noisy channel way after ordinary ARQ schemes have collapsed. The system thus appears to be extremely well-suited to HF radio transmission where the ability to adapt to changing channel conditions is essential.

#### 4.3 AN ADAPTIVE TRANSMISSION PROTOCOL

The adaptivity of ARQDD to the changing channel conditions is accomplished through the automatic retransmission of erroneous subpackets. For the multi-FSK system under consideraa large number of subpackets are transmitted in each tion ' Under very noisy conditions this will require the retransmission of a large proportion of each frame. This will require considerable complexity in terms of the buffer management and sequence numbering operations. Thus it is preferable if the protocol operates so that the number of retransmissions is kept low, while operating at a throughput efficiency close to that of ARQDD. As indicated in the previous section, when the throughput of ARQDD is near 50%, it is equivalent in throughput to ARQCD which has a throughput of  $V_{\rm C}^{\rm O}$  and which is shown in Table 1 as well as in Figure 9. It can be seen that by switching to ARQCD when the throughput of ARQDD falls to near 50%, significant simplifications in the implementation will be obtained at little loss in throughput. Since ARQCD has a throughput that never exceeds 50%, the protocol should switch to ARQDD and perhaps even ordinary ARQ when the channel conditions are favorable.

The obvious decision rule for switching between the two protocols is to compare the number of subpackets that require retransmission to a threshold. The switch from ARQDD to ARQCD is effected when the number of packets that require retransmission exceeds the threshold. The switch in the reverse direction should be based on the number of subpackets that arrive incorrectly prior to Viterbi decoding since we are trying to establish that the system can operate satisfactorily using essentially hard decisions only. The required count can be made by retaining the same subpacket format and predecoding procedures at the receiver. Each subpacket would first be divided and error checked prior to Viterbi decoding. either of the branches received in two different frequencies is correct, then Viterbi decoding can be skipped, and as well the count required to implement the decision rule for switching can be carried out. The retention of this part of the ARQDD protocol also gives the receiver the option to handle many more subpackets per frame than it would be able to decode in ARQCD where every branch pair would undergo Viterbi decoding.

#### 4.4 OPEN ISSUES

The discussion in this section has concentrated only on the throughput performance of the various schemes for several relatively simple models. It has been established that code diversity significantly extends the range of channel conditions within which information can be reliably transmited. As well the combination of code diversity with ARQ makes it possible to operate at high throughput efficiencies when channel conditions are favorable. We expect that these conclusions will hold for real channels as well because the schemes make no specific assumptions about the channel statistics and because the schemes are inherently adaptive to a coarse statistic, block error rate.

The schemes need to be investigated further with attention paid to implementation details. The memory and processing requirements need to be estimated. The algorithm can then be optimized for maximum performance within the constraints placed on the processing and memory requirements.

## APPENDIX A

| MODU                                                         | LE                                                           |      | PAGE                            |

|--------------------------------------------------------------|--------------------------------------------------------------|------|---------------------------------|

| 1.1<br>1.2<br>1.3<br>1.4                                     | MAIN LOOP<br>INIT<br>ACS1-2<br>SCALE<br>SEARCH<br>HIST       |      | 1<br>1<br>1<br>2<br>2<br>2<br>3 |

| 1.2.1<br>1.2.1.1<br>1.2.1.2<br>1.2.1.3<br>1.2.1.4            | SHIFT<br>GETBIT<br>PUTBIT<br>STROBUP<br>STROBON              | •••• | 3<br>4<br>4<br>5<br>5           |

| 1.2.1.2.1<br>1.2.1.2.1<br>1.2.1.2.1<br>1.2.1.2.1<br>1.2.1.2. | .1 NEXTPN<br>.2 REP<br>.2.1 KEYCHK<br>.2.2 PUTC<br>.2.3 TEXT |      | 5<br>6<br>7<br>7<br>7<br>8      |

MODULE NAME: MAIN LOOP (VITERBI) MLOOP MNEM: HIER: 1.0 This is the top level module of the hierarchy DESC: Real-Time Viterbi Decoder. Upon being entered, initializes variables and storage areas. It then enters the main loop of the program that repetitively implements the decoding cycle. CALLED MODULES: INITIALIZE NAME: HIER: MNEM: INIT 1.1 ADD, COMPARE, SELECT NAME: ACS1, ACS2 HIER: MNEM: SCALE METRICS NAME: MNEM: SCALE HIER: 1.3 SEARCH FOR BEST STATE NAME: MNEM: SEARCH HIER: NAME: HISTORY UPDATE MNEM: HIST HIER: 1.5 MODULE NAME: INITIALIZE MNEM: INIT HIER: 1.1 Initialize input ports. Initialize output port. DESC: Set long term history to zeros. Setup PN generators. Zero block variables. COMMON DATA: BF1 (WRITE) ALLOK, NOBLOCK, ERRS, RESYNC, (WRITE) PN1, GPN (WRITE) OUT (WRITE) OUTPORT, PCR, ACR, IFR, OUTDDR, DDRA, DDRB (WRITE) HO (WRITE) CALLED FROM: MAIN LOOP (VITERBI) NAME: MNEM: MLOOP HIER: 1.0 ADD, COMPARE, SELECT MODULE NAME: ACS1, ACS2 MNEM: HIER: 1.2 These two routines each update one of the state information tables. ACS1 uses State Organization Table #1 (SOT1) to update the information in buffer #1 (BF1), the results being

put in buffer #2. ACS2 uses SOT2 to update BF2 and the results are put in BF2. The states are updated in groups of four states

all states are done. At the start of the ACS operation

data output, data input, and metric distances are calculated.

LOCAL DATA:

SPSAVE (READ/WRITE)

COMMON DATA:

BF2, SOT1 (READ) FOR ACS1:

BF2 (READ/WRITE)

BF2, SOT2 (READ) FOR ACS2:

BF1 (READ/WRITE)

T0000, T0001, ... T1111 (READ)

CALLED FROM:

NAME: MAIN LOOP (VITERBI)

MNEM: MLOOP HIER: 1.0

CALLED MODULES:

SHIFT OUT DATA, GET DATA NAME: HIER: MNEM: SHIFT 1.2.1

MODULE NAME: SCALE METRICS

MNEM: SCALE

1.3 HIER:

DESC: Subtracts previous best metric from all state metrics. Also, if any metric gets above 32000 then it is reduced to approximately 16000. The truncation should not be required if calls are made frequently to this routine.

CALLING PARAMETERS:

Register U contains the address of the buffer to be scaled (BF1 OR BF2).

Variable: BESTM should be equal to or less than the metric.

LOCAL DATA:

SCOUNT (READ/WRITE)

COMMON DATA:

BF1, BF2 (READ/WRITE)

BESTM (READ)

CALLED FROM:

MAIN LOOP (VITERBI) NAME:

HIER: 1.0 MNEM: MLOOP

SEARCH FOR BEST STATE MODULE NAME:

MNEM: SEARCH

HIER:

DESC: Loop through all states to find the lowest metric.

Save the metric and path pointer for later use.

CALLING PARAMETERS:

Register U should point to buffer to be searched.

LOCAL DATA:

COUNT (READ/WRITE)

COMMON DATA:

BESTM, BESTV (READ/WRITE) BF1. BF2 (READ)

CALLED FROM:

NAME: MAIN LOOP (VITERBI)

MNEM: MLOOP HIER: 1.0

MODULE NAME: HISTORY UPDATE

MNEM:

HIST

HIER:

1.5

DESC: Trace back operation using best path pointer to find most likely output. Move recent history (path pointers) to long term history. Create new path pointers.

CALLING PARAMETERS:

Register X contains a pointer to the first path pointer in whichever buffer is selected.

BESTV should contain the best path pointer found by SEARCH.

LOCAL DATA:

CURCOL (READ/WRITE)

COMMON DATA:

BESTV (READ)

CALLED FROM:

NAME: MAIN LOOP (VITERBI)

MNEM: MLOOP HIER: 1.0

MODULE NAME: SHIFT OUT DATA, GET DATA

MNEM:

SHIFT

HIER:

1.2.1

DESC: Output data. Raise strobe to indicate data valid. Get eye values. Rotate eye values into position. Calculate branch distances. Lower strobe.

LOCAL DATA:

TEMPA, TEMPB (READ/WRITE)

COMA, COMB (READ/WRITE)

CALLED FROM:

NAME: ADD, COMPARE, SELECT MNEM: ACS1, ACS2 HIER: 1.2

CALLED MODULES:

NAME: GET DATA FROM ADC BOARD

MNEM: GETBIT HIER: 1.2.1.1

NAME: OUTOUT BIT

MNEM: PUTBIT HIER: 1.2.1.2

NAME: RAISE STROBE

MNEM: STROBUP HIER: 1.2.1.3

NAME: LOWER STROBE

MNEM: STROBDN HIER: 1.2.1.4

MODULE NAME: GET DATA FROM ADC BOARD

MNEM: GETBIT 1.2.1.1

DESC: Wait for data ready from ADC board. Read value from ADC board. After isolating lower seven bits run value through the quantization map.

LOCAL DATA:

MAP (READ)

Register A & B each hold one of the mapped, integrated eye values.

COMMON DATA:

IFR (READ/WRITE) ADAT, BDAT (READ)

CALLED FROM:

NAME: SHIFT OUT DATA, GET DATA MNEM: SHIFT HIER: 1.2.1

MODULE NAME: OUTPUT BIT

MNEM: PUTBIT HIER: 1.2.1.2

DESC: Shift out a bit from the variable OUT. This value is placed on the output port.

CALLING PARAMETERS:

OUT should contain the most likely output bits found in the routine HIST.

COMMON DATA:

OUT (READ/WRITE)

OUTPORT (READ/WRITE)

DOUT (WRITE)

CALLED FROM:

NAME: SHIFT OUT DATA, GET DATA MNEM: SHIFT HIER: 1.2.1

CALLED MODULE:

NAME: DO BLOCK ERROR CHECKING

MNEM: ERRCHK HIER: 1.2.1.2.1

MODULE NAME: RAISE STROBE

MNEM: STROBUP HIER: 1.2.1.3

DESC: Raise strobe to indicate output data valid.

COMMON DATA:

OUTPUT (READ/WRITE) DOUT (WRITE)

CALLED FROM:

NAME: SHIFT DATA OUT, GET DATA MNEM: SHIFT HIER: 1.2.1

MODULE NAME: LOWER STROBE

MNEM: STROBDN HIER: 1.2.1.4

DESC: Lower strobe on data output port.

COMMON DATA:

OUTPUT (READ/WRITE)

DOUT (WRITE)

CALLED FROM:

NAME: SHIFT DATA OUT, GET DATA MNEM: SHIFT HIER: 1.2.1

MODULE NAME: DO BLOCK ERROR CHECKING

MNEM: ERRCHK HIER: 1.2.1.2.1

DESC: Keeps a running record of the most recent output bits so that the internal shift register can be reloaded if synchronization is lost. The bit to be output is compared to the internal PN generator and any differences are counted. When the block is done, one of three characters is printed:

"." - no errors in block

"\*" - less than ERRLIM errors

"s" - ERRLIM or more errors (Reload shift register)

The appropriate counter is also incremented.

CALLING PARAMETERS:

BITOUT should contain bit just output.

LOCAL DATA:

BCOUNT (READ/WRITE) STOR1, STOR2 (READ/WRITE)

COMMON DATA:

BITOUT (READ)

ERRS, RESYNC, ALLOK, NOBLOCKS (READ/WRITE)

CALLED FROM:

NAME: OUTPUT BIT

MNEM: PUTBIT HIER: 1.2.1.2

CALLED MODULES:

NAME: NEXT PSEUDO-NOISE BIT

MNEM: NEXTPN HIER: 1.2.1.2.1.1

NAME: REPORT BLOCK ERRORS

MNEM: REP HIER: 1.2.1.2.1.2

NAME: CHECK KEYBOARD

MNEM: KEYCHK HIER: 1.2.1.2.1.2.1

NAME: PRINT CHARACTER

MNEM: PUTC HIER: 1.2.1.2.1.2.2

MODULE NAME: NEXT PSEUDO-NOISE BIT

MNEM: NEXTPN

HIER: 1.2.1.2.1.1

DESC: Generate next pseudo-noise value from internal shift register and feed it into the shift register to carry on. The sequence generated is 511.

LOCAL DATA:

CHECK (READ/WRITE)

PN1, PN2 (READ/WRITE)

Register A returns the PN bit.

CALLED FROM:

NAME: DO BLOCK ERROR CHECKING

MNEM: ERRCHK HIER: 1.2.1.2.1

MODULE NAME: REPORT BLOCK ERRORS

MNEM:

REP

HIER: 1.2.1.2.1.2

DESC: Report on the block errors encountered. Report includes: total blocks read; number of error free blocks; number that had bad bits; and number that caused resynchronization.

CALLING PARAMETERS:

NOBLOCK, ALLOK, ERRS, RESYNC should contain appropriate block error values.

LOCAL DATA:

TB, OK, NB, RS, MEND (READ)

COMMON DATA:

NOBLOCK, ALLOK, ERRS, RESYNC (READ)

CALLED FROM:

NAME: DO BLOCK ERROR CHECKING

MNEM: ERRCHK HIER: 1.2.1.2.1

CALLED MODULES:

NAME: OUTPUT STRING

MNEM: TEXT HIER: 1.2.1.2.1.2.3

NAME: PRINT DECIMAL NUMBER

MNEM: PNUM HIER: 1.2.1.2.1.2.4

MODULE NAME: CHECK KEYBOARD

MNEM: KEYCHK

HIER: 1.2.1.2.1.2.1

DESC: Get a character from the keyboard if one is

waiting, else return zero (null).

LOCAL DATA:

Returns the read character in register A.

COMMON DATA:

STATUS, DATA (READ)

CALLED FROM:

NAME: DO BLOCK ERROR CHECKING

MNEM: ERRCHK HIER: 1.2.1.2.1

MODULE NAME: PRINT CHARACTER

MNEM:

PUTC

HIER:

1.2.1.2.1.2.2

DESC:

Print a character on the terminal.

CALLING PARAMETERS:

Register A contains ASCII value to be printed.

COMMON DATA:

STATUS (READ) DATA (WRITE)

CALLED FROM:

NAME: DO BLOCK ERROR CHECKING

MNEM: ERRCHK HIER: 1.2.1.2.1

NAME: OUTPUT STRING

MNEM: TEXT HIER: 1.2.1.2.1.2.3

NAME: PRINT DECIMAL NUMBER

MNEM: PNUM HIER: 1.2.1.2.1.2.4

MODULE NAME: OUTPUT STRING

MNEM: TEXT

HIER: 1.2.1.2.1.2.3

DESC: Print a string on the terminal until a zero (null)

is encountered.

CALLING PARAMETERS:

Register X holds starting address of string.

CALLED FROM: