Analysis and Design of Land Mobile

Communications Systems Based on

Digital Techniques

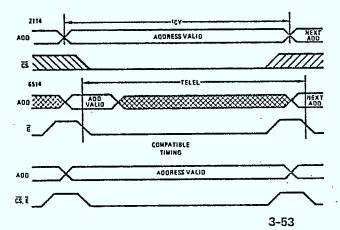

Final Report

Contract: OSU79-00060

Submitted By

Professor Samy Mahmoud (Principal Investigator), and

Professor Cyril Leung

Department of Systems Engineering and Computing Science

Carleton University

March, 1980

Analysis and Design of Land Mobile

Communications Systems Based on

Digital Techniques

Final Report

Contract: OSU79-00060

Industry Canada Library Queen

JUL 2 1 1998

Industrie Canada Bibliothèque Queen

Submitted By

Professor Samy Mahmoud (Principal Investigator), and

Professor Cyril Leung

Department of Systems Engineering and Computing Science

Carleton University

March, 1980

#### **ABSTRACT**

Integration of Voice and Data Communications over land mobile radio channels is regarded as a promising approach towards efficient spectrum utilization. The research reported here represents a step towards achieving such integration in a digital land mobile radio system. Four aspects have been investigated: (1) the use of forward error correction schemes for data messages to improve channel throughput in the face of fading conditions, (2) the implementation of low power microprocessor controller for integrated mobile terminals, (3) testing the performance of two modulation systems (DPSK and FFSK) for transmitting data at speeds of 9.6 kb/sec. and 16 kb/sec. under simulated fading conditions, and (4) the construction of a TFM modulator which will be tested later to compare the performance of this technique to that of the FFSK technique in fading channels.

# ACKNOWLEDGEMENTS

First of all, we would like to express our gratitude to Mr. J. Da Silva and Dr. H.M. Hafez of the Department of Communications, Ottawa for their support throughout this work. Our thanks also go to Mr. R. Matyes and Mr. D. Wohlberg of the Communication Research Centre, Ottawa for making available the FFSK Modem used in our experiments. Last but not least we would like to thank Mr. P. Manashe and our students A. Amakom and A. Lam for their concerted help in this research.

#### Table of Contents

#### 1. Introduction

- 1.1 Integration of Voice and Data over Mobile Radio Networks

- 1.2 Objectives of Current Research

- 1.3 Structure of the Report

- 1.4 References

- 2. Error Control for Random-Error and Rayleigh Fading Channels

- 2.1 Introduction

- 2.2 Effect of Forward Error Correction on Mean Wasted Time

- 2.3 Effect of Forward Error Correction on Mean Time to Successful Transmission

- 2.4 Concluding Remarks

- 2.5 References

- 3. Design and Implementation of Low Power Microprocessor

- 3.1 Introduction

- 3.2 Architecture of the CMOS Microprocessor

- 3.3 Implementation of the Microprocessor Board

- 3.4 Testing and Performance

- 3.5 Future Improvements

- 4. Measurements and Results

- 4.1 Introduction

- 4.2 DPSK Modern Experimental Set-up and Results

- 4.3 Measurements of the FFSK Modem Set

- 4.4 Non-Recursive Implementation of a Tamed Frequency Modulator

- 4.5 The Fading Signal Simulator

- 4.6 References

- 5. Summary and Future Research

- 5.1 Summary

- 5.2 Future Research

# Table of Contents (cont'd)

Appendix A: A Sample of Microprocessor Test Routines

Appendix B: Microprocessor Board Component Description

Appendix C: DPSK Modem Circuit Diagram

Appendix D: Important Circuit Details for TFM Modulator

#### CHAPTER 1

#### Introduction

The use of land mobile communications channels has so far been largely confined to voice communications. However, recent years have witnessed a rapid growth in the need for data communications mobile systems. Such a demand on the scarce frequency spectrum resource has motivated the search for new techniques to achieve better utilization of the radio frequency spectrum.

It is predicted that the demand for data transmission on mobile radio channels will be steadily increasing over the current decade. Examples of the applications demanding such a service include automatic vehicle location systems, control of channel assignment in cellular systems, police applications, taxi and other dispatch systems. As an indication of the expected demand, it is anticipated that a large fraction of the 350,000 radio users which constitute the Canadian private mobile radio community will add to their system a data transmission capability in the next five years.

The congestion of the available spectrum, coupled with the growing demand for mobile data transmission motivates the search for feasible techniques for integrating speech and data within a single land mobile radio channel. Attempts to investigate such techniques for general data networks have been published recently [1, 2, 3, 4]. The remaining sections of this chapter explore such techniques and serve as an introduction to the research effort intended to accomplish the objective of integrating

voice and data communications over mobile radio channels.

### 1.1 Integration of Voice and Data Over Mobile Radio Networks

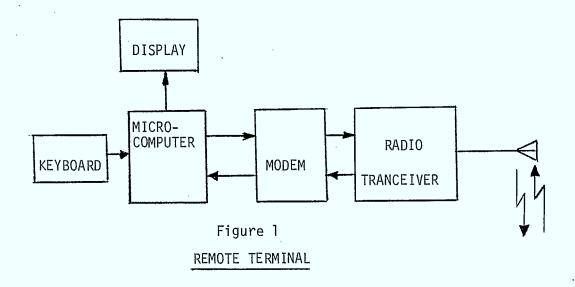

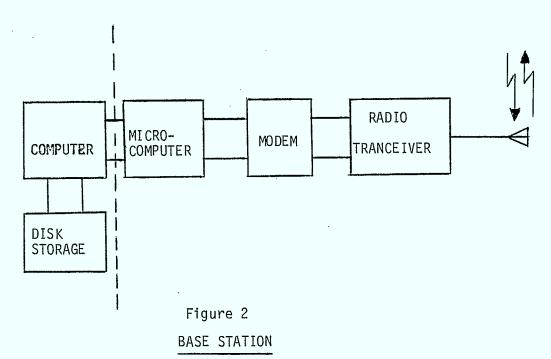

In existing commercial mobile communications systems, data messages and speech are transmitted on separate dedicated channels. Voice communications (mobile telephone) is carried out using frequency modulation techniques. This led to the standardization of the transmitter/receiver units in which FM channels have 30 KHz bandwidth. The need to transmit data messages over mobile communications systems was accommodated by using an IF modulation technique (e.g. DPSK) for the input data messages. The output of the IF stage is then inserted in the audio input section of the FM transmitter unit. Figures 1 and 2 illustrate the components of mobile data terminals and a fixed base station. Data buffering and transmission is controlled by a microcomputer unit which interfaces serially with the modem.

The above technique places severe limitations on the speed of data transmission since the spectrum of the IF signal has to be limited to the bandwidth of the audio input of the transmitter. Increasing the speed of the input signal will lead in this case to higher bit error rates. In random access techniques, the transmission of messages at low rate increases the probability of errors and message retransmissions, which leads to rapid deterioration of the throughput performance of the channel. As well, the scarcity of the available spectrum resources makes it difficult to satisfy the increasing demand for mobile data communications.

Recent research in the speech communications field indicates the existence of gaps between talk spurts of average durations ranging from 0.6 to 1.2 m.sec, depending on the applications. The channel becomes idle

during these gaps. Transmission of voice and data simultaneously over the same channel can obviously be made possible by transmitting data packets during the silent intervals of the channel which is used primarily for voice communications.

Assuming data packet lengths ranging from 1000 to 2000 bits (as is the case in most applications), it is possible to fit these packets into the silent intervals of the channel using appropriate transmission rates. This is feasible at transmission rates of 8 k.bits/sec or higher.

The realization of the above scheme in mobile radio applications is feasible only under the following conditions:

- (1) The availability of low cost modem sets that can transmit data at rates higher than 8 k bits/sec over 30 KHz channels with low BER.

- (2) The availability of accurate speech detector in voice terminals so that the carrier is suppressed when no input speech is detected.

- (3) The ability of the data terminals to sense the voice carrier on the channel to determine if the shannel is busy (talk spurt) or free (gap). The data terminal will transmit its packet only when a gap is detected.

Integration of voice and data transmissions in existing mobile communications systems will require the use of different modulation technique in RF band for the data signals. This is needed since data transmissions will be an 'added on' service to an existing FM mobile communications system.

The objective of the on-going research report here is to construct an all digital voice/data mobile communications systems for the 800 MHz

frequency band. Thus the same modulation technique is used for both voice and data signals. To explain the general concept of such a system, we consider the general structure of the base station and each mobile unit.

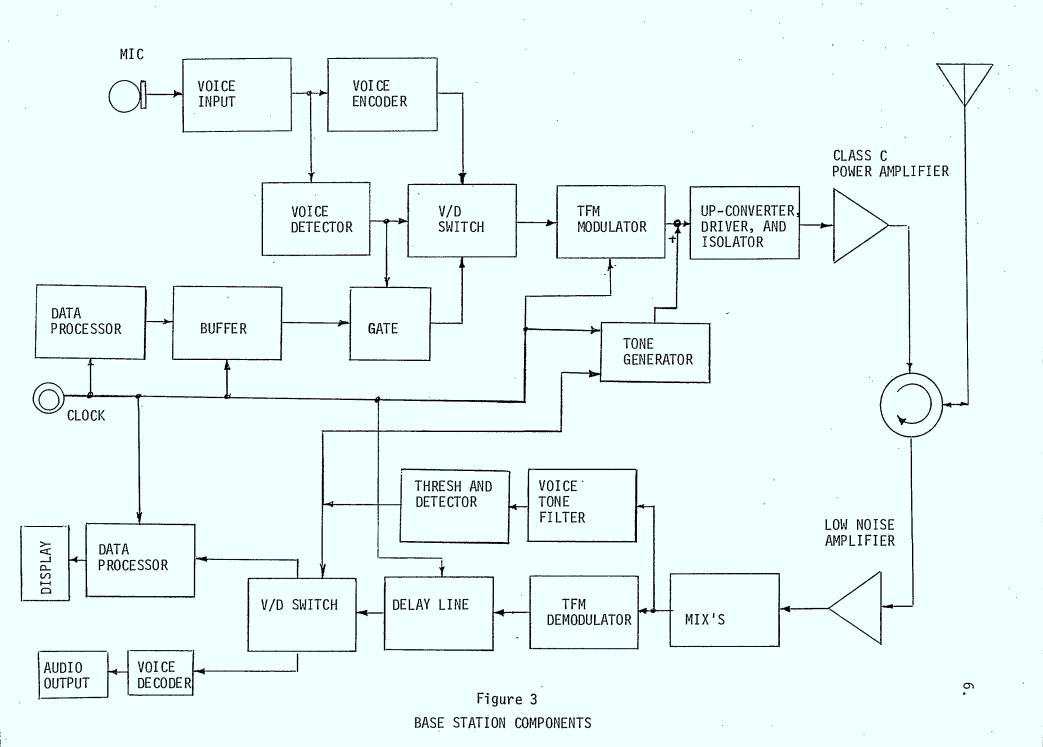

#### The Base Station:

Figure 3 illustrates the basic components of the base station. When a speech signal is transmitted to over a channel the station adds to it a narrow band tone and a clock signal. When a data signal is transmitted, only the clock signal is added to it (in the frequency domain).

#### The Mobile Station:

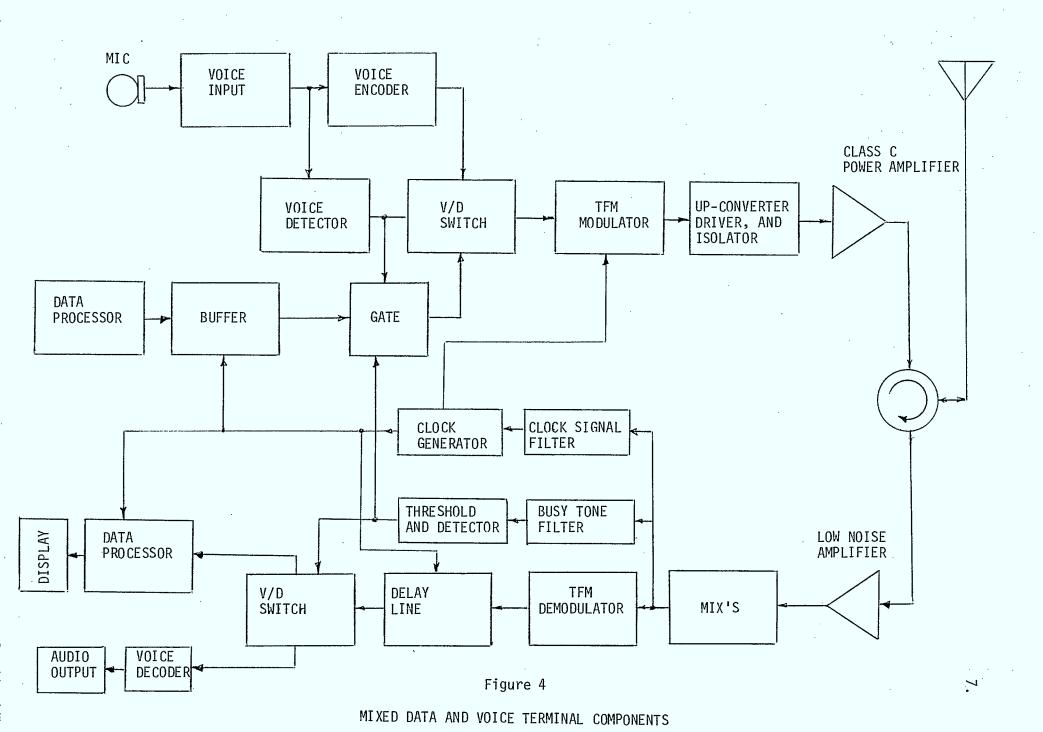

Figure 4 illustrates the basic components of each mobile unit.

The mobile transmits speech signals after the channel is assigned to it by the base station. The mobile unit transmits data packets only after it senses the carrier on the channel and determines, by examining the busy tone, if the channel is busy or free. The speech detector is used to suppress the mobile carrier when it is not transmitting in the speech mode.

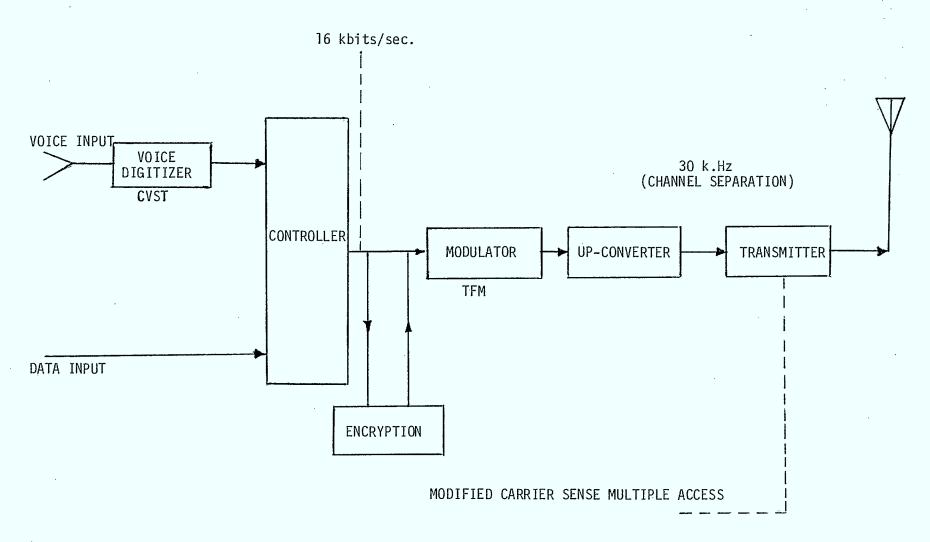

Figure 5 illustrates the structure of the mobile terminals proposed for future research. The voice encoder/decoder circuit will be implemented using the CVSD technique and voice will be digitized at 16 k bits/sec. The modem set to be used will be based on the TFM technique, which will be discussed in section 4.4

## 1.2 <u>Objectives of Current Research</u>

The ultimate objective of the research reported here is to demonstrate, both theoretically and practically, the feasibility of integrating speech and data transmissions over mobile radio channels. Such an integration will lead to better utilization of the available frequency

Figure 5

PROPOSED EXPERIMENTAL MOBILE TERMINAL

spectrum and provide flexibility in channel use for applications involving voice and data communications. The research reported here can be considered as a step in the progress towards achieving the final objective. Specifically, three research aspects have been addressed:

- (1) Improvement of channel throughput delay performance with respect to packet data traffic;

- (2) Design and implementations of low power, small size micropower controller units; and

- (3) Measurement of the BER performance of specific modulators under simulated fading conditions.

The following is a summary of the research conducted in each of the above three aspects.

## 1.2.1 Improvement in Throughput of Packet Data Traffic

The poor throughput-delay performance of random access channels is attributed to the loss of data packets due to collisions or noise and the increase in the total traffic input resulting from packet retransmissions. When fading effects are taken into account, the number of packets received in error increases, which leads to further deterioration of the performance of the channel. One approach for improving the throughput - delay characteristics is accomplished through the use of forward error correction schemes. By correcting some of the packets received in error, the total number of retransmissions will be reduced, leading to improvement in the throughput-delay performance of the channel. Chapter 2 of this report examines the result of investigating the applicability of forward error correcting codes to random access channels under fading conditions.

## 1.2.2 Design of Mobile Radio Terminals

It is apparent from the discussion of section 1.1 that the controller of the mobile terminals will be performing a number of time critical functions. In practice, microprocessors are used as controller units. However, microprocessor boards that are based on I<sup>2</sup>L technology tend to have high power consumption and relatively large size, two factors that mitigate against using them in portable mobile terminals. The power consumption and size of the microprocessor board can be substantially reduced by using the CMOS technology. In this research, a general purpose CMOS microprocessor board has been designed, implemented and tested for mobile terminal functions. This board will be used as the controller unit of the mobile terminals that will be deployed in future field experiments. The design, implementation and testing of the microprocessor board are discussed in Chapter 3.

# 1.2.3 BER Performance of Two Modulation Systems Under Fading Conditions

As mentioned earlier, fading and multipath effects introduced errors to digital signal transmitted over radio channels. In data transmissions, such errors will lead to frequent retransmissions and subsequent deterioration in the throughput - delay performance of the channel. In the transmission of digitized voice, such errors will adversely affect the quality of the received speech, particularly if the voice if encoded at low sampling rates. In this research, two modulator/demodulator sets have been tested to determine the effects of fading signals on the BER of each set. Both sets have been used previously in experimental mobile radio systems as explained in Chapter 4.

### 1.3 Structure of the Report

The remaining chapters of this report are organized as follows:

Chapter 2 examines the distribution of packet transmission

errors introduced by channel fading conditions. Forward error correction

methods are applied and their performance is examined. The feasibility

of using forward error correction to enhance the performance of random

access techniques is discussed in the conclusions of the chapter.

Chapter 3 reports the design implementation and testing of a CMOS microprocessor which has much lower power consumption and smaller volume relative to an  $\rm I^2L$  microprocessor (INTEL 8020) with comparable functional capabilities.

Chapter 4 reports the results of testing the BER of two digital modulation systems in the existence of fading signals and receiver (Gaussion) noise. The first system is based on the DPSK modulation technique and the second system is based on the FFSK modulation technique. A tamed frequency modulator (TFM) circuit implementation is also reported in this chapter.

Finally, Chapter 5 contains concluding remarks and an outline for the future continuation of the research reported here.

## 1.4 References

- [1] E. Arthurs and B.W. Stuck, "A Theoretical Traffic Performance Analysis of an Integrated Voice-Data Virtual Circuit Packet Switch", IEEE Transactions on Communications, 27(7), pp. 1104-1111, July 1979.

- [2] C.J. Weinstein, M.L. Malpass and M.J. Fischer, "Data Traffic Performance of an Integrated Circuit and Packet Switched Multiplex Structure", International Conference on Communications, pp. 24. 3-1 to 24.3-5, Buston, Mass., 1979.

- [3] M.J. Ross, A. Tabbot, J.W. Waite, "Design Approaches and Performance Criteria for Integrated Voice/Data Switching", Proc. IEEE, 65(9) pp. 1283-1295, September 1977.

- [4] A. Pan, "Integrating Voice and Data Traffic in a Broadcast Network Using Random Access Scheme", International Conference on Computer Communications, pp. 551-556, Kyoto, Japan, September 1978.

#### CHAPTER 2

# ERROR CONTROL FOR RANDOM-ERROR AND RAYLEIGH FADING CHANNELS

#### 2.1 Introduction

Error detection and retransmission schemes are quite commonly used in many data communications because they can provide high reliability at a small cost [1,2]. Such schemes are particularly effective when the probability of a retransmission  $P_r$  is small. However, as the channel error rate (and therefore  $P_r$ ) increases, they yield lower and lower throughput. To preserve an acceptable throughput, various techniques can be used, such as diversity transmission or coding.

In this chapter the use of random and burst error correcting codes in improving the performance of a stop-and-wait Automatic Repeat-Request (ARQ) scheme over random-error and Rayleigh Fading channels is investigated. Two models are examined. The first model is similar to the one in [1] and is used to analyze the effect of forward error correction on the mean wasted time. The second model assumes a Poisson arrival process for fixed length messages and determines the effect of forward error correction on the mean time between the arrival of a message and its successful transmission.

## 2.2 <u>Effect of Forward Error Correction on Mean Wasted Time</u>

In this section, a model of a stop-and-wait ARQ scheme similar to [1] is used to examine the reductions in the mean wasted time obtainable by the use of forward error correcting codes. Two channel models, one with random errors and the other with Rayleigh fading, are considered.

We assume that measages have random lengths L which are geometrically distributed, i.e.

$$P_1(\ell) = pq^{\ell-1}, \ \ell = 1,2,3 \dots; \ q = (1-p)$$

(1)

with average length  $\overline{L}=\frac{1}{p}$ . The message is split into blocks of size B bits. These are then assembled into packets of length (B+b) bits, where b represents overhead required for synchronization, addressing, error detection, etc. The mean number of packets per message is given by

$$\overline{N}(B) = \sum_{n=1}^{\infty} n \cdot P([n-1]B < L \le n B)$$

$$=\sum_{n=1}^{\infty} n \sum_{\ell=(n-1)B+1}^{nB} pq^{\ell-1}$$

$$= \frac{1}{(1-q^B)} \tag{2}$$

Let  $P_e(B+b)$  denote the probability that the transmitted packet will be received incorrectly. We assume that the error-detection code is able to detect all errors [3]. Of course,  $P_e(B+b)$  depends on the channel noise characteristics.

In the stop-and-wait transmission scheme, the transmitter sends a packet and waits for an acknowledgement from the receiver. If a positive acknowledgement is received (indicating the packet was successfully received), the sender proceeds to send a new packet. Otherwise, the transmitter repeats the same packet until it receives a positive acknowledgement. Throughout this chapter, the acknowledgement delay is assumed to be a con-

stant, denoted by A.

There is a trade-off involved in selecting the packet size. On the one hand, it is desirable to choose a large packet size so as to reduce the acknowledgement delay. On the other hand, a long packet is more likely to be corrupted by the channel, and hence require a retransmission. Also, in the case where the unused portion of the last packet of a message is filled with dummy bits, a long packet results in more waste. This can be avoided by using an end-of-message character.

Assuming that an error in the transmission of a packet is independent of that of any other packet transmission and that the last packet is filled with dummy bits, it can be shown [1] that the expected wasted time (i.e. the difference between the actual time for transmitting the packetized message and the time it would take to directly transmit the (unpacketized) message over an error-free channel with the same baud rate) is given by

$$\overline{W}(B) = \frac{1}{(1-q^B)} \left[ \left( 1 + \frac{P_e(B+b)}{1-P_e(B+b)} \right) (A+T) \right] - \frac{\overline{L} + b}{R}$$

(3)

where R = channel baud rate in bits/sec

$$T = \frac{B+b}{R}$$

= packet transmission time in sec.

We now consider the effect of forward error correction on the mean wasted time as described by equation (3). The use of an error-correcting code involves a trade-off: On the negative side, parity-check bits representing additional overhead have to be used; however this may be more than offset by the reduction in the probability of a packet retransmission  $P_r$ .

The choice of an error-correcting code  ${\cal C}$  and its effect on the

mean wasted time is now examined. We confine our attention to Bose-Chaudhuri-Hocquenghem (BCH) codes [4,5]. For a given packet length n, (preferably of the form  $n=2^m-1$ , m=2,3,4, ... corresponding to the codeword lengths of BCH codes), we obtain the distribution of the number of channel errors in the packet. This can be derived analytically for the random-error channel. For the Rayleigh fading channel, simulations were used to obtain the desired distribution.

From this distribution, we can determine the number of bit errors t that should be corrected for a given packet retransmission probability  $P_r(n)$ . Of course, the smaller  $P_r(n)$  is, the larger t will be. The number of parity-check bits p required to correct these t errors can be easily determined from BCH code parameters [5]. By comparison with equation (3), the resulting expression for the mean wasted time is

$$\overline{W}_{C}(n,p) = \frac{1}{\left(1-q^{-n-(b+p)}\right)} \left[ \left(1 + \frac{P_{r}(n)}{1-P_{r}(n)}\right) (A+T) \right] - \frac{\overline{L}+b}{R}$$

(4)

where  $T = \frac{n}{R}$  = packet transmission time in seconds.

# 2.2.1 Numerical Results for the Random-Error Channel

The distribution of the number of bit errors  $\,N\,$  in a packet of length  $\,n\,$  sent over a random-error channel is given by

$$P_{\text{random}}(n,N) = {n \choose N} p_b \left(1-p_b\right)^{N-N}$$

(5)

where  $p_b$  is the bit error rate. We assume  $p_b = 10^{-2}$ .

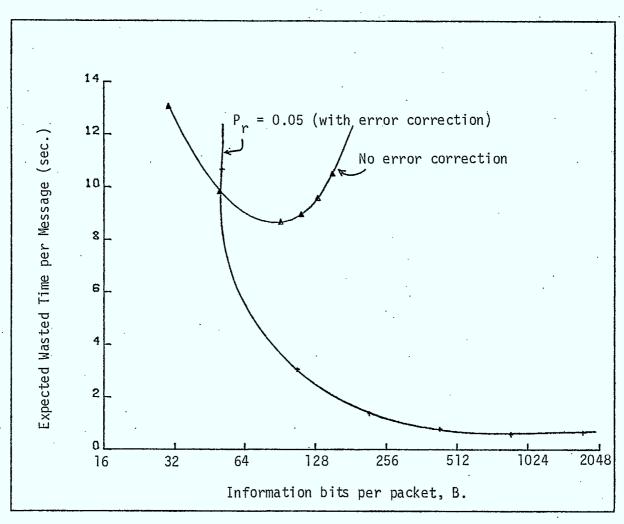

Letting  $P_e(B+b) = 1 - P_{random}(B+b, 0)$  in equation (3), the expected wasted time for  $\overline{L} = 1000$ , 2000 and 5000 bits was calculated as a function of B.

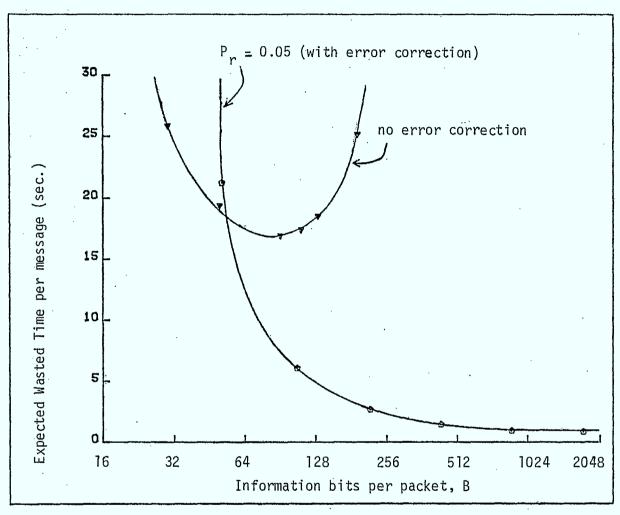

The results are plotted in figures 6, 7 and 8 (curves labelled no error correction). For each value of  $\overline{L}$ , there is an optimal value of B which minimizes the expected wasted time as suggested by the discussion at the beginning of section 2.2. BCH random error correcting codes were then used to correct enough channel errors say t to ensure that the probability of retransmission  $P_r$  is no larger than 0.05. The codes used for various packet lengths are given in table 1.

| packet length n | BCH (n,k,t) code used to achieve P <sub>r</sub> < 0.05 |  |

|-----------------|--------------------------------------------------------|--|

| 255<br>511      | (255, 215, 5)<br>(511, 430, 9)                         |  |

| 1023            | (1023, 863, 16)                                        |  |

| 2047            | (2047, 1739, 28)                                       |  |

TABLE 1: BCH Codes Used for Random-Error Channel

We then use equation (4) to calculate the corresponding expected wasted times. The results, shown in figures 6, 7 and 8, indicate that error-correction can substantially reduce the expected wasted time. For example, figure 7 shows that with error-correction, the minimum expected wasted time is reduced from about 17 seconds to 0.8 second.

### 2.2.2 Numerical Results for the Rayleigh Fading Channel

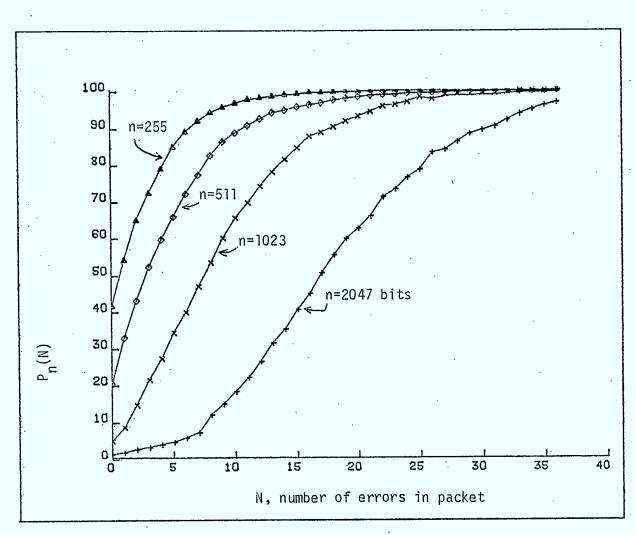

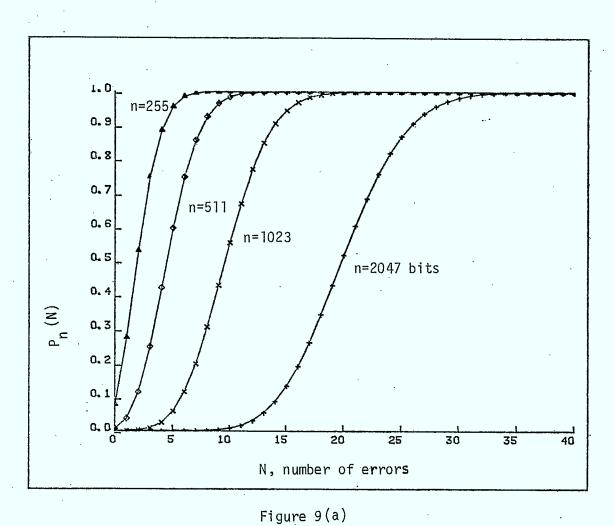

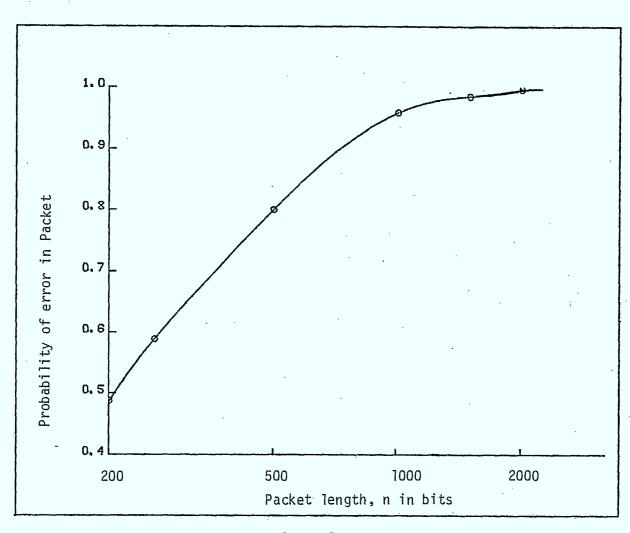

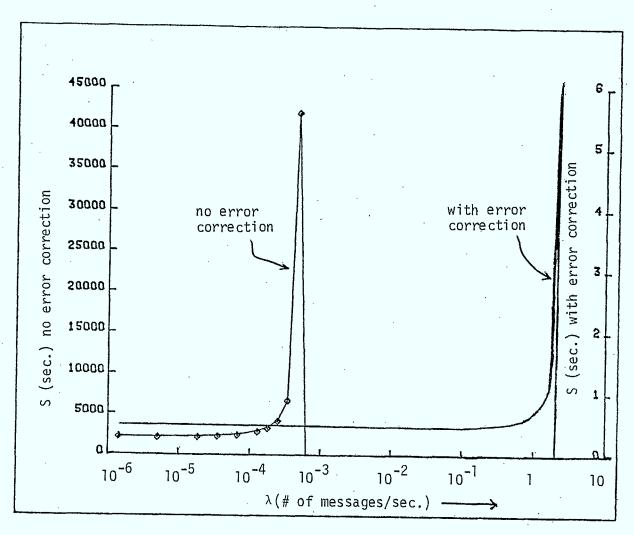

To obtain the distributions of the number of channel errors in packets of various lengths, a simulation program was written [6,7]. The results are displayed in figure 9 which gives the cumulative distribution function (CDF) of the number of errors in packets of lengths 255, 511, 1023 and 2047 bits. A channel bit error rate  $\rm p_b$  of  $10^{-2}$ , a channel rate of 4000 bits/sec, a Doppler frequency  $\rm f_D$  of 25.5 Hz (corresponding to a vehicle speed of 20 MPH and carrier frequency of 850 MHz) and non-coherent FSK modulation were assumed. Fig. 10 shows the probability of getting one or more bit errors as a function of the packet length.

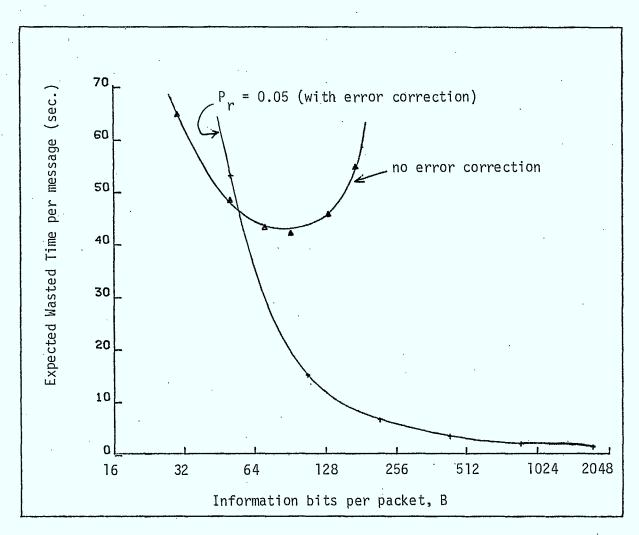

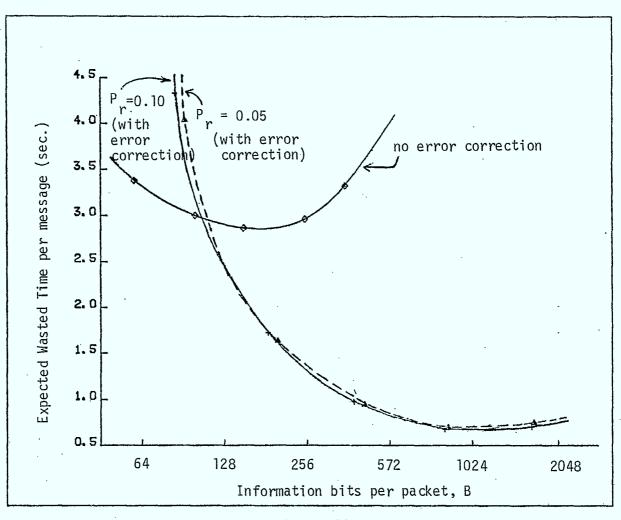

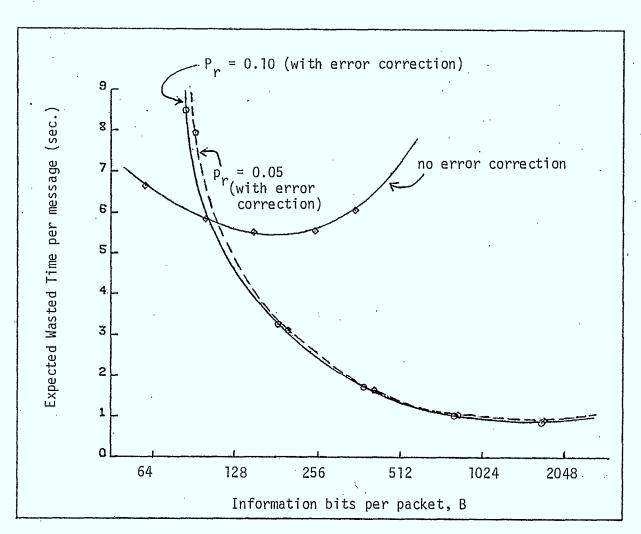

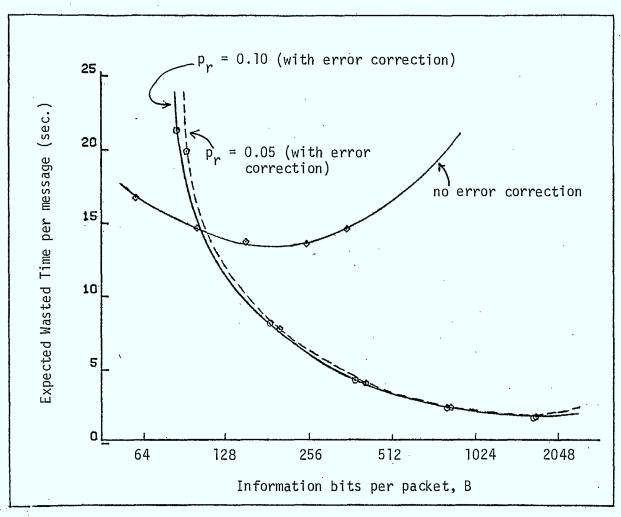

Using fig. 10, equation (3) was evaluated as a function of B for  $\overline{L}$  = 1000, 2000 and 5000 bits. The results are shown in figures 11, 12 and 13(curves labelled no error correction). It can be seen that for each value of  $\overline{L}$  there is an optimal value of B which minimizes the expected wasted time.

BCH random error correcting codes were then used to correct enough channel errors say  $\,$ t to ensure that the probability of retransmission was no larger than 0.05 (or 0.1). The choice of the code to be used is made based on the packet length  $\,$ n and  $\,$ t (see table 2). Equation (4) was then used to calculate the corresponding expected wasted times. The results are shown in Figs. 11, 12 and 13. They show that the use of error-correction gives a substantial reduction in the expected wasted times. For example, Fig. 12 shows that with error-correction, the minimum expected wasted time per message is reduced from about 5.5 seconds to about 1 second. Similar improvements were found for  $\overline{L}$  = 1000 and 5000 bits.

| Packet Length              | BCH (n,k,t<br>P <sub>r</sub> =0.05                                 | ) code used<br>P <sub>r</sub> =0.1                                  |

|----------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------|

| 255<br>511<br>1023<br>2047 | (255, 187, 9)<br>(511, 376,15)<br>(1023, 808,22)<br>(2047,1662,35) | (255, 199, 7)<br>(511, 412, 11)<br>(1023, 838,19)<br>(2047,1695,32) |

| 2047                       | (2047,1662,35)                                                     | (2047,1695,32)                                                      |

TABLE 2: BCH Codes Used for Rayleigh Fading Channel

# 2.3 <u>Effect of Forward Error Correction on Mean Time to Successful</u> Transmission

In this section, we examine the same stop-and-wait scheme of the previous section from a different view point. Messages of fixed lengths (the case of variable lengths is being developed) are assumed to arrive at the transmitter according to a Poisson process. Messages are transmitted on a first-in, first-out basis. The effect of using error-correcting codes on the mean time S between the arrival of a message and its successful transmission (i.e. positive acknowledgement sent back by the receiver) is examined.

Using the Pollaczek-Khinchin mean value formula for M/G/1 queues [8], we obtain

$$S = \frac{1}{\mu} \left[ 1 + \frac{\frac{\lambda}{\mu} (1 + \mu^2 \sigma_b^2)}{2(1 - \frac{\lambda}{\mu})} \right]$$

(6)

where  $\lambda = arrival rate$

$\frac{1}{\mu}$  = mean service time

$\sigma_b^2$  = variance of service time

For the stop-and-wait scheme, the distribution of the number of transmissions D required till a message (packet) is successfully transmitted (assuming independent transmissions) is given by

$$P(D=i) = (1 - P_r) P_r^{i-1}, i = 1, 2, 3, \dots$$

(7)

The mean and variance of the distribution of (7) is given by

$$\bar{D} = \frac{1}{1 - P_n} \tag{8}$$

$$Var D = \frac{P_r}{(1-P_r)^2}$$

(9)

Each transmission (and acknowledgement) takes (A + T) seconds. Therefore in equation (6),

$$\frac{1}{\mu} = \frac{1}{1 - P_{\kappa}} (A+T) \tag{10}$$

$$\sigma_{b}^{2} = \frac{P_{r}}{(1 - P_{r})^{2}} (A + T)^{2}$$

(11)

# 2.3.1 Numerical Results for the Random-Error Channel

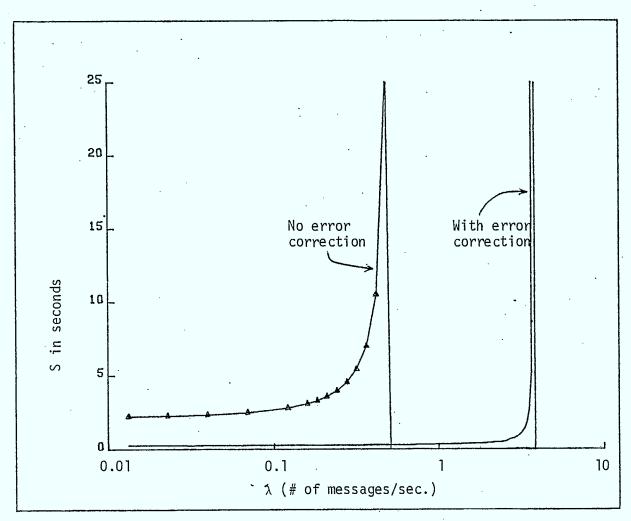

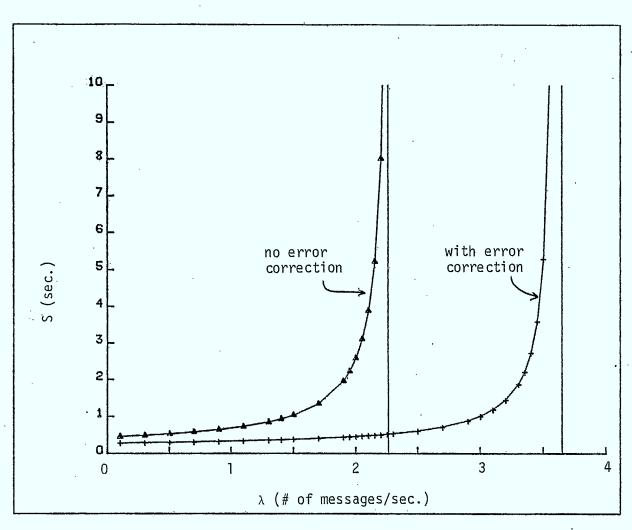

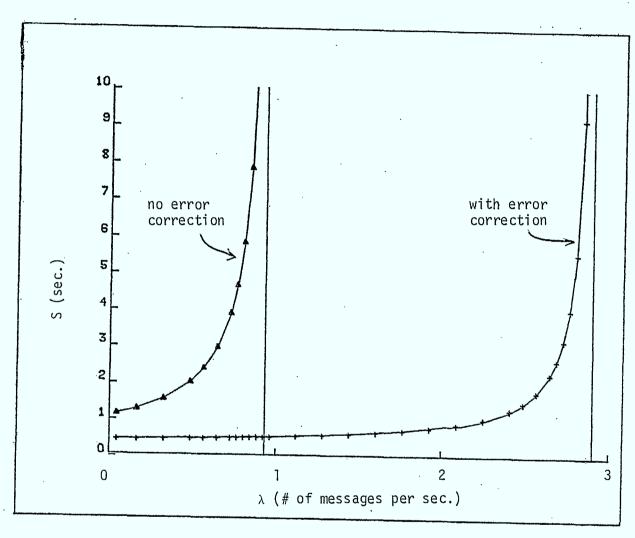

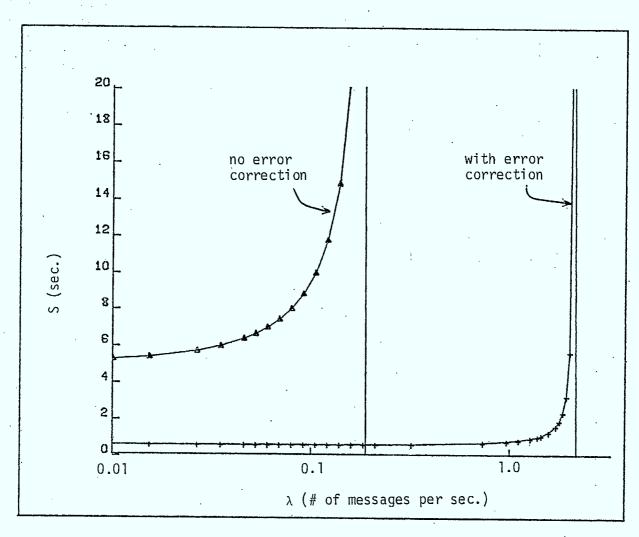

For packet lengths n = 255, 511 and 1023, the BCH codes used to achieve a probability of retransmission  $P_r \le 0.05$  can be obtained from table 1. Equation (6) can then be used to determine S when error correction is used, assuming A = 0.2 sec and T =  $\frac{n}{4000}$  sec. Plots of S against the arrival rate  $\lambda$  are shown in figs. 14, 15 and 16 for B = 185, 400 and 833 bits (b = 30 bits assumed). The number of information bits B in a packet is of course n - b - p.

With no error correction, the packet lengths n' would be given by n' = 215, 430 and 863 bits. The corresponding  $P_r$  is determined from equation (5). As before, equation (6) is then used to calculate S. The results are plotted in figs. 14, 15 and 16 (curves labelled no error correction), and show that for a given arrival rate  $\lambda$ , S can be significantly reduced using forward error correction. Also the maximum (asymptotic) value of  $\lambda$  is increased with error correction, e.g. in figure 15,  $\lambda_{max}$  increases from 0.04 to 2.85.

### 2.3.2 <u>Numerical Results for the Fading Channel</u>

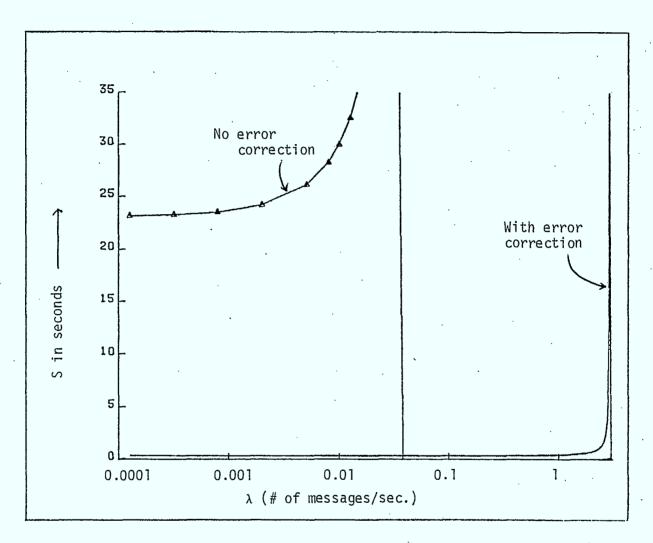

From table 1, we know the BCH codes to be used for achieving a value of  $P_r \le 0.05$  for packet lengths n = 255, 511 and 1023. Assuming a transmission rate of 4000 bits/sec, the transmission time  $T = \frac{n}{4000}$  sec. This together with an acknowledgement delay A of 0.2 sec were used to determine S in equation (6). The results are shown in figures 17, 18 and 19.

If no error correction was used, the packet lengths n' would be given by n' = 187, 376 and 808 respectively. The corresponding  $P_r$  can be determined from fig. 10. As before this was used together with  $T = \frac{n'}{4000}$  sec, and A = 0.2 sec in equation (6) to solve for S. The results are shown in figures 17, 18 and 19 (curves labelled no error correction) and indicate that performance is substantially enhanced by using error correction. As an example, in figure 18 with error correction, the maximum (asymptotic) value of  $\lambda$  is increased from 0.94 to 2.9.

#### 2.4 Concluding Remarks

The results obtained in the last two sections indicate that the use of error-correcting codes can lead to significantly better system performance in a stop-and-wait ARQ scheme. In practice this improvement has to be weighed against the cost and complexity of using the error-correcting code. The results presented so far used BCH codes as random error-correcting codes. These can also be used as burst-error-correcting codes for the fading channel [9]. However we consistently found that using the BCH code in a random-error-correcting mode yielded a higher fraction of correctable packets. This agrees with the general conclusion in [10] based on actual channel error measurements on a mobile radio channel. It might be pointed out however that decoders for burst error correction are simpler and less expensive.

We conclude this chapter with a few remarks about other methods for improving the transmission of data over fading channels. Bit interleaving [5] may be used to disperse the errors that occur in "bursts" when the received signal fades. As the degree of interleaving increases, the fading channel packet error distribution approaches that of the random error channel. Therefore as indicated by the results in section 2.2.1, bit interleaving coupled with (random) error correction can be quite effective. It should be noted however that with bit interleaving, a packet is received essentially only when all interleaved packets have been received.

Another technique for combatting the fades on a Rayleigh-fading channel is diversity transmission [11]. In <u>time diversity</u>, the same packet is repeated several times (after some appropriate time interval) in the hope that not all transmissions will be hit by a deep fade. Another common

implementation is <u>space diversity</u> in which several antennas are used to reduce the probability that the received signal at all the antennas will be simultaneously subject to a deep fade. It is planned that space diversity will be used in the Bell System Advanced Mobile Phone Service (AMPS) currently being tested [12].

Figure 6

Expected Wasted Time Against B for random error channel

with  $p_b = 10^{-2}$

R = 4000 bits/sec.

$\overline{L}$  = 1000 bits

A = 0.2 sec.

b = 30 bits

Figure 7

Expected Wasted Time against B for random error channel

with  $p_{b} = 10^{-2}$

R = 4000 kits/sec.

$\overline{L}$  = 2000 bits

A = 0.2 sec.

b = 30 bits

Figure 8

Expected Wasted Time against B for random error channel

with

$$p_b = 10^{-2}$$

$R = 4000 \text{ bits/sec.}$

$\overline{L} = 5000 \text{ bits}$

$A = 0.2 \text{ sec.}$

b = 30 bits

Figure 9

CDF,  $P_n(N)$  of number of errors in packets of lengths n for Rayleigh fading channel with  $p_b$  =  $10^{-2}$ ,  $f_D$  = 25.5 Hz and transmission rate R = 4000 bits/sec.

CDF,  $P_n(N)$  of number of errors in packets of lengths for n Random channel with  $p_b = 10^{-2}$  and transmission rate R = 4000 bits/sec.

Figure 10

Packet error rate as a function of packet length for Rayleigh fading channel with  $p_b = 10^{-2}$ ,  $f_D = 25.5$  Hz, transmission rate R = 4000 bits/sec.

Figure 11

Expected Wasted Time against B for Rayleigh fading channel

with  $p_b = 10^{-2}$

R = 4000 bits/sec.

$\overline{L}$  = 1000 bits

A = 0.2 secs.

b = 30 bits

Figure 12

Expected Wasted Time against B for Rayleigh fading channel

with  $p_b = 10^{-2}$

R = 4000 bits/sec.

$\Gamma$  = 2000 bits

A = 0.2 sec.

b = 30 bits

Figure 13

Expected Wasted Time against B for Rayleigh fading channel

with  $p_b = 10^{-2}$

R = 4000 bits/sec.

$\overline{L}$  = 5000 bits

A = 0.2 sec.

b = 30 bits

Figure 14

Plot of mean time to successful transmission against arrival rate for random error channel

with A = 0.2 sec.

B = 185 bits

$p_b = 10^{-2}$

Figure 15

Plot of mean time to successful transmission against arrival rate for random error channel

with

$$A = 0.2 \text{ sec.}$$

$$B = 400 \text{ bits}$$

$$p_b = 10^{-2}$$

$$R = 4000 \cdot \text{bits/sec.}$$

Figure 16

Plot of mean time to successful transmission against arrival rate for Random Error Channel with A = 0.2 sec.

B = 833 bits

$p_b = 10^{-2}$

Figure 17

Plot of mean time to successful transmission against arrival rate for Rayleigh fading channel

with A = 0.2 sec.

B = 187 bits

$p_b = 10^{-2}$

Figure 18

Plot of mean time to successful transmission against arrival rate for Rayleigh Fading Channel

with A = 0.2 sec.

B = 376 bits

$p_b = 10^{-2}$

Figure 19 .

Plot of mean time to successful transmission against arrival rate for Rayleigh fading channel

with A = 0.2 sec.

B = 808 bits

$p_b = 10^{-2}$

#### REFERENCES

- [1] W.W. Chu, "Optimal Message Block Size for Computer Communications with Error Detection and Retransmission Strategies", <u>IEEE Trans.on Comm.</u>, Vol. COM-22, No. 10, October 1974.

- [2] J.M. Morris, "Optimal Blocklengths for ARQ Error Control Schemes", IEEE Trans. on Comm., Vol. COM-27, No. 2, February 1979.

- [3] S.K. Leung and M.E. Hellman, "Concerning a Bound on Undetected Error Probability", <u>IEEE Trans. on Info. Theory</u>, Vol. IT-22, No. 2, March 1976.

- [4] W.W. Peterson and E.J. Weldon, <u>Error-Correcting Codes</u> M.I.T. Press, 1972.

- [5] S. Lin, <u>An Introduction to Error-Correcting Codes</u>, Prentice Hall, 1970.

- [6] G.A. Arredondo, W.H. Chriss and E.H. Walker, "A Multipath Fading Simulator for Mobile Radio" <u>IEEE Trans. on Comm.</u>, Vol. COM-21, No. 11, November 1973.

- [7] J.I. Smith, "A Computer Generated Multipath Fading Simulation for Mobile Radio", <u>IEEE Trans. on Vehicular Technology</u>, Vol. VT-24, No. 3, August 1975.

- [8] L. Kleinrock, "Queueing Systems", Vol. 1, John Wiley, 1975.

- [9] S.E. Tavares and S.G.S. Shiva, "Detecting and Correcting Multiple Bursts for Binary Cyclic Codes", <u>IEEE Trans. on Info. Theory</u>,

Vol. IT-16, September 1970.

- [10] P.J. Mabey, "Mobile Radio Data Transmission Coding for Error Control", <u>IEEE Trans. on Vehicular Technology</u>, Vol. VT-27, August 1978.

- [11] J.M. Wozencraft and I.M. Jacobs, <u>Principles of Communication</u>

Engineering, J. Wiley, 1965.

[12] G.A. Arredondo, J.C. Feggeler and J.I. Smith, "Voice and Data Transmission", Bell System Tech. Journal, January 1979.

#### CHAPTER 3

# Design and Implementation of Low Power Microprocessor

#### 3.1 Introduction

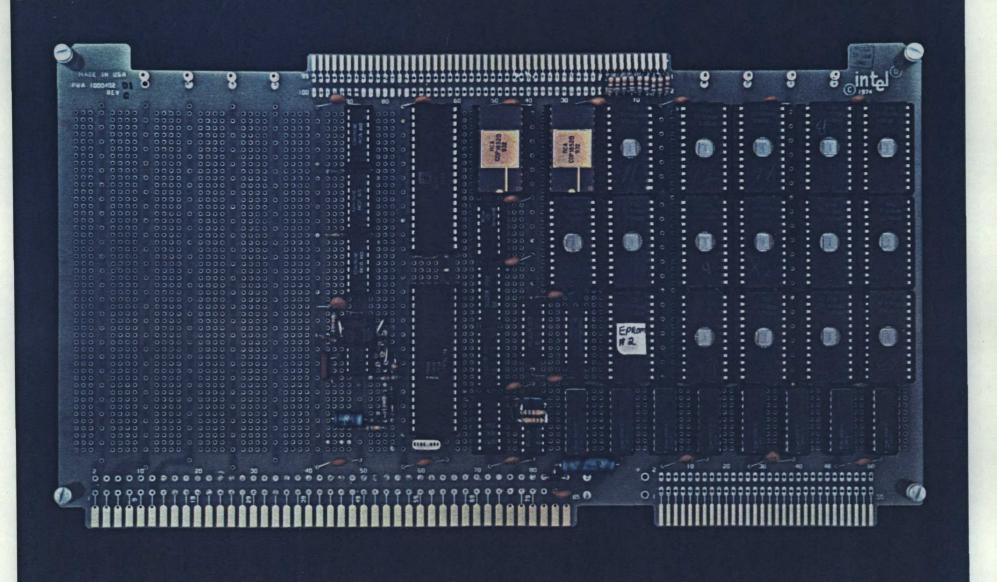

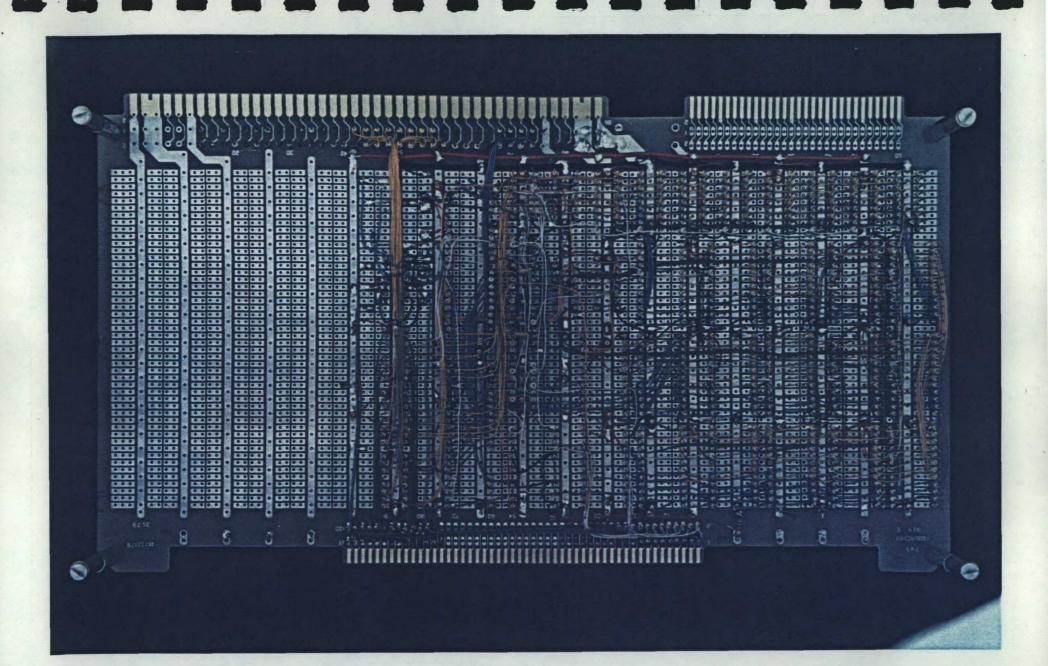

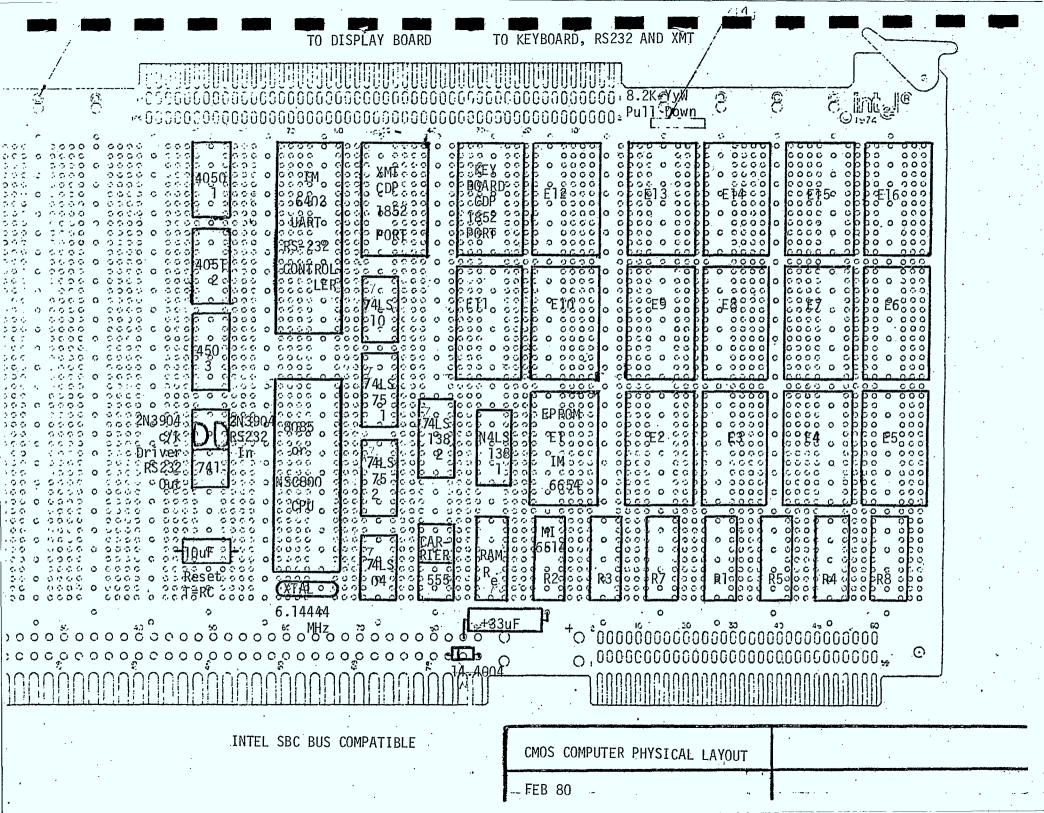

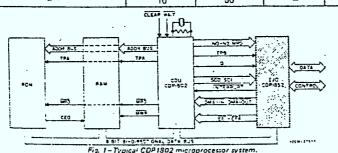

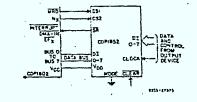

This chapter describes a CMOS microcomputer which was developed as a replacement for the Intel SBC 80/204 CPU board used in portable Packed Radio Terminals. The main design goals were: reduced power dissipation, compatibility with previously developed software code (for the 8080 processor) and small size. The CMOS microcomputer described here contains 8K bytes of EPROM, 4K bytes of RAM, two 8 bit I/O parts, one serial RS-232 port and a CPU. The power consumption was reduced from 33.64W to 0.771W at no loss of performance (compared to Intel SBC 80/204). The only N-MOS part in the whole board is the 8085 CPU. Replacement of this CPU by the National Semiconductor NSC-800 CMOS CPU will result in further reduction of power dissipation to about 0.375W for the whole CPU board.

# 3.2 Architecture of the CMOS Microprocessor

The term <u>computer architecture</u> refers to the programmers' view of a particular machine, i.e. its instruction set, I/O arrangement and register set.

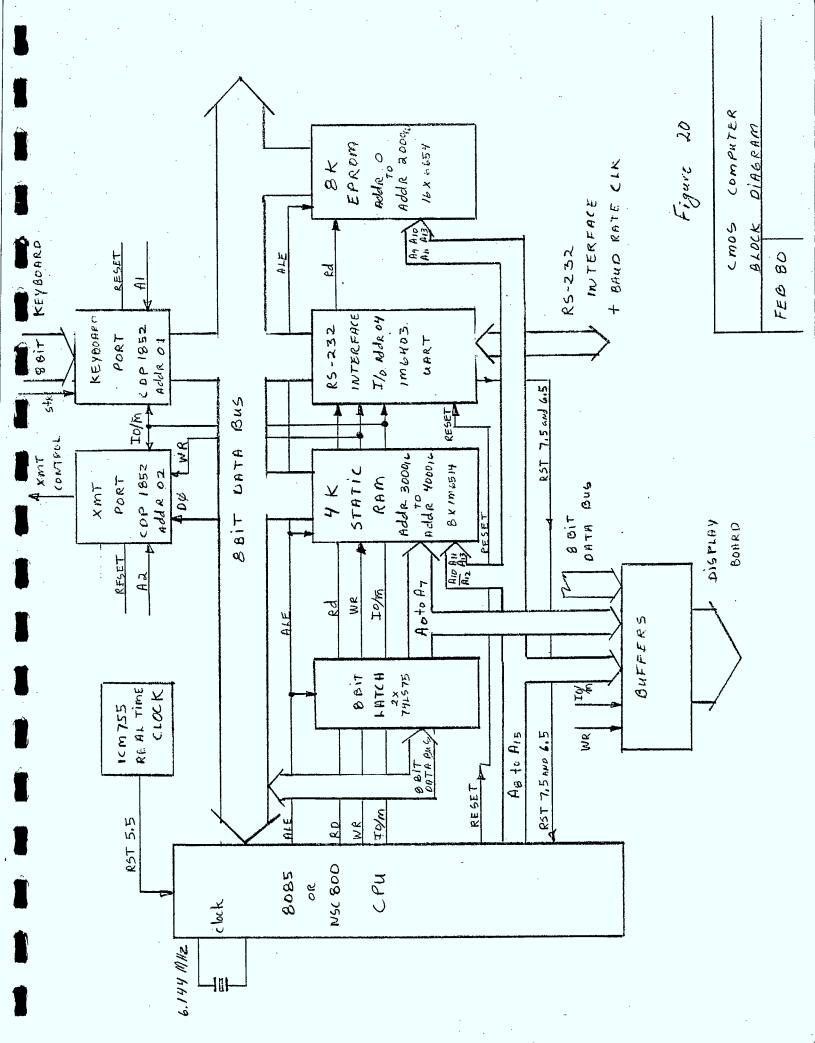

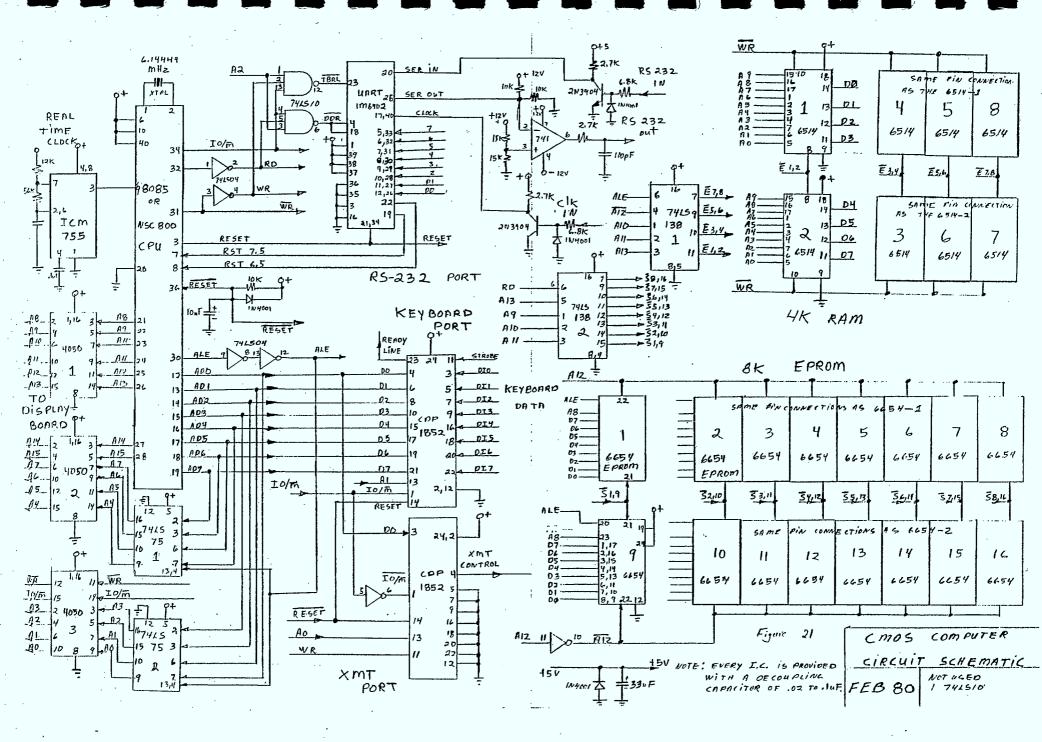

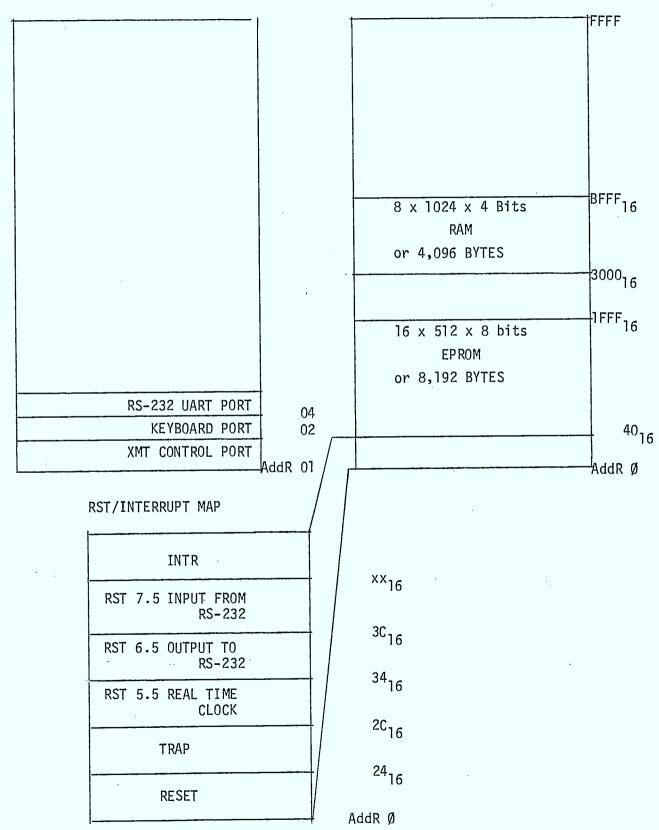

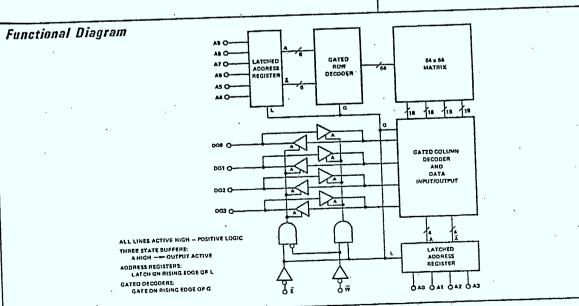

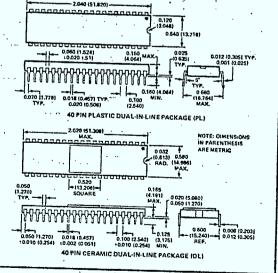

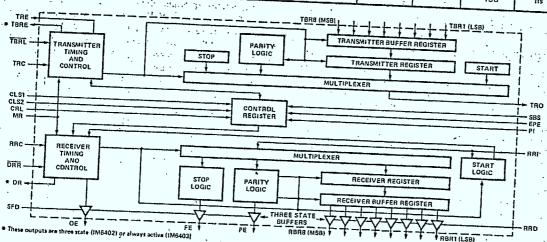

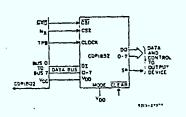

The architecture of the CMOS microcomputer is shown in Figs. 20 and 21. In addition to the CPU, static RAM and EPROM modules, the architecture contains one serial port for interfacing to the modulator/demodulator circuit, and two parallel ports for keyboard interface and radio transmitter control.

The instruction set of the CMOS microcomputer board (8085 CPU) is exactly the same as that of the SBC 80/204. This assures software compatibility between the two CPU boards. The NSC 800 CMOS CPU which will replace

the 8085 CPU used in the CMOS microcomputer has an Z-80 instruction set. The Z-80 instructions are a superset of the 8080 instructions, containing within it all seventy eight 8080 instructions. The NSC 800 CPU will be available in June 1980.

The CMOS CPU board has one serial port, two parallel ports and buffers to interface the display board controller.

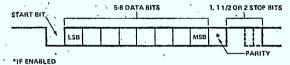

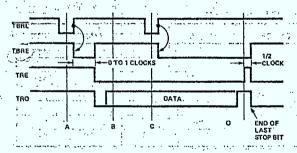

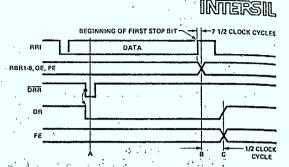

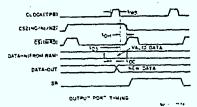

The serial port is interrupt driven for both the transmitter and receiver port. The RS 232 interface enables it to be directly connected to the modem of the Packet Radio Terminal. Both receiver and transmitter clocks are derived from the modem. RS 232 buffers are provided for the clock input.

One of the 8 bit parallel ports is connected as an input from the keyboard, while the other controls the radio transmitter (one bit output).

The display board controller is seen by the CPU as memory locations. Therefore, only buffers were needed to facilitate its connection to the address and data buses of the computer.

The ICM 755 timer is used as a real time clock for process switching. It is connected to interrupt 5.5 of the CPU.

A detailed description of the components used in the microprocessor board is included in Appendix B.

# 3.3 Implementation of the Microprocessor Board

The prototype of the CMOS microcomputer board was implemented on an Intel SBC-905 prototype board. The physical dimensions of that board are the same (12 x 6.75 inches) as the standard SBC 80/204 board size. All the circuitry of the CMOS microcomputer occupies approximately two thirds of the board, leaving enough room for future expansion of memory or I/0. All connections between integrated circuits were wire wrapped. This method of interconnection is very reliable, and allows quick changes needed during prototype development.

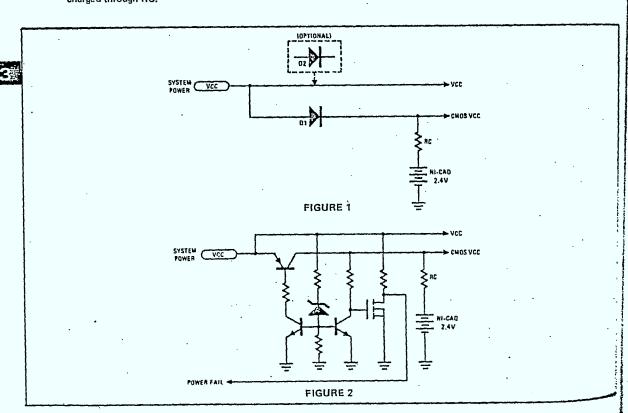

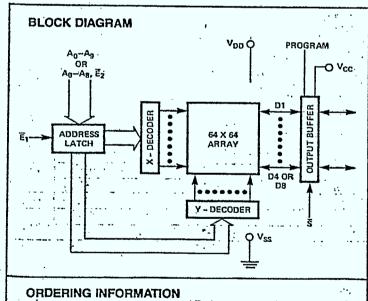

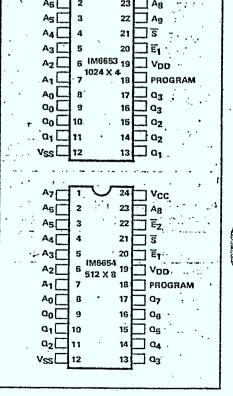

The memory chips used for the RAM memory banks are Harris HM 6514 static  $1024 \times 4$  CMOS RAMS with an access time of 300 nsec. This RAM chip is housed in a 18 pin dual in-line package.

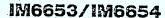

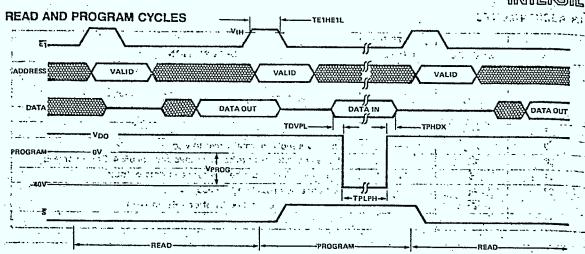

The EPROM section uses the Intersil IM6654 CMOS EPROM. This device has an organization of  $512 \times 8$  bits and is housed in a 24 pin dual in-line package. The programming of the IM6654 EPROMS was done on a Data I/O programmer, using a special personality module. The erasure time for these EPROMS is 30 minutes, using the UVS-11 ultra-violet source.

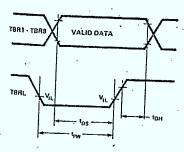

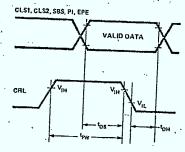

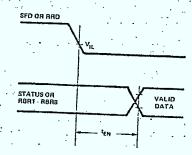

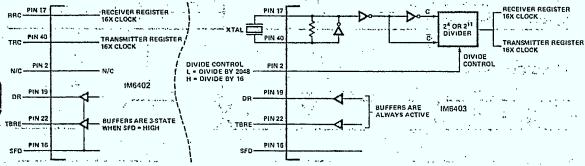

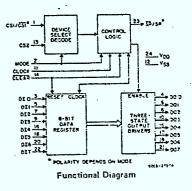

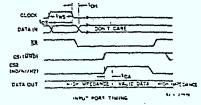

Serial interface uses the Intersil IM6402 UART. This CMOS UART consumes only 10 miliwatts and can operate up to speeds of 200K bits per second. The UART uses an external clock, supplied by the modem. The two parallel I/O ports were implemented using the RCA CDP 1852 eight bit I/O port.

The N-MOS CPU used is the Intel 8085. This CPU runs with a crystal 6.144 MHZ and has four interrupt lines. Two of the interrupt lines are used for the UART transmitter and receiver respectively, the third one is used for the systems clock and the fourth interrupt is used for the keyboard.

The whole microcomputer board, with the exception of the RS 232 interface, runs on single 5V power supply and a current of 135 miliamperes. The RS-232 serial interface requires  $\pm$  12v at 4 miliamperes.

#### 3.4 Testing and Performance

The testing was performed initially with a HP logic analyser up to the point where the CPU was accessing the EPROM memory bank. From that point on, software test routines were used for the testing. These software routines were first burned into the EPROMS and then plugged into the microcomputer where they performed the testing together with the CPU. For this reason, software routines were written and used to test and debug all the EPROM sockets, all the RAM sockets, the parallel I/O ports and the serial I/O port. To verify the proper operation of the serial RS 232 port, a complete I/O routine has been written and a serial communication link with a LA 36 Decwriter has been successfully tested. A sample of the test routines is given in Appendix A.

#### 3.4.1 Speed

The 8085 CPU is running at a clock frequency of 6.144 MHZ. This gives a minimum instruction cycle of 1.3 microseconds.

#### 3.4.2 <u>Power Dissipation</u>

The actual power dissipation was measured in the HALT state and also while the CPU was running a typical program. The program used is shown in Appendix A under the heading of "Memory Test Routine".

The power dissipation under running condition is approximately 50 miliwatts higher than in the stopped state. This is typical of CMOS

circuits. These circuits dissipate negligible power during idle states with the major power dissipation occuring during switching.

#### Power dissipation

|             | <u>5V</u> | <u>+12V</u> | <u>-12V</u> | Total W |

|-------------|-----------|-------------|-------------|---------|

| CPU idle    | 125mA     | 4mA         | 4mA         | 0.721   |

| CPU running | 135mA     | 4mA         | 4mA         | 0.771   |

#### 3.5 Future Improvements

Several improvements are expected to be incorporated in the CMOS microprocessor board in the near future. A summary of these improvements follows:

1. The power dissipation could be drastically reduced (by approximately 0.4 watts) by replacing the Intel 8085 CPU with a National Semiconductor CMOS CPU P/N NSC 800.

This CPU dissipates a mere 0.05 watts, operates at the same speed and has the same pinout as the 8085 CPU.

- 2. Replacement of the 6514 4K RAM chips with the RCA 16K CMOS RAM would reduce the number of RAM chips required from eight to two.

- Using higher density EPROMS would also reduce the chip count.

- 4. The RAM and ROM space (combined) can be enlarged to 64K. The maximum I/O port capability is 256 ports.

- 5. Changing the computer architecture into a pipeline organization would increase the speed of the computer to a point where real time digital signal processing would be possible. Thus some of the modulator/demodulator functions could be incorporated into the CMOS microprocessor. This would

result in further reduction in the total power consumption of the packet radio terminal.

#### CHAPTER 4

#### MEASUREMENTS AND RESULTS

#### 4.1 <u>Introduction</u>

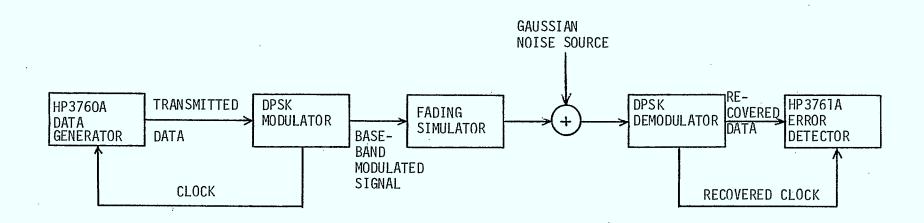

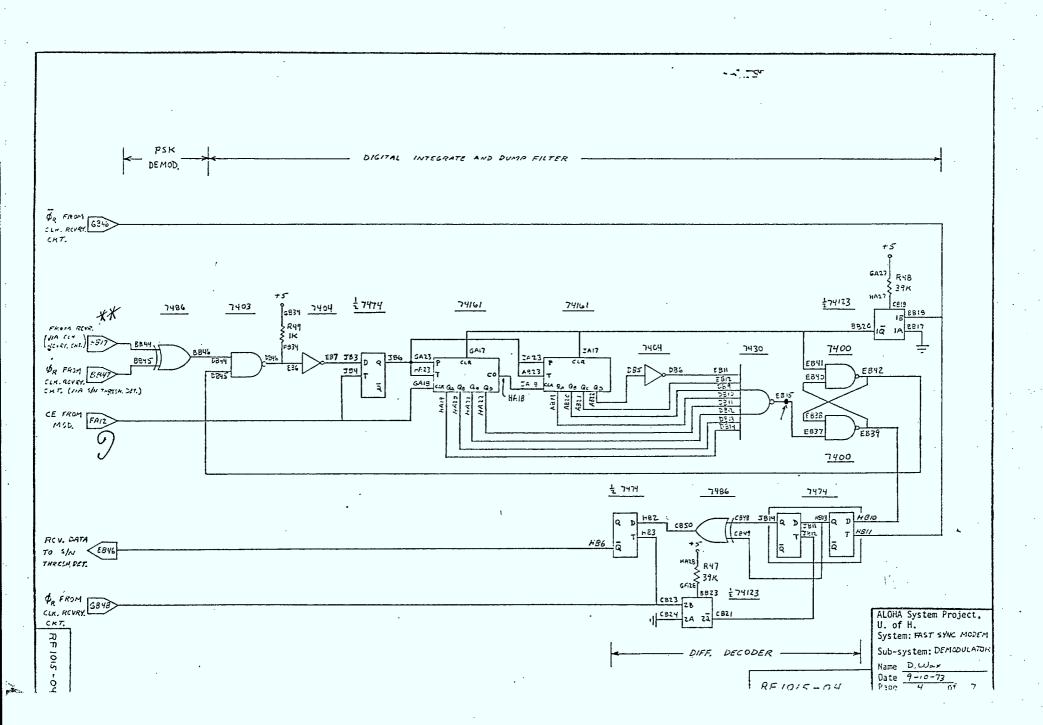

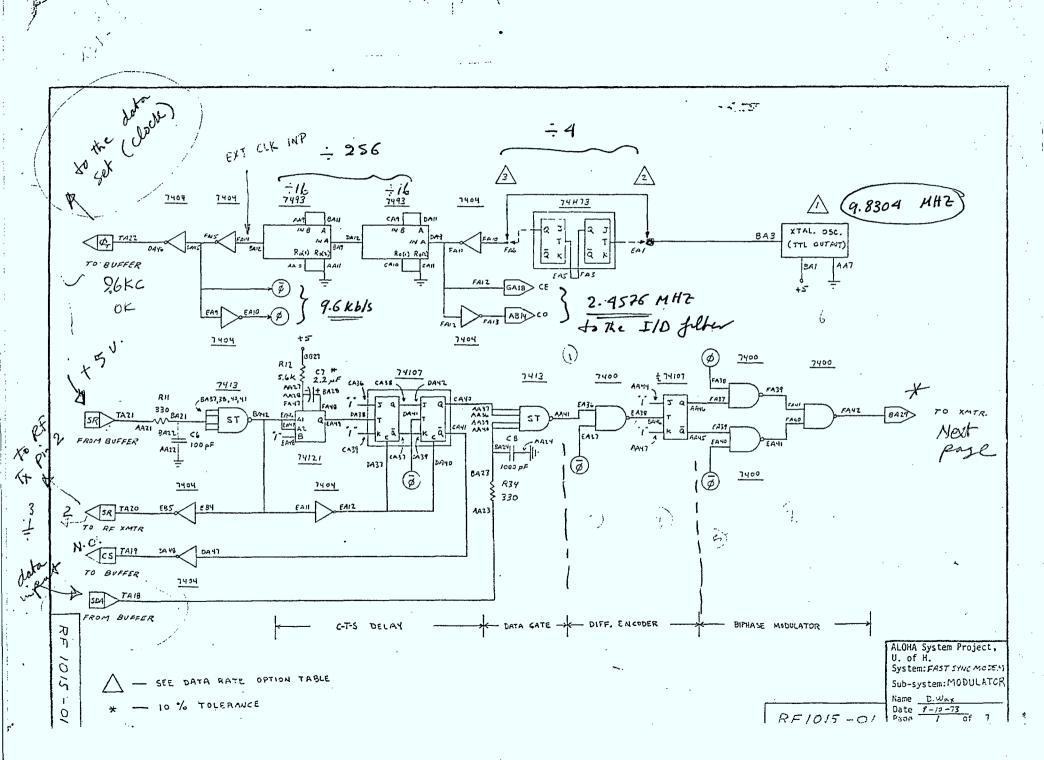

This chapter describes the laboratory experiments which were set up to study the effects of Gaussian noise on differentially coherent phase-shift keying (DPSK) and Fast Frequency Shift Keying (FFSK) modulation schemes for non-fading and fading channels. The DPSK modem was obtained from the University of Hawaii Electrical Engineering Department where it was used in the ALOHA experiments. The data transmission rate is 9600 bits/sec. The FFSK modem with a data rate of 16 K bits/sec was designed at the Communication Research Center, Ottawa where it was used in field experiments involving transmission of digitized voice. Sections 4.2 and 4.3 present the experimental results obtained with the DPSK and FFSK modems used. In section 4.4, the fading simulator is described, along with tests for verifying its proper functioning. Continuing work on the design of a Tamed Frequency Modulation (TFM) modem is outlined in section 4.5.

# 4.2 DPSK Modem Experimental Set-up and Results

# 4.2.1 Theoretical Background

The DPSK modulation scheme makes use of the carrier phase of the preceding signaling interval to obtain a phase reference for use in demodulation [1]. The bit error rate for DPSK over an additive white Gaussian noise channel with two-sided noise spectral density  $\frac{N_0}{2}$  is given by [2]

$$p_b = \frac{1}{2} e^{-\frac{E_b}{N_0}}$$

(12)

where  $\mathbf{E}_{\mathbf{b}}$  is the energy per bit.

This may be contrasted to coherent PSK (with a modulation index m = 1) for which the bit error rate is [1,3]

$$p_b = Q \left( \sqrt{\frac{2E_b}{N_o}} \right) = \frac{1}{2} erfc \left( \sqrt{\frac{E_b}{N_o}} \right)$$

(13)

Using the approximation

$$Q(\alpha) \approx \frac{1}{\sqrt{2\pi}\alpha} e^{-\alpha^2/2}$$

(14)

which is quite accurate for  $\alpha \ge 2$ , equation (13)

becomes

$$p_b \approx \frac{1}{2\sqrt{\pi} E_b/N_o} e^{-E_b/N_o}$$

Thus for  $\frac{E_b}{N_0} \gtrsim 2$ , the bit error rates for DPSK and coherent PSK differ only by a factor  $\sqrt{\pi E_b N_0}$ . For  $p_b < 10^{-4}$ , this amounts to a loss of less than 1 db in signal-to-noise ratio. This makes DPSK a convenient means of providing a carrier reference for demodulation.

The probability of bit error when DPSK is used over a Gaussian noise channel which is subject to Rayleigh fading can be derived as in [3] and is given by

$$p_b = \frac{1}{2(1+\bar{E}_b/N_0)}$$

(16)

where  $\bar{\mathbf{E}}_{b}$  is the mean value of the received energy.

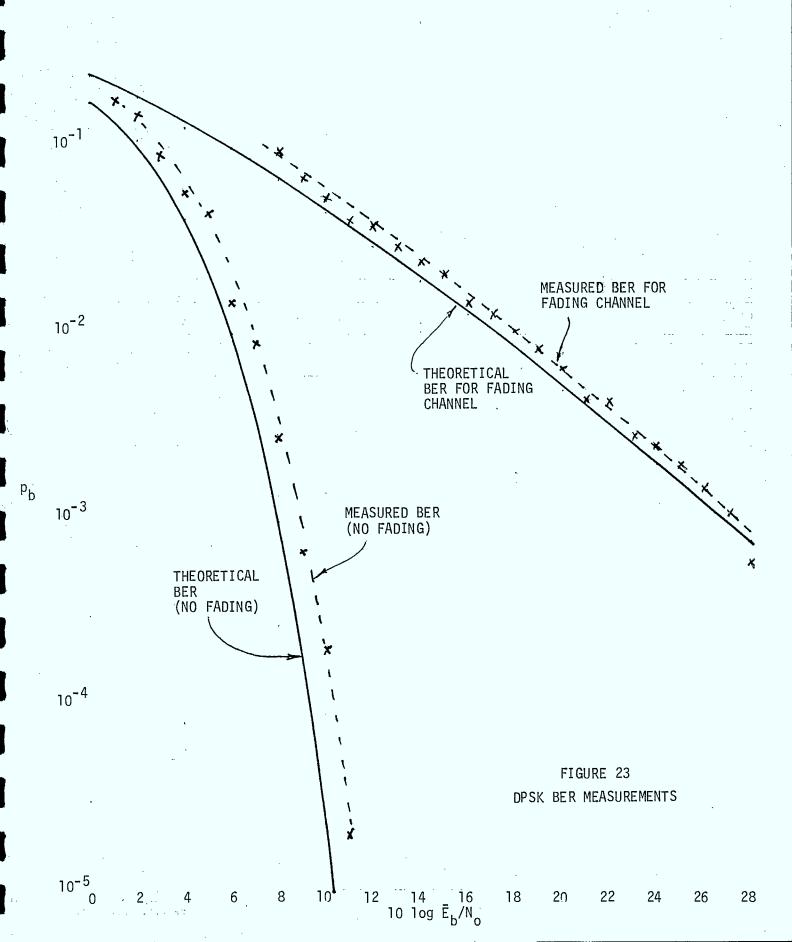

# 4.2.2 Experimental Set-up and Results

The block diagram of the experimental set-up is shown in Figure 22. Details of the fading simulator are given in section 4.4 and schematic diagrams for the DPSK modem are in Appendix C.

The experimental bit error rates for non-fading and fading channels as a function of the signal-to-noise ratio (mean SNR in the fading case) are shown in Figure 23. Also plotted are the theoretical curves obtained from equations (12) and (16). It can be seen that the experimental error rates are slightly higher than the theoretical values; however, there is generally good agreement between them with a maximum difference of about 1 dB in SNR.

FIGURE 22: DPSK Experimental Set-Up

# 4.3 Measurements of the FFSK Modem Set

The Fast Frequency-Shift Keying (FFSK) is a coherent binary modulation technique which has the following properties [4]:

- (1) it is phase coherent

- (2) it has low deviation ratio, L = 0.5

- (3) it occupies a band width which is typically 0.75 times the bit rate, without need for intersymbol interference correction

- (4) it uses as receiver a self-synchronizing circuit and a phase detector

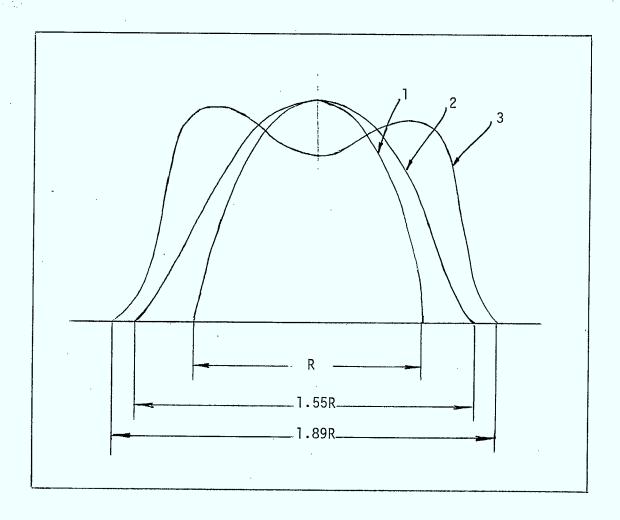

The bandwidth requirements for the FFSK modulation technique relative to FSK modulation techniques with modulation indices L=1.0 and L=0.71 is shown in Figure 25. The superiority of the FFSK modulation technique in terms of bandwidth utilization over the other two FSK modulators is apparent. This aspect indicates the suitability of the FFSK technique for mobile radio applications which require transmission of digital signals at high speeds over limited bandwidth channels.

The FFSK modulator used in the experiment reported here has been developed at the Communications Research Centre of the Federal Government [5]. The modulator has been tested in field experiments involving transmission of voice signals digitized at 16 K.bits/sec. In the experiment reported here the BER performance of the modulator is obtained under simulator fading conditions.

# 4.3.1 FFSK in Fading Channel

For FFSK, the bit error rate,  $P_e$ , is given by [4],

$$P_{e}(\rho) = Q(\sqrt{2\rho}) \qquad (\rho = \frac{E_{b}}{N_{o}})$$

where

$$Q(x) = \int_{-X}^{\infty} \frac{e^{-y^2/2}}{\sqrt{2\pi}} dy$$

$$= \frac{1}{\sqrt{2\pi}x} e^{-x^2/2}$$

Thus

$$P_e(\rho) = \frac{1}{\sqrt{4\pi\rho}} e^{-\rho}$$

.....(17)

Let  $\rho_{0}$  be the signal-to-noise ratio at the receiver given by:

$$\rho_0 = \frac{\bar{E}_b}{N_0}$$

where  $\bar{\mathsf{E}}_{\mathsf{b}}$  is the average energy per bit at the receiver.

The probability density function of  $\rho$  when the signal is subjected to fading will be [7]:

$$f(\rho) = \frac{1}{\rho_0} e^{-\rho/\rho_0}$$

The BER of the received signal in the existence of fading will be given by:

$$P_{b} = \int_{0}^{\infty} P_{e}(\rho) \cdot f(\rho) d\rho$$

$$= \int_{0}^{\infty} \frac{1}{\rho_{0}} e^{-\rho/\rho_{0}} \frac{1}{\sqrt{4\pi\rho_{0}}} e^{-\rho} d\rho$$

$$= \sqrt{\frac{1}{4\rho_0(1+\rho_0)}}$$

FIGURE 25

Relative Bandwidth Requirements for:

- 1. FFSK, h = 0.5

- 2. Coherent FSK, h = 0.7

- 3. Non-Coherent FSK, h = 1.0

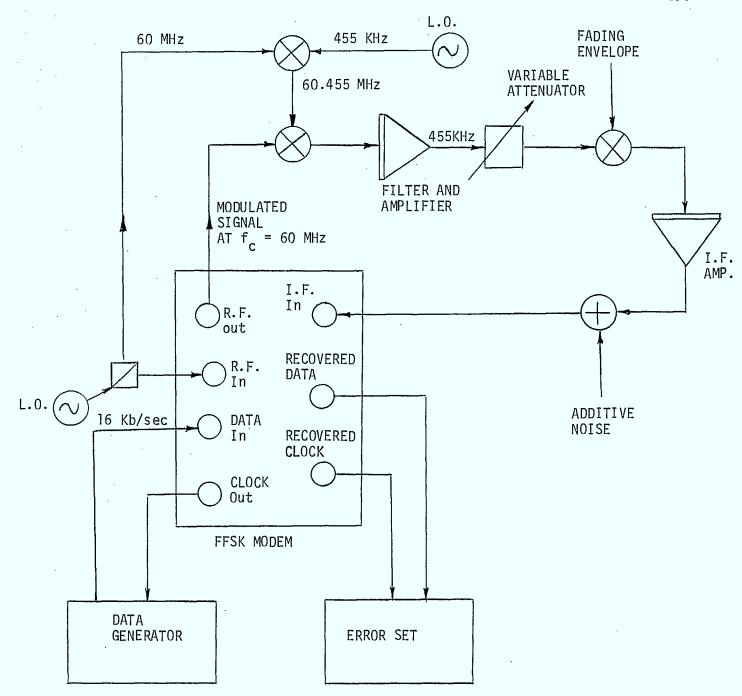

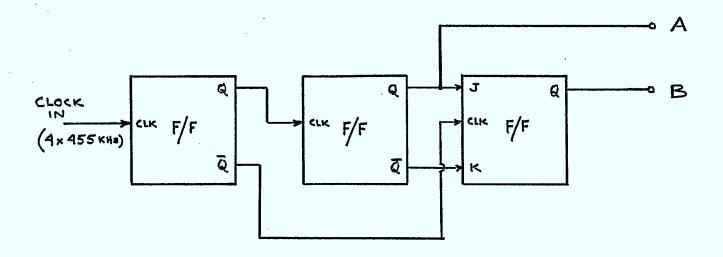

#### 4.3.2 Experimental Set-up

Figure 26 illustrates the experimental set-up used for measuring the performance of the FFSK modulator under simulated fading conditions. The modulator clock is used to generate an output data stream (PRBS) at 16 k.bits/second from the data generator which is fed as input data to the modulator. The modulator RF input signal has  $f_{\rm C}=60$  MHz at +10dBm. The modulated signal thus has a carrier frequency of 60 MHz, with the RF output of the modulator at -16 dBm. This signal is down converted to a centre frequency of 455 KHz which is the IF input to the demodulator section.

The down conversion from  $f_c$  = 60 MHz to  $f_c'$  = 455 KHz is accomplished by multiplying the RF output of the modulator by a signal with frequency  $f_m$  = 60.455 MHz and then filtering out the high frequency components. To ensure that the IF frequency remains constant at 455 KHz, it is essential to maintain the difference  $f_m$  -  $f_c$  equal to 455 KHz. This is achieved by using the same input signal to the modulator's R.F. section to generate  $f_m$  as shown in Figure 26.

FIGURE 26: Modem Measurement Set-Up

# 4.3.3 Results

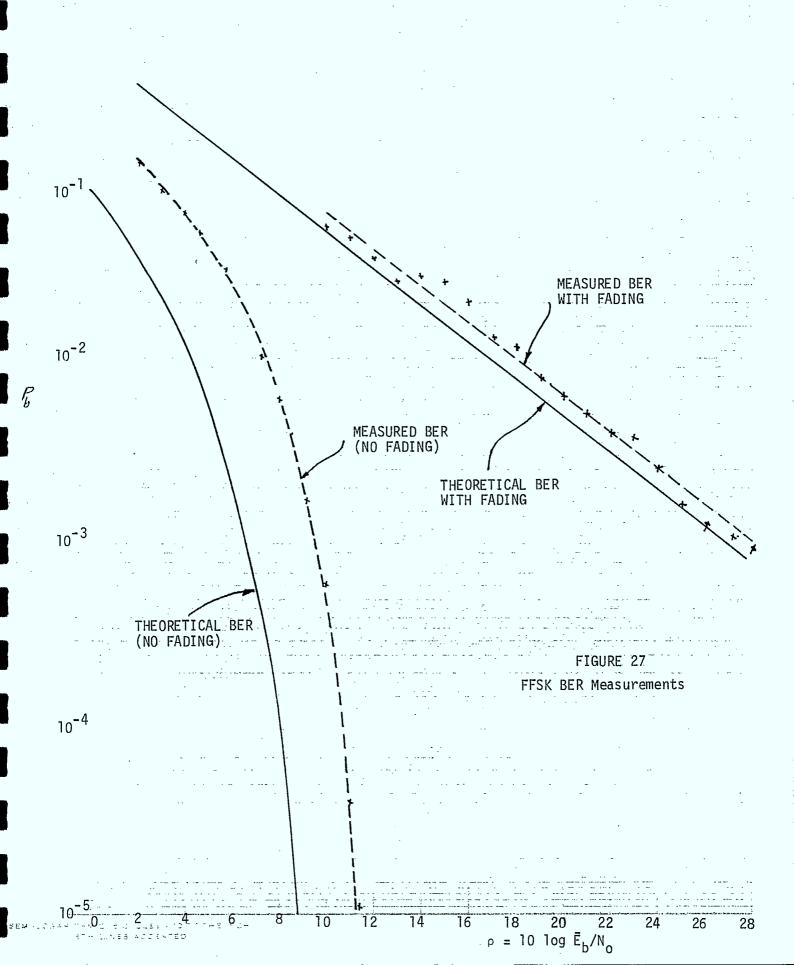

The results of the measurements conducted on the FFSK modem set are shown in Figure 26. The theoretical BER with no fading signal if based on equation (17). The measured BER for the modem falls within 2dB in SNR from the theoretical BER.

Under fading conditions, the agreement between the measured BER and the theoretical curve is extremely close; a maximum difference of at most 1 dB in SNR exists between the two curves.

The effect of fading on the performance of the FFSK modem becomes noticable at low BER. For example, to obtain a BER of  $10^{-3}$ , it is essential to increase the SNR from approximatley 10 dB (with no fading) to 28 dB when fading conditions are taken into account.

The effect of fading on the transmission of data messages is obviously a dominant factor that must be addressed. This indicates the importance of transmitting data at higher speeds and the use of forward error corrections such as those discussed in Chapter 2.

# 4.4 <u>Non-Recursive Implementation of a Tamed Frequency Modulator</u> Introduction

The Tamed frequency modulation (TFM) technique has the advantage of placing very little out of band radiation as compared with other constant-envelope modulation technique [6]. This modulation technique can allow data transmission at a rate of 16 K bits/sec with a radio channel spacing of 30 K Hz with less than -70 dB out of band radiation into the adjacent channels. The modulation scheme still allows orthogonal coherent detection of the modulated signal.

The code rule for TFM defines the phase function value at the sampling instants

$$t = (m - 1) T$$

,  $mT$ ,  $(m + 1)T$ , ..... as follows:

$$\phi(mT + T) - \phi(mT) = \frac{\pi}{2} - (\frac{a_{m-1}}{4} + \frac{a_m}{2} + \frac{a_{m+1}}{4}) \qquad (19)$$

with  $\phi(o) = 0$  if  $a_0 \cdot a_1 = 1$  and  $\phi(o) = \frac{\pi}{4}$  if  $a_0 \cdot a_1 = -1$

where  $a(t)$  is the data signal.

If the three successive bits have the same polarity the phase changes by  $\frac{\pi}{2}$ , and the phase remains constant for three bits of alternating polarity. The change in phase values for all different combination of data input is illustrated in Table 4.1. It should be noted that the phase values of the TFM signal at successive sampling moments are dependent. For better spectrum efficiency, the phase should vary as smoothly as possible between sampling moments.

TABLE 4.1

| a <sub>m+1</sub> | a <sub>m</sub> | a <sub>m-1</sub> | $\Delta \phi (m+1) = \phi (m+1) - \phi (m)$ |

|------------------|----------------|------------------|---------------------------------------------|

| -1               | -1             | -1               | <del>-</del> π/2                            |

| -1               | -1             | +1               | -π/4                                        |

| -1               | +1             | -1               | 0                                           |

| -1               | +1             | +1               | +π/4                                        |

| +1               | -7             | -1               | -π/ <sub>4</sub>                            |

| +7               | -1             | +1               | 0                                           |

| +7               | +7             | -1               | +π/4                                        |

| +1               | +1             | +1               | +π/2                                        |

|                  |                |                  |                                             |

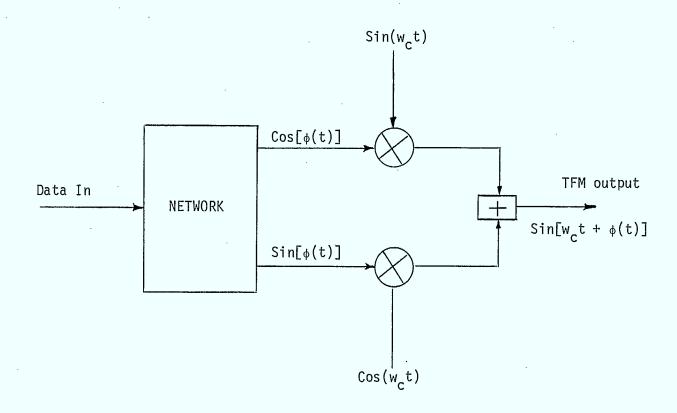

#### 4.4.1 Implementation of the Modulator Circuit

The tamed frequency modulator can be built using both recursive and non-recursive techniques [6]. However, because of instability problems of the former, the latter scheme was chosen.

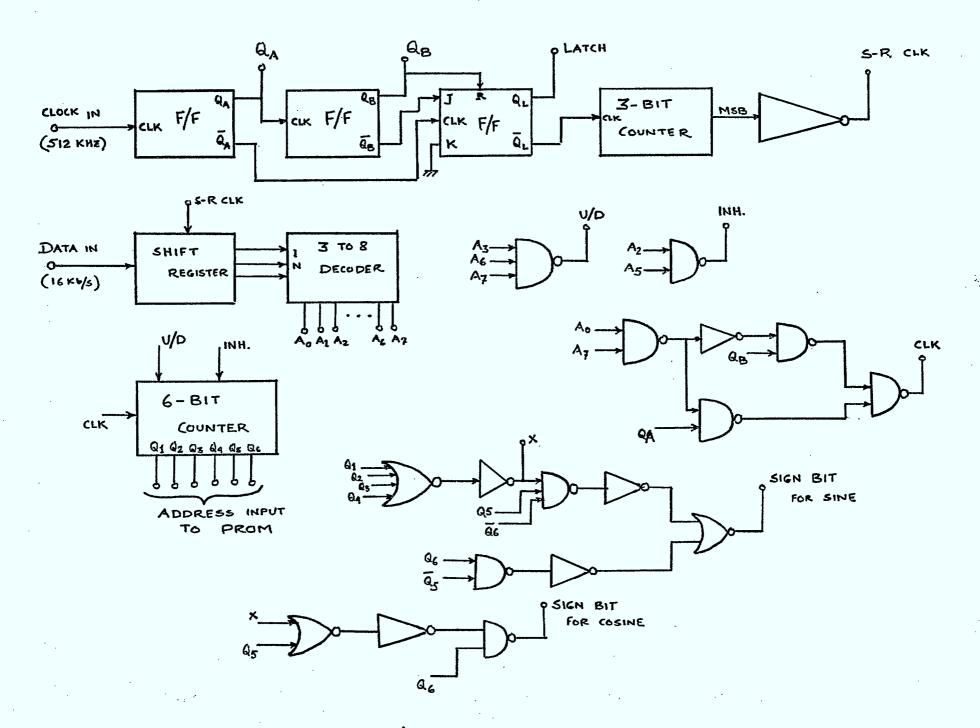

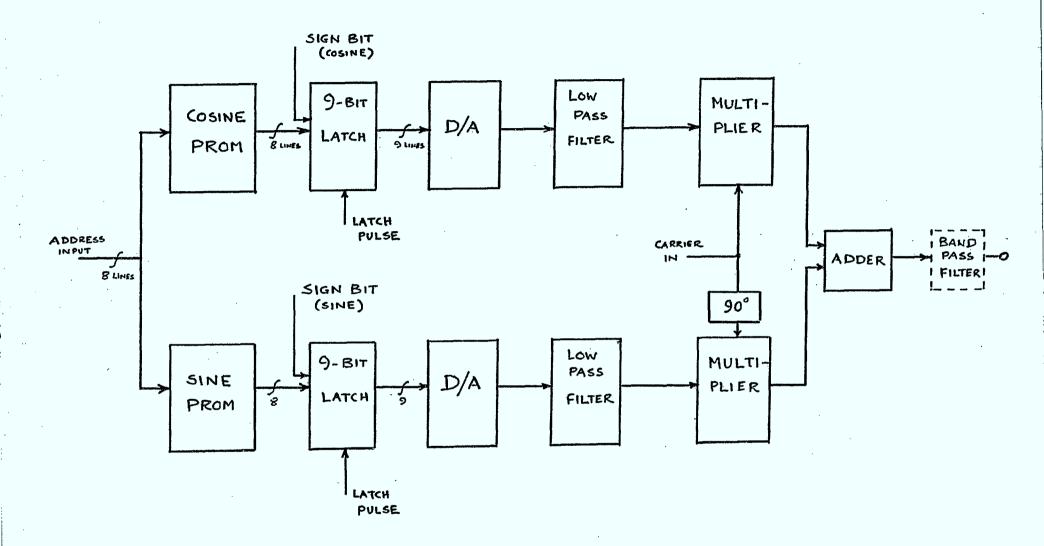

A basic block diagram of a non-recursive system is shown in Figure 28. The implementation is based on a quadrature modulator. The imput data is fed to a network which puts out the sine and cosine of the phase angle according to the code rate given in equation (19). The outputs are applied to two product modulators operating in quadrative. An interpolation technique is used to ensure that the phase function changes smoothly from one sampling instant to the next.

Figure 28 - Basic Block Diagram of a Tamed

Frequency Modulator Circuit

A 3-bit TFM system was implemented using a linear interpolation technique. It is seen from equation (19) that at the sampling instants the phase value can only change by 0,  $\pm \frac{\pi}{4}$  or  $\pm \frac{\pi}{2}$ . In order for the phase function to vary smoothly from one sampling instant to the next, 8 - interpolating levels were introduced between samples. Thus for a phase change of  $\pm \frac{\pi}{4}$ , the phase function changes in 8 steps, each step of size  $\pm \frac{\pi}{32}$ , and for a phase change of  $\pm \frac{\pi}{2}$ , the step size is  $\pm \frac{\pi}{16}$ . To implement this interpolation scheme two PROMS were coded with the Sine and Cosine of angles  $\frac{n\pi}{32}$  for n = 0, 1 .....63, to encompass the entire 0 to  $360^{\circ}$  phase circle. The address to the PROMS is changed at 8 times the sampling rate for a phase change of  $\pm \frac{\pi}{4}$ . For a phase change of  $\pm \frac{\pi}{2}$ , the address is changed at 16 times the sampling rate although the data outputs from the PROMS are still "latched" out at 8 times the sampling rate so as to provide only 8 interpolating levels.

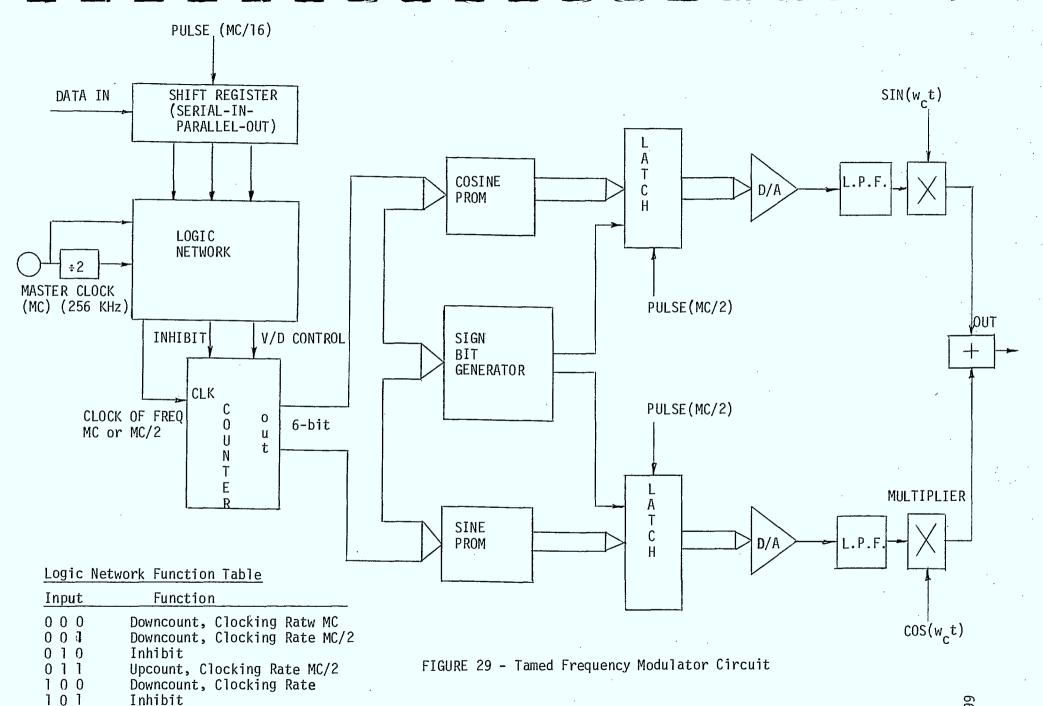

Figure 29 shows a block diagram of a circuit used to implement the TFM system. The data enters a serial-in, parallel-out shift register at the appropriate sampling rate. (The system was designed for 16 K bit/sec data rate). The outputs from the shift register are fed to a logic network which controls the operation of a 6-bit up-down counter according to the input bit pattern. A function table for the logic network is included in Figure 29. The counter is either upcounted, down counted or inhibited depending on the input bit string. The clocking rate is doubled when the bit strong is either 0, 0, 0 or 1, 1, 1.

The counter output forms the address of two PROMS which contains the unsigned COSINE and SINE of the angle values in 8-bit digital words.

The sign bit is generated externally from the address inputs. The output from the PROMS and the sign bits are latched and fed to two D/A converters

110

111

Upcount, Clocking Rate MC/2 Upcount, Clocking Rate MC

followed by two low pass filters and two product multipliers operating in quadrature. Each low pass filter was designed to have linear phase (Bessel filter) with a cut-off frequency around 64 KHz. The output from the two multipliers are added in a summing amplifier to provide the final phase modulated output. The complete circuit details are included in Appendix D.

### 4.4.2 Results

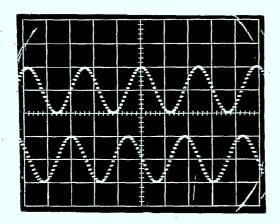

A 3-bit TFM system using linear interpolation scheme was breadboarded for initial investigations. To conserve power, the digital logic part was built using CMOS devices. Analog devices AD561 and AD534 were used as digital to analog converters and analog to analog multipliers respectively. Although 1 PROM could be multiplexed, for convenience, 2 PROMS (2716) were used for storing the Sine and Cosine code Tables. Each PROM location was coded with the respective Sine or Cosine value of angle  $\frac{11\pi}{32}$ with n varying from 0 to 63. The total memory requirement is therefore 128 bytes. When the input data is such that the phase change between two successive intervals is  $\pi/4$ , the PROM addresses are scanned at 128 KHz i.e. 8 times the data rate (16 k bits/sec). When the phase change is  $\pi/2$ the addresses are scanned at 16 times the data rate. However, only the output corresponding to every alternate address input is presented to the D/A. Figure 30(a) and (b) illustrate the situations. Figure 30(a) shows the D/A outputs from the Sine (top) and the Cosine (bottom) channels. The input data stream is continuously held at Oll. Consequently, the PROM addresses are incremented at a rate of 128 KHz - thus producing a Sine and a Cosine wave output with a periodicity of 0.5 msec ( $\frac{1}{128\text{KHz}} \times 64$ ). A continuous input of 110, 001 or 100 will provide identical results, however in the last two cases the PROM addresses will be continuously decremented.

Figure 30 (b) shows the D/A outputs from the Sine (top) and Cosine (bottom) channels for a continuous inout of 111. In this case the PROM addresses are incremented at twice the above rate and thus producing a Sine and a Cosine ware output with periodicity of 0.25 m sec. Doubling of the output step is also evident from the figire. For a continuous input of 000, the PROM addresses will be continuously decremented, however, the D/A outputs will appear identical to Figure 3(b).

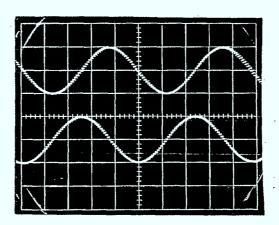

Figure 31 demonstrates the code rule that is fundamental to the TFM system. For this demonstration, the input shift register was replaced by a 3-bit counter so that all possible combinations of the input data stream are sequentially presented to the TFM system. The D/A output from the Sine (top) and the Cosine (bottom) channels are shown in the figure. When an input of 010 is presented to the system, no change in phase takes place at the output. This is seen by the Straight line portion on the left hand side of the figure. The output remains fixed until the input is changed at 011. When a phase change of  $+45^{0}$  takes place in 8 equal Following this the input is changed to 100. The subsequent phase changes are  $-45^{\circ}$ ,  $0^{\circ}$ ,  $+45^{\circ}$ ,  $+90^{\circ}$ ,  $-90^{\circ}$  and  $-45^{\circ}$  until the situation repeats. In this figure, the absolute phase angle is close to  $0^{0}$  during the time no phase change takes place i.e. between input 010 and 011. Figure 30(a) (b), and 31 only illustrate the operation of the TFM system for arbitrary inputs. In actual operation the change in input at any sampling interval is dependent on the past input.

A carrier frequency of 455 KHz was used in the present experiments. A quadrative modulation was achieved by using two square waves shifted in phase of  $90^{\circ}$ . A circuit schematic for generating  $90^{\circ}$  phase

shifted square waves is shown in appendix D. Two multipliers (AD534) were used for up translation. The output from the multipliers were added in an operational amplifier summer. A band pass filter can be employed at the output of the summer network to suppress unwanted modulations around the harmonics of the carrier frequency. Using a psendo random data input, the output spectrum showed more than 45dB attenuation beyond a 16 KHz band spread as shown in Figure 32. The results were as expected for a 3-bit transation. At present, however, a demodulator circuit is yet to be built for data recovery.

### 4.4.3 Summary

The initial results on TFM system clearly holds promise. Detailed characterization is now underway. The circuit is also being refined. It is believed that the D-A converter and the multiplier network in each channel can be replaced by a single multiplying D to A converter (MDAC). This will reduce cost and further save power. Also, the configuration will be more amenable to integration on a single chip.

(a)

(b)

Figure 30 - D/A Outputs for an Input (a) 011; (b) 111

[Horizontal Scale - 0.1 m sec/div; Vertical Scale - SV/div.]

Figure 31 - D/A Outputs for Input Continuously Varying from 000 to 111 by Means of a 3-bit Counter

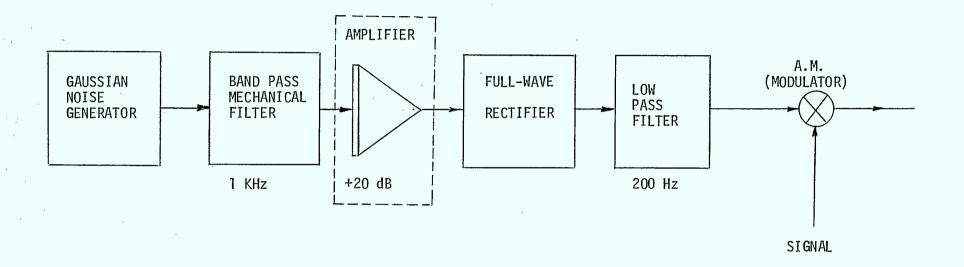

## 4.5 The Fading Signal Simulator

### 4.5.1 Fading Simulator Circuit

The black diagram of the fading simulator circuit is shown in Figure 33. A white gaussian noise generator is used to generate a random signal with a uniform spectrum up to about 200 KHz. This signal is then bandlimited using a narrow bandpass filter with a centre frequency of  $f_0 = 1$  KHz and sharp cutoff frequencies of approximately ( $f_0 \pm f_m$ ),  $f_m = 7.6$  Hz. The band limited signal is then full-wave rectified after it has been amplified to raise the signal to such a level as would enable the rectifier to operate efficiently. The rectified signal is next passed through a low-pass filter ( $f_C = 200$  Hz) to remove the 1 KHz carrier. The result is a signal whose amplitude approximates the Raleigh distribution. The resultant wave form is mixed with the IF signal using an amplitude modulator.

If the operating frequency of the system is taken to be at 170 MHz, the wavelength  $\lambda$  will be equal to 1.765m. The maximum doppler frequency,  $f_m$ , is given by

$f_{m} = v/1.765 \; \text{Hz, v is the vehicle speed.}$  Thus for v = 48 Km/hr,  $f_{m} = 7.6 \; \text{Hz}$  and for v = 96 km/hr,  $f_{m} = 15 \; \text{Hz}$ .

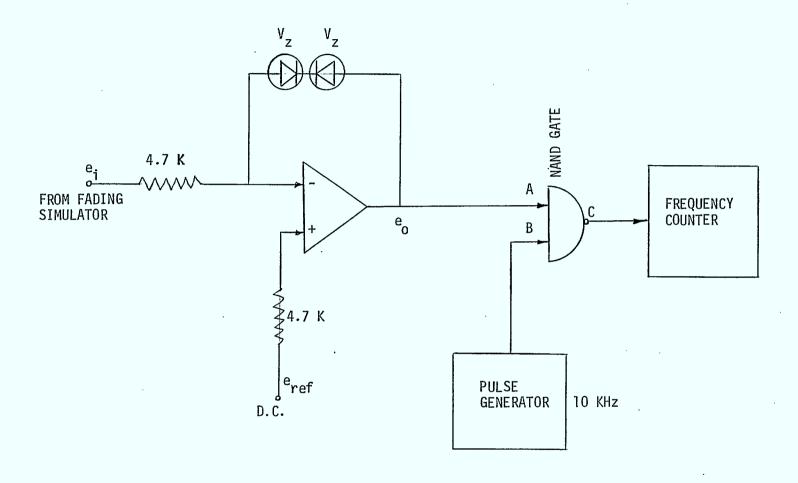

# 4.5.2 Fading Simulator Testing

The circuit shown in Figure 34 is used to test the fading simulator. The output signal from the fading circuit is compared to a variable d.c. reference. The voltage comparator has the following characteristics:

$$e_0 = + V_z$$

, if  $e_i < e_{ref}$ ,

$e_0 = - V_z$ , if  $e_i > e_{ref}$

The resulting random square wave is then sampled at 10 Kb/sec using a clock generator and a NAND gate. The number of pulses is then recorded using a frequency counter which is activated using a gate signal (push button) for one second durations.

The percentage of time the signal level exceeded the d.c. threshold level is calculated as:

% time above threshold level =

$$\frac{N}{f_c \cdot T_g} \times 100$$

where:  $f_c$  = frequency of clock generator = 10 Kb/sec

$T_{\alpha}$  = gate duration = 1 second

N = counter reading at the end of the gate pulse

Thus the cumulative distribution of the output signal from the fading simulator can be determined.

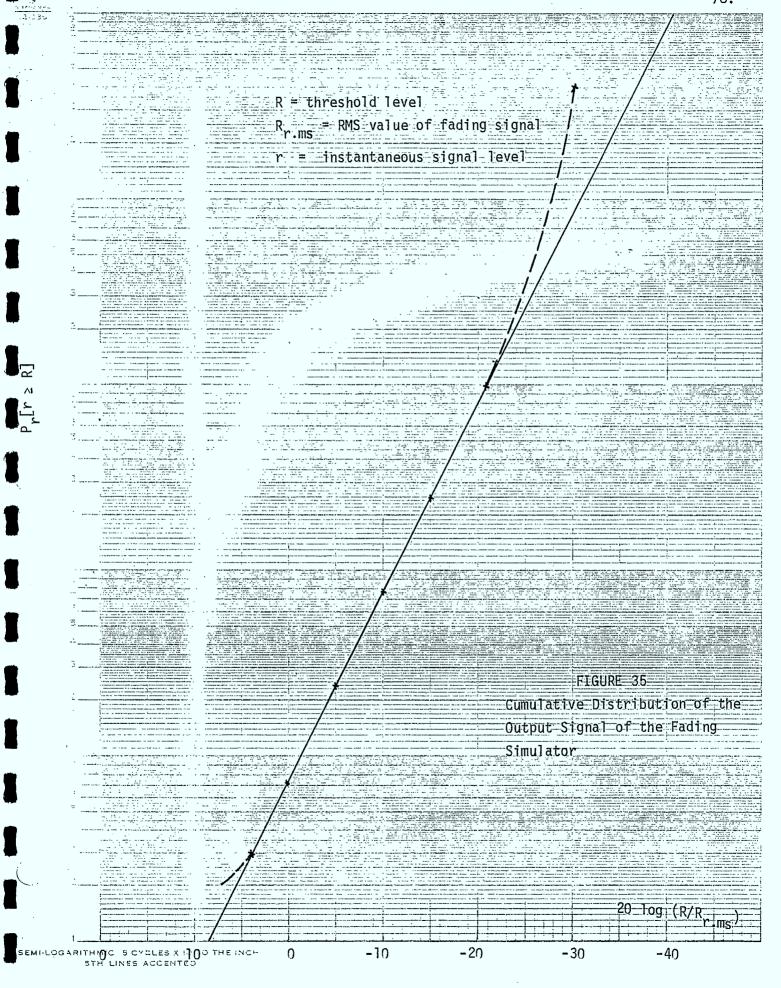

Figure 35 shows a plot of the percentage of time the signal level exceeds the threshold for various threshold levels. The solid line represents the theoretical curve for Raleigh distribution while the dotted line represents the result of the measurements. The range of agreement extends from about +5dB to -20dB. At each threshold level, thirty readings were taken and averaged.

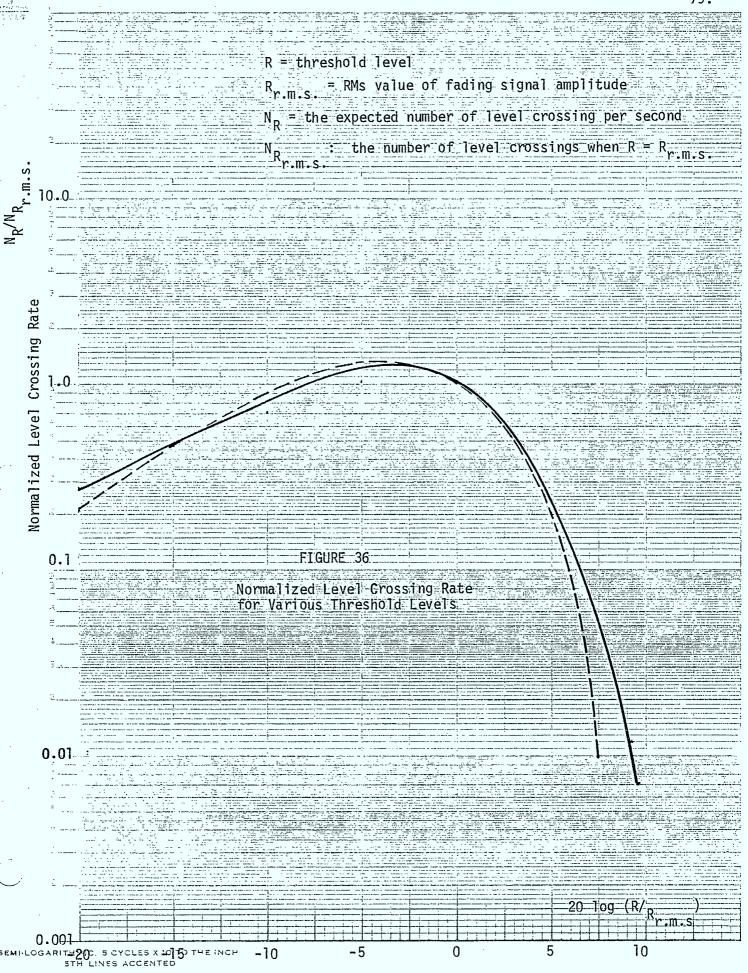

Figure 36 shows a plot of the normalized level crossing rate for various threshold levels. The solid line represents the theoretical curve while the dotted line represents the experimental results. The agreement between the two curves is again very close for a range of 5 dB to -20 dB. It is concluded that the simulated circuit produces an output

which has the same characteristics as the fading signals in mobile radio channels.

FIGURE 33: Block Diagram of Fading Simulator

FIGURE 34: Circuit Diagram for Testing the Simulator

### REFERENCES

- [1] R.E. Ziemer and W.H. Tranter, <u>Principles of Communications</u>, Houghton Mifflin, 1976.

- [2] J.J. Downing, <u>Modulation Systems and Noise</u>, Prentice-Hall, 1964.

- [3] J.M. Wozencraft and I.M. Jacobs, <u>Principles of Communication</u>

<u>Engineering</u>, Wiley, 1965.

- [4] Rudi De Buda, "Coherent Demodulation of Frequency-Shift Keying with Low Deviation Ratio", IEEE Transactions on Communications, June 1972, pp. 429-435.

- [5] R. Matyas, "Effect of Noisy Phase References on Coherent Detection of FFSK Signals", IEEE Communications, Vol. COM 26-6, June 1978.

- [6] F. de Jager and C. Dekker, "Tamed Frequency Modulation, A Novel Method to Achieve Spectrum Economy in Digital Transmission",

IEEE Transactions on Communications, Vol. COM 26, No. 5, May 1978.

- [7] M. Schwartz, W.R. Bennet, and S. Sterin, "Communications Systems and Techniques", McGraw Hill, 1966.

### Summary and Future Research

### 5.1 Summary

The following is a summary of the results of the research reported here.

- 1. In chapter 2, the use of forward error correction in improving the performance of a stop-and-wait ARQ scheme over random-error and Rayleigh fading channels was examined. The results show that both the mean wasted time and the mean time to successful transmission can be substantially reduced by forward error correction.

- 2. A low cost CMOS microprocessor board has been designed and implemented, as reported in chapter 3. The microprocessor is functionally equivalent to the Intel 8020 board with respect to the mobile terminal control requirements. However, the CMOS board's power consumption is approximately 1/30 of a functionally comparable board constructed using the I<sup>2</sup>L technology.

- 3. The performance of two modulator sets (DPSK and FFSK) which have been used previously in mobile applications has been tested experimentally under simulated fading conditions. Fading effects were shown to be dominant at low BER, as substantially higher SNR at the receiver is required to obtain the same BER when no fading signals exist.

- 4. A non-recursive TFM modulator circuit has been designed and implemented. The output spectrum for the modulator circuit showed more that 45 db attentuation beyond a 16 kHz band spread. A demodulator circuit is planned in the immediate future to test the BER performance of TFM under fading conditions.

### 5.2 Future Research

As explained earlier, the results of the research reported here represent intermediate steps towards the objective of establishing the feasibility of an all digital integrated voice and data mobile communications system. As a follow up to these steps, the following research areas will be explored in the immediate future.

- Construction of the TFM demodulator component. This will be followed by testing the TFM modem under fading conditions to compare its performance to the FFSK modem.

- 2. Construction of a voice digitization encoder/decoder circuit at 16 Kb/sec. The effects of modulation and fading on the quality of voice received over radio channels will be tested.

- 3. Construction of a suitable voice detection circuit which will be used as a carrier on/off switch in the voice circuit of the mobile terminal.

- 4. The implementation of forward error correcting codes will be explored with special considerations given to the trade-offs between improvement in throughput and added complexity and cost. Improvements in performance obtainable through the use of diversity transmission will also be examined. Encryption techniques will be studied so as to meet the confidentiality requirements needed in certain applications such as police communication.

# APPENDIX A

A SAMPLE OF MICROPROCESSOR TEST

ROUTINES

# EPROM #1 (MEMORY, PARALLEL I/O, RST 5.5 TEST)

| RESET  | 00 XMT                                   | PORT TEST                       |                                              |

|--------|------------------------------------------|---------------------------------|----------------------------------------------|

|        | 00 AF                                    | XRLA,A                          |                                              |

|        | 01 d301                                  | OUTA,XMT                        |                                              |

|        | 03 2F                                    | COMPA                           |                                              |

|        | 04 C30100                                | JMP 01                          |                                              |

| TRAP   | 24 MEMORY TES                            | ST                              | ,                                            |

|        | 24 3ECE                                  | MOV A, #CE                      |                                              |

|        | 26 30                                    | Sim                             | ENABLE                                       |

|        | 27 FB                                    | E1                              | INTERRUPTS                                   |

|        | 28 C34000                                | JMP40                           |                                              |

| CT.ADT | 40 45                                    | VDI A. A.                       | OUTPUT TRIGGER                               |

| START  |                                          | XRLA,A                          |                                              |

|        | 41 d301                                  | OUT A,XMT                       | PULSE TO                                     |

|        | 43 2F                                    | COMPA                           | TO TRANSMITTER                               |

|        | 44 d301                                  | OUTA,XMT                        | CONTROL PORT 01                              |

|        | 46 2F                                    | COMPA                           |                                              |

|        | 47 d301                                  | OUTA,XMT                        |                                              |

|        | 48 2601                                  | MOV H, #01                      | TEST EPROM                                   |

|        | 4B 2E00                                  | MOV L, #0                       | FROM 100 <sub>16</sub> to 2000 <sub>16</sub> |

|        | 4d 23                                    | INC H,L                         |                                              |

|        | 4e 7C                                    | MOV A,H                         |                                              |

|        | 4f FE20                                  | CPI #20                         | is Adde = 2000?                              |

|        | 51 CA5E00                                | J2,X                            | No continue; Yes go to RAM                   |

|        | 54 3EFF                                  | MOV A, #FF                      | check EPROM content                          |

|        | 56 46                                    | MOV B, (H,L)                    | iF = FF continue                             |

|        | 4e 7C<br>4f FE20<br>51 CA5E00<br>54 3EFF | MOV A,H CPI #20 J2,X MOV A, #FF | No continue; Yes go to                       |

|       | 57    | B8            | CMP A, B                | if # FF ERROR! RESTART      |

|-------|-------|---------------|-------------------------|-----------------------------|

|       | 58    | CA4doo        | JZ 4d                   |                             |

|       | 5B    | C34000        | JMP 40                  |                             |

|       | 5E    | 2630          | MOV H, #3ø              | SET START RAM               |

| Υ     | 60    | 23            | INC H,L                 | TEST RAM FROM               |

|       | 61    | 7C            | MOV A,H                 | 3,000 to 4000 <sub>16</sub> |

|       | 62    | FE 40         | CPI, #40                | 10                          |

|       | 64    | CA 4000       | JZ 40                   | is $Addr = 4000_{16}$       |

|       | 67    | AF            | XRLA,A                  | YES RESTART: NO CONTINUE    |

|       | 68    | 77            | MOV (H,L),A             | WRITE"Ø" in RAM             |

|       | 69    | 46            | MOV B, (H,L)            | READ FROM RAM               |

|       | 6A    | В8            | CMP A,B                 | COMPARE                     |

|       | 6B    | C24000        | JNZ 40                  | IF # RESTART                |

|       | 6E    | 3EFF          | MOV A, #FF              |                             |

|       | 70    | 77            | MOV (H,L),A             | WRITE "FF" in RAM           |

|       | 71.   | 46            | MOV B, (H,L)            | READ                        |

|       | 72    | B8            | COM A,B                 | COMPARE                     |

|       | 73    | CA6000        | JZ Y                    | IF = CONTINUE               |

|       | 76    | C34000        | JMP 40                  | IF # RESTART                |

| RST 5 | 5.5 A | DDR 2C        | TEST KEYBOARD PORT      |                             |

|       | USE D | OIP SWITCH AS | SEMBLY TO TEST KEYBOARD | PORT. USE 555 TO INTERRUPT  |

|       | CPU A | AND JUMP TO K | EYBOARD ROUTINE         |                             |

|       | 2C    | C3 7F00       | JMP 7F                  | TEST KEYBOARD PORT          |

|       | 7F    | FB            | EI                      |                             |

|       | 80    | dbo2          | in PO2                  |                             |

|       | 82    | 47            | MOV B,A                 |                             |

|       | 83    | EE00          | XRL A,#Ø                |                             |

|       |       |               |                         |                             |

| 85   | CA 2400 | BZ 24        |

|------|---------|--------------|

| 88   | 3EFF    | MOV A,#FF    |

| 8A   | A8      | XRL A,B      |

| 8B   | CA 9700 | B7 XMT1      |

| 8E   | 3E 47   | MOV A, #47   |

| 90   | A8      | XRL A,B      |

| 91 . | CA9d00  | BZ XMTØ      |

| 94   | C37F00  | JMP 7F       |

| 97   | 30      | XMTI INCA    |

| 98   | d301    | OUT POI      |

| 9A   | C37F00  | JMP 7F       |

| 9d   | d301    | XMTO OUT POI |

| 9F   | C37F00  | JMP 7F       |

# EPROM #2 (UART TEST) WITH RS 232 TERMINAL AND EXTERNAL 4.8 kHz CLK BAUD RATE 300

| RESET 00   | 3E od         | MOV A,#od   | SET 6.5 INT         |

|------------|---------------|-------------|---------------------|

| 02         | 30            | Sim         |                     |

| 04         | 06 00         | MOV B,#Ø    | CLR RB              |

| . 06       | C3 AØ 00      | JMP AØ      |                     |

| DCT C E 24 | C2 P000       | "IMD DO     | (NDITE TO DC 222)   |

|            | C3 B000       |             | (WRITE TO RS-232)   |

|            | 3E od         |             | (READ FROM RS-232)  |

| 3E         | 30            | Sim         | SET 6.5 INT         |

| 3 <b>F</b> | C3 C500       | JMP C5      |                     |

| AØ         | 26 00         | MOV H, #Ø   | SET MESSAGE         |

| 2          | 2E dd         | MOV L, #dd  | POINTER             |

| 4          | Fb            | EI          | ENABLE INT          |

| 5          | 76            | HALT        | WAIT                |

| ВØ         | 23            | INC H,L     | INCREMENT POINTER   |

| 1          | 3E <b>2</b> E | MOVA,#2E    | CHECK IF MESSAGE    |

| 3          | BE            | CMPA,(H,L)  | IS FINISHED         |

| 4          | CA BC 00      | BZ A        | YES GO TO READ OUT  |

| 7          | <b>7</b> E    | MOV A,(H,L) | NO OUTPUT           |

| 8          | d3 04         | OUT PO4     | CHARACTER TO RS 232 |

| А          | Fb            | EI          | EN INT              |

| В          | 76            | HALT        | AND WAIT            |

| С          | 78 A          | MOV A,B     | OUTPUT REG B        |

| d          | d304          | OUT PO4     | TO RS 232           |

| f          | 3E ob         | MOV A,#OB   | SET 7.5 INT         |

| C1         | 30            | SIM         | READ FROM RS 232    |

| 2  | Fb      | EI            | WAIT               |

|----|---------|---------------|--------------------|

| 3  | 76      | HALT          |                    |

| C5 | db 04   | In A, PO4     | GET CHARACTER IRO  |

| 7  | 47      | MOV B,A       | RS 232 AND STORE   |

| 8  | 21 F000 | MOV H,L #F000 | IN REG B           |

| b  | Fb      | EI            | INITIALIZE POINTER |

| С  | 76      | HALT          | WAIT FOR RS-232    |

|    |         |               | WRITE INTERRUPT    |

.

.

# CHARACTER SETS IN EPROM dE to 103

| dE | OA              | LF  | Fl  | OA | CR |

|----|-----------------|-----|-----|----|----|

| f  | ođ <sup>°</sup> | CR  | . 2 | od | LF |