# University of **Waterloo Research Institute**

PERFORMANCE MEASUREMENT IN COMPUTER NETWORKS

P 91 C655 M673 1975

che cked

OFFICE OF RESEARCH ADMINISTRATION UNIVERSITY OF WATERLOO INCORPORATING THE WATERLOO RESEARCH INSTITUTE

PROJECT NO. 3046-2

SPONSORED BY

Department of Communications

Under

Department of Supply and Services Contract Number OSU 4-0098

Salat COMMUNICATIONS CANADA BIBLIDTHEQU 984 2 1 JUNE LIBRARY

DD 4605565 DL 4605601 P 91 C655 M673 1975

# 1. Introduction

# 1.1 Computer Network Monitoring System

On 2 October 1974, at a panel discussion of the joint meeting of the ACM Special Interest Group on Measurement and Evaluation (SIGMETRIC) and Boole and Babbage Users' Group, leaders in the computer measurement field stated that since a number of organisations were forming computer networks, there was a need for a system of hardware and software to observe the activities of these networks. It soon became evident that we were the only people who had attempted to design and implement such a system, although a few other organisations, such as Comress and Tesdata, are hoping to produce suitable monitoring systems within one to two years.

Most measurements that have been made of computer networks have been made using software techniques (e.g., see <1,2>). Such software can and does interfere with network activities and produces significant inaccurracies in the measurements. Moreover, measurement traffic on the network can distort traffic statistics.

The system of special hardware and software we have been creating for the past three years is designed to observe the activities of a computer network while interfering minimally with them. This Computer Network Monitoring System (CNMS) is described in Appendices A, B, and C.

- 1 -

# 1.2 Computer Network Dependability Research

and more organisations are realizing that an un-More reliable computer system is not cost-effective, regardless of how quickly it executes or how efficiently it handles resources. Enhanced dependability is one reason often given for building networks of computers. We are investigating the possibility of using the Computer Network Monitoring a tool for enhancing the dependability of a com-System as puter network. We are devising an automated maintenance system for computer networks which is an integrated system composed of a number of tools for achieving dependability.

Bell Laboratories has devised a variety of tools and techniques for enhancing the dependability of electronic switching systems. These are described in Bell Systems Technical Journals of 1964, 1969, 1970, and 1973., and in <3,4>. A fairly extensive bibliography of computer system dependability studies is included in Appendix E. Appendices E and F survey the fields of computer system and network dependability.

# 2. Purpose

The objectives of this research are:

1. To provide an easily used, yet powerful computer network monitoring system. Experience indicates that neither hardware nor software alone are completely satisfac-

- 2 -

tory; thus, a combination is sought.

2. To learn how to provide a flexible, easily used network maintenance system that facilitates rapid detection, diagnosis, and recovery from network troubles, whether malfunctions or bottlenecks.

# 3. Summary of Methods

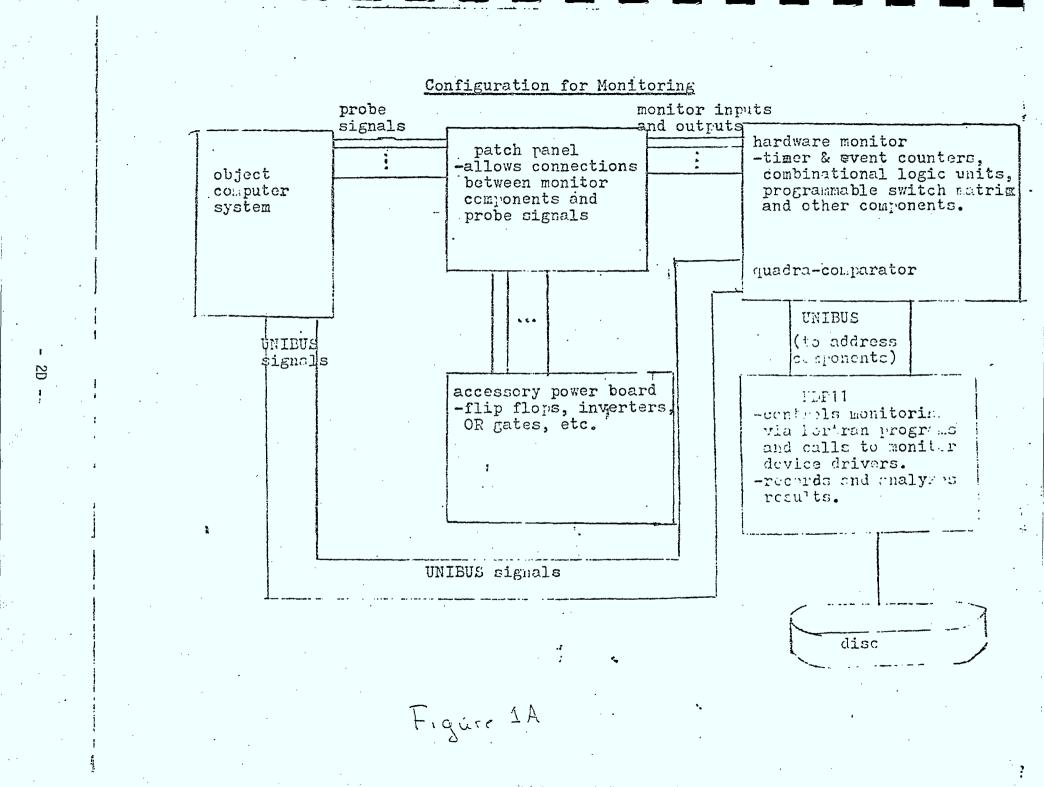

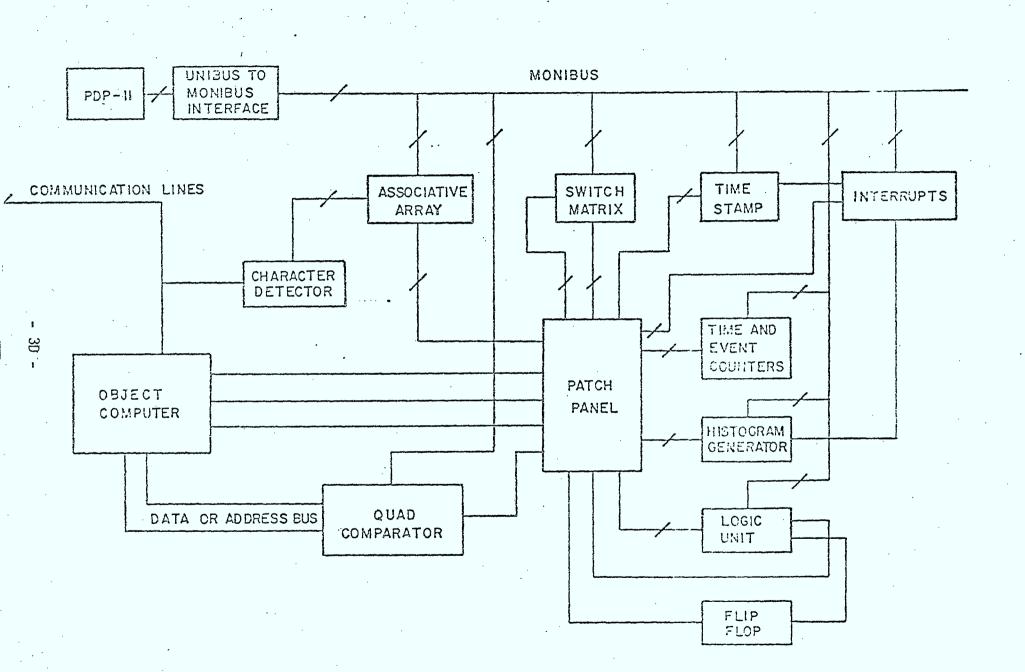

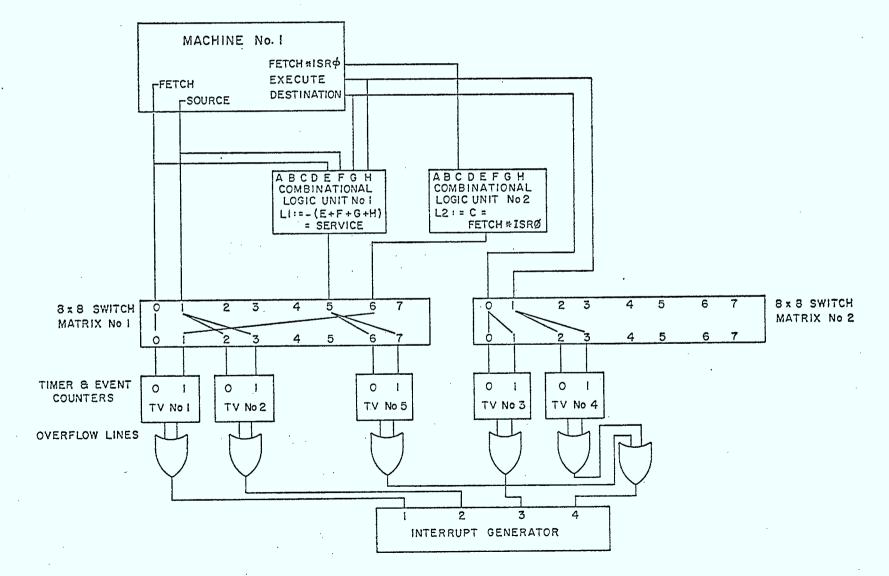

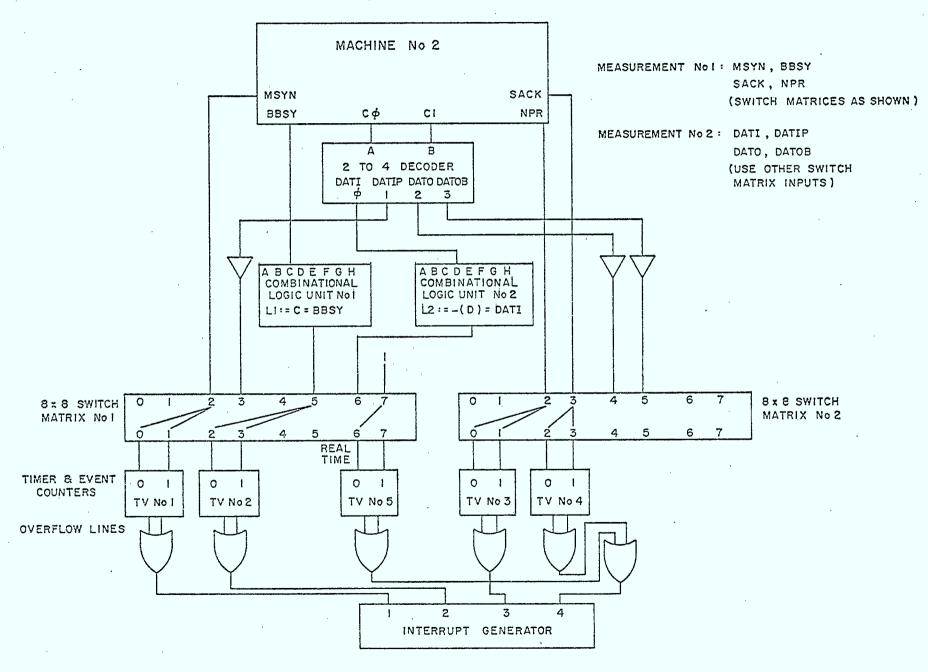

For the past four years, we have been designing, implementing, testing, and, within the past year, we have been using a prototype of a system of special hardware and software for monitoring a computer network (or computer system). Called a Computer Network Monitoring System (CNMS) and described in Appendices A, B, C, the system consists of:

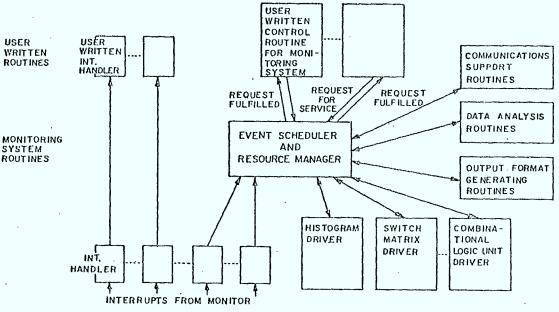

> (1.) A set of software-controlled hardware monitors (often called hybrid monitors), each of which is attached by its probes to a computer and associated data links of the network to be monitored. Each monitor can be controlled by a remotely-located computer via a telecommunications link.

> (2.) Software to control the monitors and analyse the data.

(3.) Software to generate traffic for the object network (i.e., the network to be monitored), so that measurements of the network's activities can be made as it responds to known stimuli.

(4.) A minimal amount of measurement software in

. 3 -

each system of the object network.

Our philosophy is to use hardware to monitor that which is best observed by hardware, to use software for that for which it is best suited, and to use a combination where neither is best.

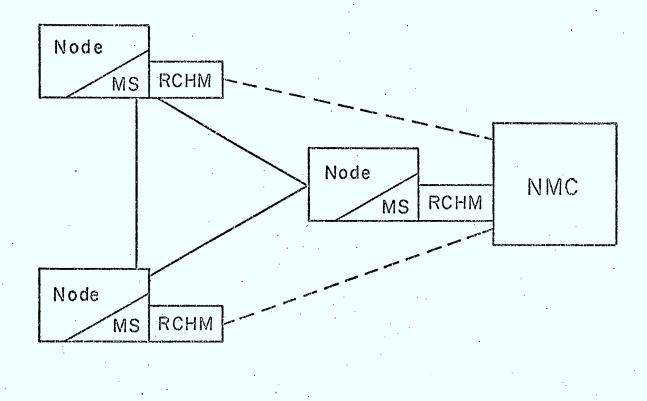

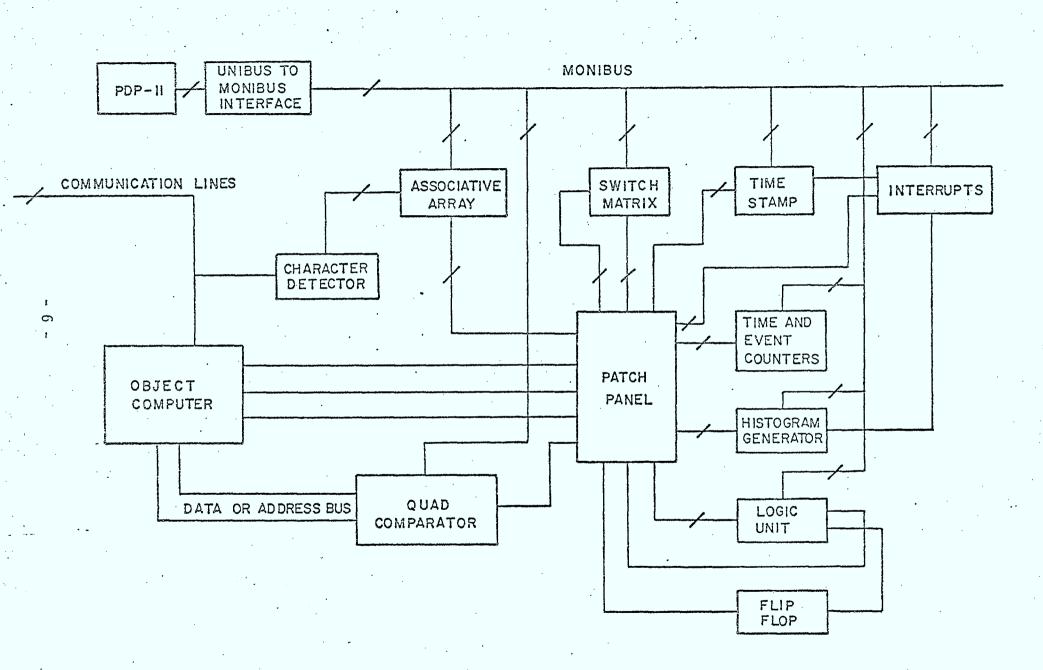

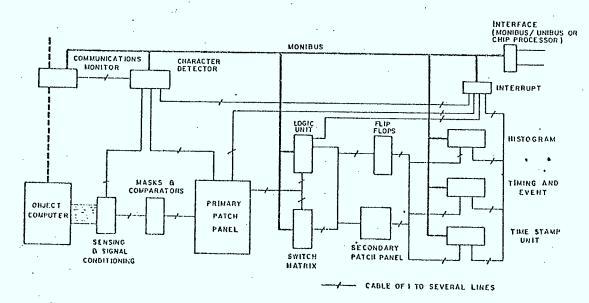

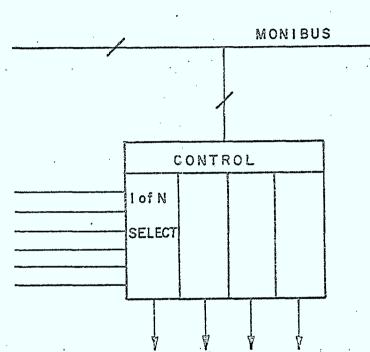

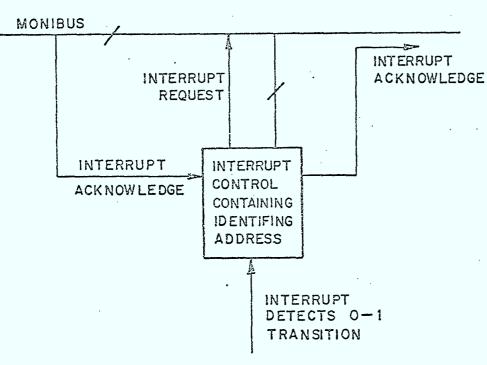

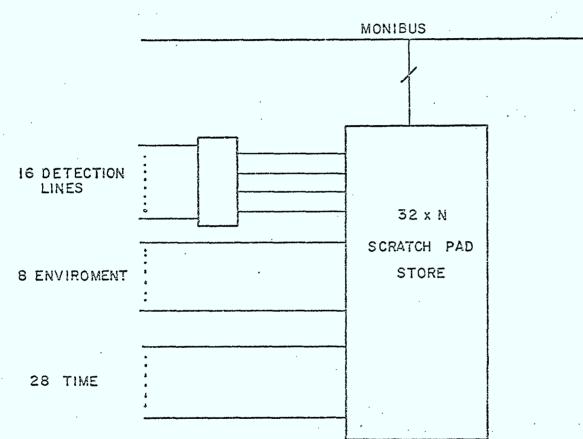

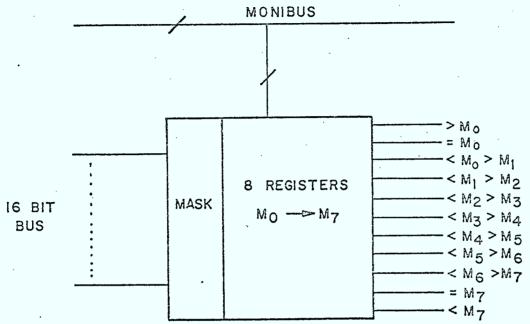

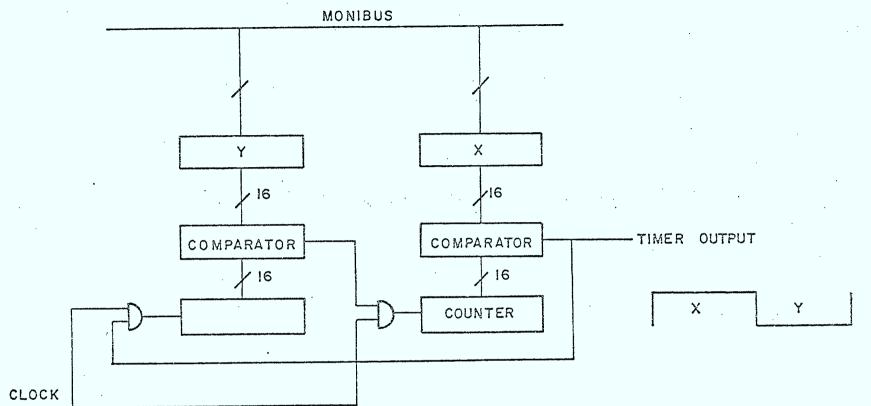

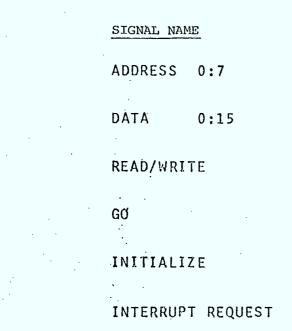

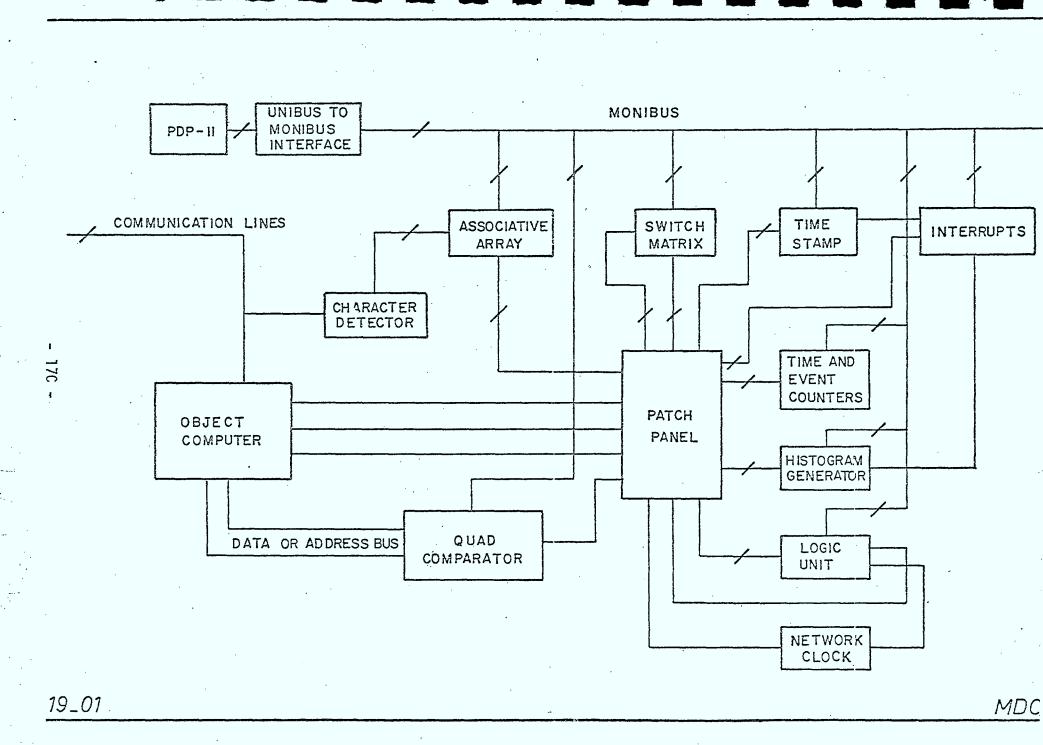

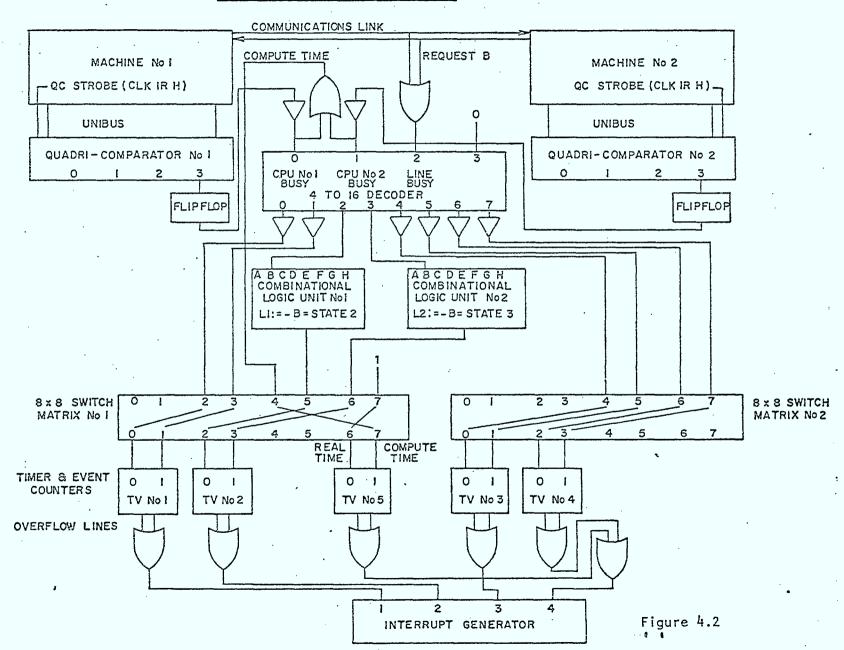

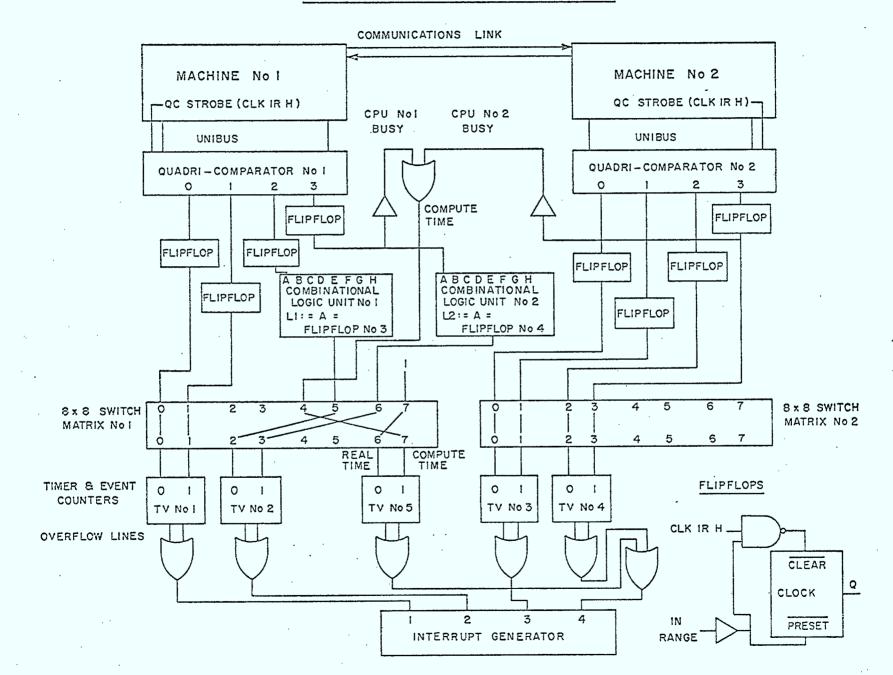

Telephone lines, normally different from those of the object network connect the monitors to the controlling computer. Each monitor consists of one or more of each of the specially-designed components listed in Table 3.1. They are joined by a single bus (called a MONIBUS) that is attached to the controlling computer.

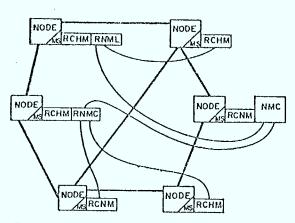

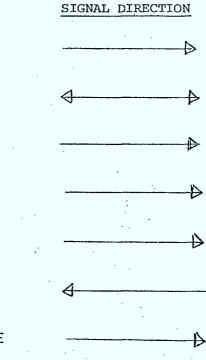

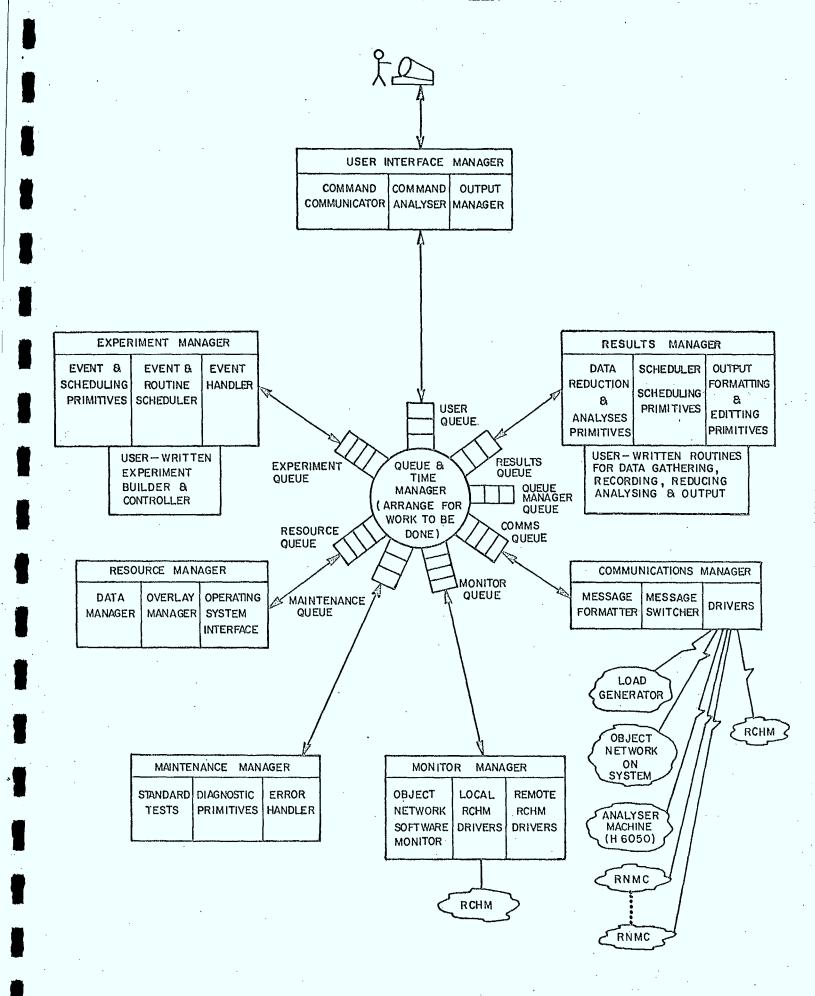

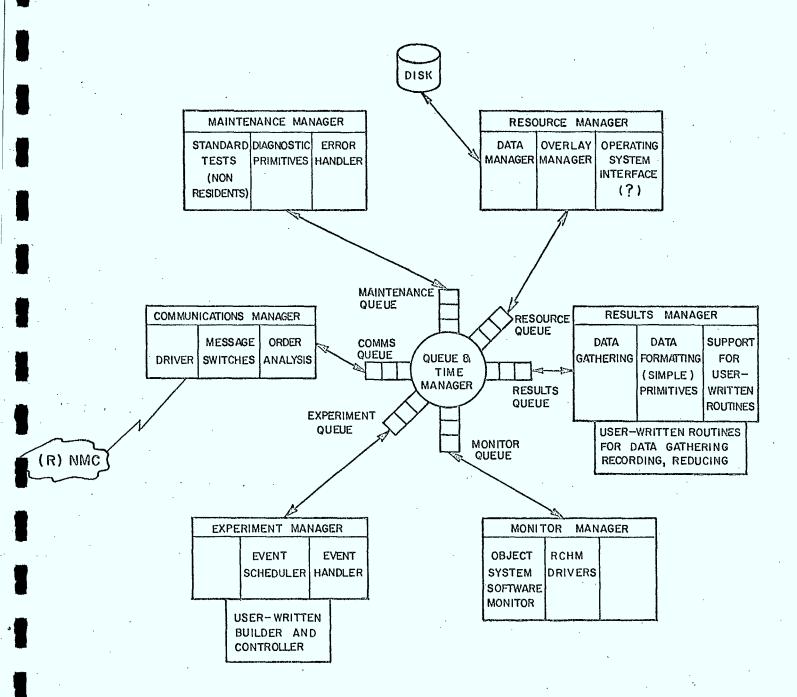

Figure 3.1 illustrates the interconnection of these components to form the monitor. Figure 3.2 illustrates the interconnection of the monitors to observe the activities of a computer network. Note that the communications lines of the network are not used to transmit measurement data or monitor control information. Rather, the controlling computer uses switched voice-grade lines to set up the measurement experiment, then disconnects while the measurements are Periodically, the connection is re-established while made. is collected and/or additional control information is data transmitted. This technique reduces communications costs in measuring geographically distributed networks. For a more complete description of the CNMS, including the software structure, see Appendix C,

| MS   | -  | Measurement Software                        |

|------|----|---------------------------------------------|

| RCHM | ÷. | Remote Computer Controlled Hardware Monitor |

| RNMC | ~  | Regional Network Measurement Centre         |

| NMC  |    | Network Measurement Centre                  |

- 5`-

Fig. 3.2 GENERALIZED MONITOR

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Hardware status                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | , * *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Status of associated software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | In use?                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| NMS              | component                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Design                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | No.<br>Built                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Testing<br>with hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                   |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Complete                                                                                                                                                                                                                                                                                                                                                                                                                                                 | In progress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | DOS-11 version<br>complete; RSX-11<br>version in<br>progress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DOS-11 version<br>nearly complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | DOS-11 version<br>nearly complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | DOS-11 version<br>in use                                                          |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                 | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | yes                                                                               |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                 | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | yes                                                                               |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | version 1<br>complete;<br>version 2 in<br>progress                                                                                                                                                                                                                                                                                                                                                                                                       | version 1<br>being built                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | nearly complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | in progress                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 50 50 50 50 50 50 50 50 50 50 50 50 50 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | no                                                                                |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                 | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | yes                                                                               |

|                  | . 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                 | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | yes                                                                               |

|                  | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                 | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | yes                                                                               |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                 | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | under way                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | no                                                                                |

|                  | *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                 | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | yes                                                                               |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                 | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | complete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | under way                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | no                                                                                |