|+|

Communications Research Centre Canada Centre de recherches sur les communications Canada

An Agency of Industry Canada Un organisme d'Industrie Canada

Held under CIDA sponsored International R & D Collaboration Program between CRC (Canada) and C-DOT (India)

Nov 15 - 24, 1999 CRC, Ottawa Canada

Canadä

CZC

## **TABLE OF CONTENTS**

## WORKSHOP REPORT

Pages 3 – 12

APPENDIX 1 : Brief project descriptions as prepared by CRC

APPENDIX 2: Brief project descriptions as prepared by C-DOT

- APPENDIX 3: Memorandum of Understanding

- APPENDIX 4: Agenda for the second C-DOT technical workshop November 15– 24, 1999

- APPENDIX 5 Copy of Presentation to PSG on CRC / CDOT collaborative activities

- APPENDIX 6 : List of participants

Industry Canada Library - Queen AUG 1 6 2012 Industrie Canada Bibliothèque - Queen

## CIDA PROJECT

#### **TECHNICAL WORKSHOP AT CRC**

#### NOV. 15 – 24, 1999

As part of CIDA Project, and as planned during our first CRC / CDOT workshop (May 31 – June 8, 1999), a second technical workshop was held at CRC from Nov. 24 – 24, 1999. In addition to the workshop, a high level CDOT delegation as well as memers of the Project Steering Group (PSG) were also hosted by CRC.

#### OBJECTIVES

The objectives of this workshop were:

- Start work on the two collaborative projects defined and finalised during the first technical workshop by placing two C-DOT engineers at CRC. The two projects are – a) development of microstrip patch antennas and b) the development of low noise amplifier and a direct digital modulator or demodulator at 20 Ghz for Ka band satellite transceiver using MMIC technology.

- 2. Define and finalise six other projects identified and initiated during the first workshop. These are:

- 155 Mbps satcom Ka band direct receiver

- Broadband applications connectivity (BADLAB)

- Broadband wireless access technology (MILTON)

- Optical components for DWDM and high speed switching

- DSP ASIC technology development for codec implementation

- RF Propagation measurement and studies for satcom and terrestrial wireless

- 3. Finalise and sign a collaborative R and D MOU between CRC and C-DOT.

- 4. Industrial visits specifically in the areas of selected projects with a view to involve Canadian companies for commercialising the results of collaborative R&D, in partnership with Indian companies through C-DOT.

## WORKSHOP PROGRAMME

**Appendix 5** gives the agenda for the workshop, and **Appendix 6** gives the list of participants. The overall program consisted of the following activities:

- Individual project discussions

- MOU finalisation and signing

- Lab visits

- Industrial visits

- PSG meeting and their visit of CRC

## **Project Discussions**

To maximise the use of available time, discussions on the 8 projects were carried out simultaneously in parallel among the respective subject experts from CRC and C-DOT. These discussions were facilitated and co-ordinated by the CRC and C-DOT CIDA Project Team Leaders. The projects are described briefly below and are explained more fully in Appendices 1 and 2, which describe project objectives, deliverables, respective roles for CRC and C-DOT, equipment, personnel and other resources required, time frame including start and completion dates, and methodology.

Appendix 1 provides a description of these projects as prepared by CRC. Appendix 2 gives a slightly more detailed version, as prepared by C-DOT engineers in the context of their own R&D programme.

# 1. Development of low gain L band, S band, and high gain EHF band microstrip patch array antennas.

Although this project was defined during the first workshop, technical specifications were further discussed and revised during this workshop to reflect C-DOT's actual product requirements.

A relatively simple L-band antenna will be designed, fabricated, packaged and tested during the first phase of the project, with C-DOT engineer working at CRC (Nov 1999 – Jan 2000).

At the end of this phase, C-DOT will procure and set up design and testing facilities in India. It is anticipated that the most of the work for the subsequent phases, aimed at the development of more sophisticated antennas, can be carried out at C-DOT with long distance support from CRC through internet.

As of now, the technical progress on this project is quite satisfactory and is on schedule. C-DOT engineer has already simulated, designed, fabricated and successfully tested a single patch.

## 2. EHF MMIC Development – LNA and Direct Modulator

The objectives are to provide design, fabrication and measurement experience and to develop first a low noise amplifier using small signal linear design and then a direct digital modulator or demodulator using more difficult non-linear design. These products are directly relevant to C-DOT's requirements. There is also a strong possibility of involving a Canadian company in this project, which may eventually find an Indian partner for commercialization purposes.

C-DOT engineer is already working at CRC to do the Low Noise Amplifier design. Due to the late arrival of C-DOT engineer (November instead of Sept as originally planned), and the strict time table for foundry fabrication, the collaborative programme has been slightly modified. Only the first stage of the LNA design will be included in the first foundry run. C-DOT engineer will leave CRC in January and will return in April to do the testing and start the design for the remaining two stages. Full design will be submitted for fabrication during the second foundry run.

It is anticipated that the experience gained during the first phase (LNA design, fabrication and testing) will enable C-DOT to undertake the second design mostly in India, with long distance support from CRC, after the procurement of the appropriate design tools and other R&D equipment,

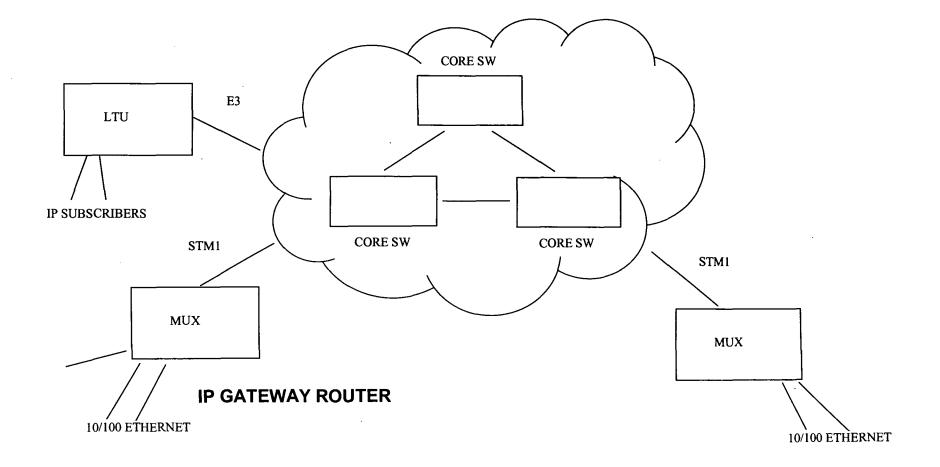

## 3. OC - 3 (155 Mbps) Satcom Ka-band Direct Receiver

CRC has developed a patent pending proprietary direct receiver technology. The current lab prototype system works at 90 Mbps at 20 GHz using QPSK. The objective of this project is to extend the data rate to OC–3 (155 Mbps) and bring the concept closer to commercialization beyond the lab prototype by optimizing the design for cost and performance. Since C-DOT has a very good hardware and ASIC design capability, its main contribution will be in the development of the digital hardware.

As is shown in the CRC's project plan, it is expected that C-DOT engineer will work at CRC in 4-6 week spans, 3-4 times over a period of 15-18 months.

Work on this project has already started. CRC has sent its project description and other technical information to C-DOT. Specific project steps and time line are shown in the gnatt chart contained in the CRC's project description document given in Appendix 1.

## 4. DSP VLSI / ASIC Design

C-DOT has a requirement for an ASIC chip to implement speech coding. Given the use of various coding standards and requirement for multiple channels, it is not clear whether or not developing a customised ASIC starting from scratch is the best solution.

A number of meetings were held to investigate various options including the use of existing DSP's, DSP cores, and the use of advanced DSP ASIC tools to translate DSP algorithms to VHDL (silicon mapping) code.

It was concluded that a 1-2 man months study (carried over 3-4 months) should be conducted to further investigate and analyse various available options and chart out a detailed project plan for the selected path or option. A more detailed description of this study proposal is given in appendices 1 and 2, along with respective roles for CRC and C-DOT.

To carry out this study, it is not necessary for the C-DOT engineer(s) to work at CRC. The study will be carried out over the next 3-4 months.

## 5. Broadband Applications Connectivity (BADLAB)

C-DOT plans to set up a broadband applications demonstration lab (similar to CRC's BADLAB) using its in-house developed ATM switches. The objective of this project is to asist C-DOT to set up such a lab in India and interconnect the two labs (Ottawa and New Delhi) through a transcontinental high speed link to demonstrate collaborative multimedia applications such as collaborative R&D (between CRC and C-DOT) and virtual school.

During this workshop, a C-DOT engineer spent considerable time with CRC's BADLAB manager and CRC's partners including Ottawa's Heart Institute (fro tele-medecine applications) and Ottawa Carleton Research Institute (OCRI).

C-DOT engineer felt that as a result of these meetings and discussions, he has enough information to start setting up a similar lab in India and no further action is needed in this regard at the moment other than possible consultation through internet.

Once C\_DOT has set up its lab, it will contact CRC to inititate the second phase of this project in which BADLAB in Ottawa will be connected to the equivalent lab in India to demonstrate multimedia type applications such as virtual school and collaborative R&D,

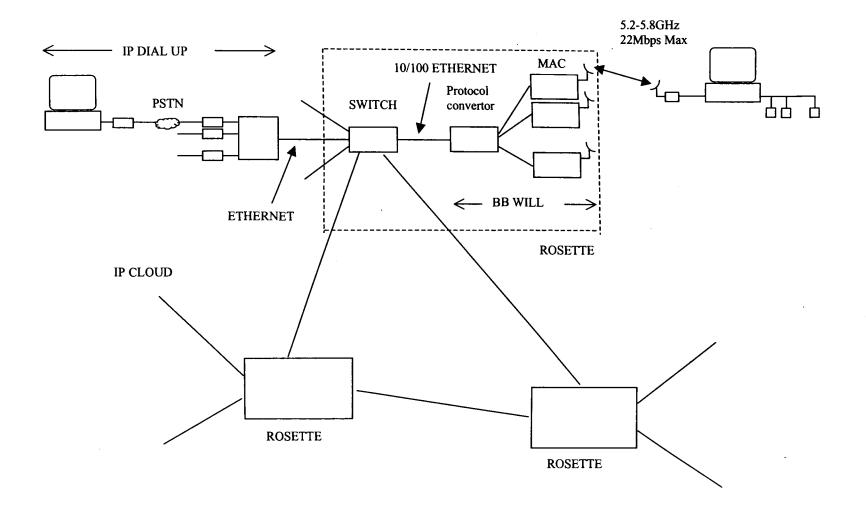

## 6. Broadband Wireless Loop using 5 GHz (Known as MILTON at CRC)

CRC has developed a patent pending low cost proprietary system for implementing broadband wireless access at the local level, as an alternative to the more expensive

option of installing optical fiber or using LMDS / LMCS system using much higher frequencies. In fact, this system may be more relevant and useful to India where the existing infrastructure is not nearly as developed as in the developed countries and the other alternate technologies such as LMDS and hybrid cable modem are not as developed yet. For these reasons, C-DOT showed a keen interest in this technology as a wideband access mechanism for its ATM switches.

Since MILTON uses IP, C-DOT plans to develop an ethernet switch by developing a new ethernet switch line card in its ATM Mux.

Once CRC has finalised its system specifications over the next few months, C-DOT could start the development of its ethernet card and other collaborative activities as outlined in the detailed project description.

In the mean time, it may be useful for a C-DOT hardware engineer to participate in the remaining development of the MILTON system to gain first hand experience. A description of duties and required skills has been sent to C-DOT already.

## 7. Optical Component Development for DWDM and High Speed Switches

C-DOT has already embarked upon the design and development of a DWDM system. CRC has developed a number of innovative technologies and components including grating-based and other components such as add/drop filters, dispersion compensation components, fused fiber couplers, optoelectronic switches, polymer based optical components including wavelength demultiplexers, wavelength demultiplexers integrated with photodetector array, wavelength multiplexers and demultiplexers using glass substrate. CRC's expertise in the optical components can be coupled with C-DOT's expertise in system design to develop a state-of-the-art DWDM system.

C-DOT is quite interested in pursuing a number of these areas. However, before selecting a particular area(s), C-DOT would like to develop a complete commercialisation plan possibly in partnership with some of its Indian industrial partners. CRC and C-DOT will further interact in these areas before specific project(s) can be finalised.

C-DOT will get back to CRC on is action plan for pursuing fiber gratings, dispersion compensation components and fused coupler technology. CRC will send more information on WDM system related technologies and optoelectronic switches to C-DOT.

## 8. Propagation Studies

Communications equipment supplier and service providers generally rely on existing propagation models which are generally based on measurements done for the developed countries, to derive system specifications for the Indian market. Since climatic conditions in India are quite different, use of such models often results in either over specifications (meaning higher system costs) or service gaps. There is, therefore, a need for carrying out propagation measurements in India and derive the appropriate models, especially in light of expected explosive growth in the wireless services.

While the immediate objective of this project is to provide experience in designing experimental methodologies, apparatus, planning field measurements, data acquisition, software development, data analysis, and interpretation at a selected frequencies, the longer term objective is to enable C-DOT to set up propagation studies program in India to allow the orderly development and installation of wireless technologies and systems.

Discussions were held on two sub projects within this area.

## A. Ka band Satellite Link Propagation Studies

C-DOT has developed VSAT communication systems like ISD –16 and ISD – 64 for existing lower frequency satellite systems. India will shortly lauch a new satellite with Ka band beacon which will allow earth-space propagation measurements and studies. These will be required in the design and employment of future Ka band VSAT and other satellite systems.

## **B.** Terrestrial Propagation Studies in L/S bands

These are required for the implementation of C-DOT's TDMA, DECT and CDMA systems.

While it is quite evident that propagation studies are essential for the orderly implementation and growth of wireless services in India, and C-DOT is one of the most competent body to carry out these studies, it is not clear whether such work falls within C-DOT's mandate.

C-DOT will discuss this issue internally and possibly with other organisations including DOT and will get back to CRC for a possible plan of action.

## **MOU Finalisation and Signing**

A formal MOU for R&D collaboration between CRC and C-DOT was discussed, finalised and signed by Gery Turcotte, CRC's President and Dr. K N Gupta, Executive Director of C-DOT, on November 19, 1999 at a brief signing ceremony held at CRC.

Apart from CRC and C-DOT personnel, the event was also attended by representatives from CIDA, IC, and Indian High Commission. Appendix \_ gives a copy of this MOU and the press release issued for the occasion.

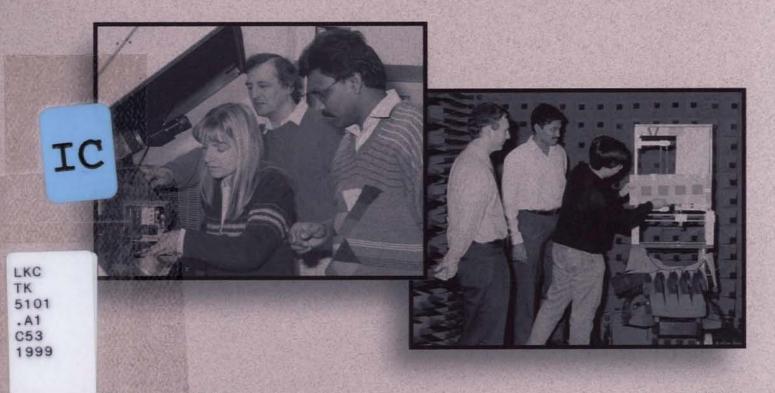

## Lab Visits

In addition to lab visits and discussions by the C-DOT engineers, the following labs and technologies were shown to the C-DOT senior management team.

| MMIC / MHMIC Microwave Lab<br>VLSI / ASIC Lab   | Dr M Stubbs / Dr V Swarz<br>Dr V Szwarc |

|-------------------------------------------------|-----------------------------------------|

| Microstrip Patch and other Antennas             | M Cuhaci                                |

| BADLAB (Broadband Applications                  | M Savoie                                |

| Demonstration Lab)                              |                                         |

| Optical Network Technologies                    | Dr E Berolo                             |

| <b>Optoelectronics Materials and Components</b> | Dr. Julian Noad                         |

| Optical Communications                          | Dr Ken Hill                             |

| Satcom Ka band direct Receiver                  | M Caron / D Hindson                     |

| Satellite Suitcase Terminal                     | C Pike                                  |

| Broadband Wireless Access (MILTON)              | J Sydor                                 |

| Terrestrial Wireless Test Bed                   | Luc Boucher                             |

The objective here was to give C-DOT's senior management team a first hand exposure of CRC's capabilities and expertise in the areas selected for collaboration, in order to gain their support and acceptance.

## **External Visits**

As per our original CIDA proposal, a small number of external visits were arranged for the C-DOT's senior management team. They visited the following organisations.

## Nanowave / Remecs Inc., Toronto

Nanowave has had considerable collaboration with CRC in the past and is currently the leading edge Canadian company in the area of MMIC / MHMIC technologies. It designs, manufactures and sells RF components, subsystems and systems for the wireless market. Both C-DOT and Nanowave showed keen interest in mutual collaboration.

## Harris Canada, Montreal

C-DOT is looking to acquire RF technology to meet its immediate needs for the development of mobile base stations required by C-DOT. Harris represents a good candidate for such technology transfer, since Harris is not particularly interested in setting up a manufacturing plant in India and would prefer an Indian

partner for exploiting its technology through a suitable collaborative and / or licensing arrangement with C-DOT.

## Larcan, Toronto

Larcan was selected to show C-DOT its prototyping and manufacturing facilites which are of similar scale as C-DOT's. Larcan also explained the advanatages of working with a government lab like CRC. C-DOT found this session quite informative and useful.

## Mitec, Montreal

Mitec designs, manufactures and sells RF front end subsystems to major cellular and PCN base station vendors. Although no areas could be identified for immediate collaboration, C-DOT may wish to work with this company to enhance its RF capabilities.

## NRC, Ottawa

C-DOT visited IIT (Institute of Information Technology) and IMT (Institute of Microstructural Sciences). No immediate mutual interest was identified.

Since these were meant to be only exploratory kind of visits with no direct and clear objectives, the number of visits were kept small. Both CRC and C-DOT have large number of industrial partners. Given C-DOT's initial interest in collaborating with Canaidan companies either itself or along with its Indian industrial partners, CRC will be willing to arrange for expanded industrial interaction if required and requested.

## Lunch by C-DOT

Dr. Gupta, Executive Director of C-DOT, hosted a special lunch for CRC and C-DOT research teams which participated in this workshop. Attendance by some 35 CRC researchers is an indication of strong interest and desire in this project.

## PSG (Project Steering Group) Meeting - November 16, 1999

Jeet Hothi (CRC) and Jayant Bhatnagar (C-DOT) made a presentation to the CIDA Project Steering Group meeting on the current status of CRC / C-DOT collaborative activities (see Appendix \_ for a copy of their presentation). The presentation was well received and PSG members seemed pleased with the progress and the manner in which collaboration has taken place so far.

### Visit of CRC by PSG , November 20, 1999

A lively discussion took place after Graham Taylor (CRC) gave an overview of CRC's research labs and its collaborative activities with industry and other national and international organisations. PSG members were then given a tour of BADLAB (Broadband Applications Demonstration lab) and DFL (Satellite integration and testing) lab. PSG member reaffirmed their satisfaction with the R&D collaborative part of the overall CIDA project.

## Visit of C-DOT by CRC

It was strongly felt that the next project review and discussion meeting should take place at C-DOT. This will allow CRC researchers a direct and first hand appreciation of C-DOT's laboratories, expertise, and technical requirements. The meeting is tentatively planned for Oct. / Nov. , 2000 time frame. An appropriate programme and agenda will be jointly developed before the meeting.

## ACKNOLEDGEMENTS

we would like to thank:

C-DOT engineers for their participation, keen interest, long working hours extending late into evenings, and co-operative and pleasant attitude;

George Wieringa of CIDA for his strong support and attending the MOU ceremony;

Claude Dostlar and Aaron Baillie of IC for their on-going support and encouragement for this project;

CRC's President for his moral and general support;

CRC VP's, Research Managers, Director of Marketing, Director of Informatics, Engineering and Scientific staff for their enthusiastic participation and co-operation;

Sylvie Boileau, Lisa McWilliam, Marnie Johnstone (Communications) and John Brebner (Creative Visual Services) of CRC to arrange for the MOU ceremony, photographs and other communications related activities;

Special thanks to Miriam Poole of CRC to take care of CRC's hospitality in such a pleasant manner;

Neelam Mukhija, a technology transfer and industry consultant for his support in organizing and conducting the entire workshop.

Finally, we would like to extend our special thanks to Dr. K N Gupta of C-DOT and his senior managers – Dr P K Bhatnagar and Vijay Madan for taking time from their busy shedule to visit CRC and also for hosting a special lunch for the research teams.

Jeet Hothi Head, Industrial R&D CRC

December, 1999

12

## **APPENDIX 1**

## BRIEF PROJECT DESCRIPTIONS AS PREPARED BY CRC

PROJECT TITLE: Microstrip Patch Antenna Development

DESCRIPTION: This project will allow a C-DOT engineer to gain experience in Microstrip Patch Antenna technology through the development of different type microstrip antennas. The project will provide knowledge in the hardware and software tools necessary for the development of microstrip antennas, the design and measurement procedures involved and some of the advantages and limitations of the technology. The project will also provide knowledge on how to setup a basic Microwave Antenna Measurement Laboratory.

#### SPECIFIC OBJECTIVES:

The objectives are planned to provide design, fabrication, packaging and testing experience for microstrip antennas in a progressive manner. The following Microstrip Antennas for Communication System at different frequencies will be designed during this project:

- 1) A low gain microstrip Linearly Polarized (LP) antenna around 2GHz,

- 2) A low gain microstrip Circularly Polarized (CP) antenna around 2GHz,

- 3) A medium gain X or Ku-band microstrip antenna for LP operation,

- 4) A Ka-band microstrip antenna for LP operation.

#### **KEY PERSON AT CRC:**

Michel Cuhaci

#### KEY PERSON AT CDOT: TBD

#### TIME FRAME/DURATION:

This activity will extend over two years, in three 6 months periods.

#### **RESOURCES**:

#### CRC – VPRS/RAAT

Pentium workstations with Ensemble and/or IE3D software. Antenna prototype fabrication, including material, layout, mask, etching and assembly. Antenna measurement facility 18 man/month

CDOT – 1 microwave design engineer Pentium workstations with TBD antenna design software

#### DELIVERABLES/OUTPUTS:

Reports – reports on simulated and measured microstrip antenna characteristics. Publications – possible Prototypes – prototype microstrip antennas Training – microstrip antenna design/measurement procedures Technology transfers – microstrip antenna design concept

#### PROJECT TITLE: EHF MMIC Development

DESCRIPTION: This project will allow C-DOT engineers to gain experience in GaAs MMIC technology through the development of MMIC chips. The project will provide knowledge in the hardware and software tools necessary for the development of MMICs, the design and measurement procedures involved and some of the advantages and limitations of the technology.

#### SPECIFIC OBJECTIVES:

The design and measurement of two EHF MMIC components for transmitter and receiver communications systems will be accomplished. The first, a low noise amplifier, will provide small signal, linear design experience and the second, a direct digital modulator (or demodulator), will provide non-linear design experience.

KEY PERSON AT CRC: Valek Szwarc

KEY PERSON AT CDOT: Vinay Madhav

#### TIME FRAME/DURATION:

The relatively long design and fabrication times, and the constraints of fiscal year expenditures, dictate that this activity will extend over two years.

One possible timeframe is as follows:

| LNA design (1 st stage)    | 15/11/1999 - |           |

|----------------------------|--------------|-----------|

| MMIC fabrication           | 20/12/1999 - | 31/3/2000 |

| Measurements               | 1/4/2000     | 31/4/2000 |

| LNA design/revision/review | 1/5/2000 -   | 1/6/2000  |

| MMIC fabrication           | 1/6/2000     | 1/9/2000  |

| Measurements               | 5/9/2000     | 15/9/2000 |

| Modulator Design           | 1/6/2000-    | 1/12/2000 |

| MMIC fabrication           | 1/12/2000-   | 31/3/2001 |

| Measurements               | 1/4/2001-    | 14/4/2001 |

Development of the LNA and modulator will be carried out by C-DOT engineer in consultation with CRC staff. The work will be carried out at C-DOT and/or CRC depending on circumstances and the ease or difficulty experienced in carrying out consultations electronically.

#### **RESOURCES**:

#### CRC – Sun workstations with Libra MMIC fabrication

#### CDOT – 1 or 2 microwave design engineers Workstations with Libra

#### DELIVERABLES/OUTPUTS:

Reports –reports on simulated and measured MMICcharacteristicsPublications – possible publications on modulatorPrototypes –three MMIC devicesTraining -MMIC design/measurement proceduresTechnology transfers – MMIC modulator concept

#### CRC RESOURCES

FY 99/00 1 Libra Workstation Foundry fabrication 3 weeks Res.- 04 1 month ENG-03 support 3 weeks EL-05 support Libra maintenance, wafer prober & test equipment usage Microwave probes

FY00/01

Foundry fab (LNA) Foundry fab (Modulator) 3 weeks Res.-04 2 month ENG-04 support 3 weeks EL-05 support Libra maintenance, wafer prober & test equipment usage

#### PROJECT TITLE: DSP VLSI Design

BACKGROUND: The implementation of communications systems, speech vocoders, error correction devices etc. frequently originates with the development and refinement of sophisticated algorithms in such languages as C or C++. Furthermore, the initial proof of concept or actual production implementation is frequently carried out on suitable general purpose processors or DSP processors that can effectively execute the compiled software. To achieve optimal performance the actual implementation may require a recoding of the algorithms in assembler language. In instances where performance and/or cost dictate it an ASIC implementation may be necessary. In considering the economics of an ASIC implementation it is imperative to consider the cost and time associated with the execution of the design. Ideally, for designs that have been developed in C or C++ and functionally tested one would like to be able to go directly from the programming language to a VHDL implementation. Some steps in this direction have been taken by Frontier Design Inc. with their DSP Station. The company has for example claimed to have implemented the G.726 ADPCM Speech Codec with this tool. The implementation in question requires 5k gates (plus memory) and is capable of operating in full duplex mode.

BRIEF DESCRIPTION: C- DOT has identified a number of applications whose implementation is contingent on the implementation of a vocoder that meets the G. 729 standard for 8 kbps voice compression. Furthermore in the applications of interest the vocoder module/ASIC would have to handle up to 24 voice channels. To implement such a module the following options have been identified for Phase 1:

- i) Design of ASIC around commercial macrocells (G. 729 macrocell, DSP macrocell, processor macrocell).

- ii) Direct implementation of vocoder algorithms in VHDL

- iii) Implementation of vocoder algorithms by means of newly available CAD tools capable of mapping algorithms in C or C++ into synthesizable VHDL code.

The proposed work at CRC is intended to investigate viability of options (i) and (iii) by:

- Identification of DSP ASIC tools: through an evaluation of a commercially available DSP/ASIC CAD tool of choice (e.g. DSP station from Frontier Design) in terms of its suitability for rapid prototyping through mapping of C and/or C++ code into synthesizable VHDL

- Identification of DSP core vendors: determination of commercial availability and suitability of vocoder, DSP and processor macrocells

- Analysis and Conclusions

On the side of C-DOT the work will involve the following tasks:

- Estimation of CODEC complexity

- Identification of DSP ASIC tools

- Identification of DSP core vendors

- Identification of complete solution providers

- Analysis and Conclusions

To assure close collaboration and effective exchange of information both C-DOT and CRC will jointly address two of the above areas as specified and collaborate on drawing up the Analysis and Conclusion.

Should the initial investigation point to the viability of using advanced CAD tools for the mapping of algorithms from C/C++ into VHDL then CRC and C-DOT may consider a joint Phase 2 R&D activity to investigate further the design methodology and relevant tools for the mapping of vocoder algorithms from C/C++ into VHDL with view to evaluating their potential and limitations. At this point we can only estimate that a Phase 2 activity would require the participation of two to three engineers. One ASIC designer from CRC and one or two DSP/ASIC engineers with vocoder experience from C-DOT.

SPECIFIC OBJECTIVES:Near term activity (Phase 1):identify R&D options andobjectives in the context of C-DOTs and CRC's respective goals and missions.KEY PERSON AT CRC:V. SzwarcKEY PERSON CDOT:Chandrashekar B. U.Chandrashekar B. U.TIME FRAME DURATION: Four months. (Phase 1). Project can be initiated as early asDec. 1999.

**RESOURCES:**

CRC: One VLSI Engineer

-

Workstation, CAD tools: Mentor Graphics, Xilinx FPGA tools

CDOT: DELIVERABLES / OUTPUTS: Report on work done.

PUBLICATIONS: possible publication – will depend on depth of analysis and choice of representative circuits.

TRAINING: N/A

TECHNOLOGY TRANSFER: Knowledge obtained in course of study.

CRC Resources

Four weeks Eng. 04 effort One week Eng. 06 effort

Software -lease (if required)\*

\* The current plan calls for using evaluation software from Frontier Design to carry out this study. If evaluation software is not available for the necessary period it may be necessary to lease it for several weeks.

## STATEMENT OF WORK FOR PROJECT:

## 155 Mbps SATCOM K-BAND DIRECT RECEIVER

#### 1. BACKGROUND

CRC/RSS has entered into an agreement with C-DOT to develop a prototype direct receiver in the 20 GHz band based on a 5-port junction front end and the novel I&Q regeneration technique developed by RSS. The I&Q regeneration technique compensates for the phase and gain imbalance introduced in the receiver front end as well as most of the phase imbalance introduced at the transmitter and generates the baseband I&Q signals. The receiver is to be capable of receiving 155 Mbps QPSK modulated signals and the project covers the electronics from the front end down to and including the generation of the baseband I&Q signals. CRC/RSS will train C-DOT personnel in order for them to be able to re-create and re-design the electronics as required in future projects.

This document provides detail on the tasks to be executed and identifies the contribution and deliverables of each party. A schedule is proposed as a guideline. Any deviation from this schedule due to any constraints will have to be discussed by both parties and agreed before to be put in force.

### 2. OBJECTIVES OF THE PROJECT

The project aims to develop a lab bench prototype direct receiver and required testing hardware adapted to the C-DOT product requirement for their ATM backbone satcom terminals. A second aim is to train C-DOT personnel such that further design and/or re-design activities can be undertaken by them as required in future projects.

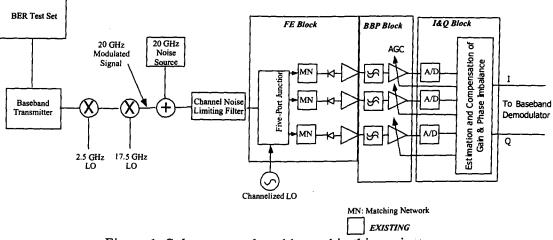

Figure 1 shows a block diagram of the hardware addressed in this project. There are three main functional blocks in the receiver chain. First the front end made of a 5– port junction, single ended mixers and a section of video amplification. This block is referred to as the "front-end" or FE block. The second block consists of the AGC circuit and the anti-aliasing filters. It is referred to as the "baseband processing" or BBP block. Finally the I&Q regeneration block referred to as the I&Q block constitutes the third element of this project.

Figure 1: Subsystem to be addressed in this project.

In order to be able to test the receiver, a number of other elements are required. The baseband transmitter is to be developed under a development contract to industry and managed by CRC/RSS. CRC's existing up-converter chain shaded in Figure 1 is to be used to generate the 20 GHz modulated signal from the baseband transmitter output. CRC's existing wideband channel noise generator also shaded in Figure 1 is to be used in this project. C-DOT I&Q demodulator is to be used in the final integration and testing of the receiver. Various test instruments are to be used in the project. In particular there is a need for a BER test set operating at up to 155 Mbps, signal sources at 2.5 GHz and 17.5 GHz, spectrum analyzer, oscilloscope and logic analyzer.

#### 3. TASKS

In this section the various tasks of this project are described and the contribution and deliverables are identified.

#### 3.1 TASK 1: RECEIVER SYSTEM DESIGN DOCUMENT

This task is to be conducted by C-DOT. This document identifies the functional requirements of the end product sought for by C-DOT in their ATM backbone satcom terminal. The document provides detailed specifications of the form, fit and functions of the receiver as well as critical interfaces. It will be the main input to Task 2.

#### 3.2 TASK 2: TEST BASEBAND TRANSMITTER AND DIRECT RECEIVER SYSTEM DESIGN DOCUMENT

This task consists in developing the system design document of the test baseband transmitter and the direct receiver lab bench prototype to be developed in this project. It provides detailed specifications of the form, fit and functions of the baseband transmitter, the direct receiver and its subsystems. It takes as input the receiver system design document of Task 1 and generates a document defining the desired system from this project. This task is jointly conducted by CRC/RSS and C-DOT.

#### 3.3 TASK 3: TEST PLAN DOCUMENT

This task jointly conducted by CRC/RSS and C-DOT defines the tests to be performed on each of the receiver functional blocks identified above as well as on the baseband transmitter and the integrated system to ascertain that the project objectives are met. The document includes as a minimum a section defining the test requirements. It is not intended in this task to develop a test plan as elaborate as in a final product test plan that is to say that the procedure used to test the specifications will not be described unless critical to the testing. For standard tests, good engineering practice will be used and testing techniques will be reported in the test reports.

### 3.4 TASK 4: I&Q REGENERATION ALGORITHM FINAL DESIGN

Task 4 is to finalize the design of the algorithm using Matlab and/or SPW computer tools to meet the requirements identified in the system document resulting from Task 2. The task will be conducted jointly by CRC/RSS and C-DOT with RSS having the lead. Consideration of ASIC requirements will be identified by C-DOT while CRC/RSS role will be to design the algorithm to meet the functional specifications of the I&Q block. The output of this task is an I&Q block implementation report with sufficient details to enable the fabrication of the ASIC by C-DOT. The SPW model of the final design will be delivered to C-DOT which will undertake the development and fabrication of the ASIC in Task 5.

# 3.5 TASK 5: I&Q REGENERATION BLOCK ASIC DESIGN AND FABRICATION

This tasks takes the SPW model of the final design of the algorithm and the implementation report of Task 4 and the design and fabrication of the ASIC is carried out by C-DOT. C-DOT will provide to CRC the final VHDL code of the ASIC fabricated. C-DOT will conduct the basic testing of the ASIC and will provide CRC/RSS with 10 samples once good operation is confirmed. One of these samples will be used in the final integration and testing of the receiver chain. Associated specifications and documentation will also be provided to CRC/RSS by C-DOT.

#### 3.6 TASK 6: FRONT END DESIGN AND FABRICATION

Task 6 consists in designing the 5-port junction together with the single ended mixers and the video amplifiers. This task is to be conducted jointly by CRC/RSS and C-DOT. Due to cost sensitivity of the final product, C-DOT

will specify the substrate to be used in developing the junction and will design the single ended mixer circuit to be used. CRC/RSS will design the junction based on that substrate and according to the specifications identified in the system document (Task 2). Fabrication cost is estimated at \$5K. Once C-DOT has finalized the design of the single ended mixer circuit and CRC/RSS, the design of the junction, C-DOT will provide their circuit design to CRC/RSS (e.g., Gerber file or equivalent) and a final integration and fabrication will be made at CRC/RSS. The video amplification circuit design and implementation will be carried out jointly by both parties. The output of this task is a FE block fully functional with a test report according to the test plan (Task 3).

# 3.7 TASK 7: AGC AND ANTI-ALIASING FILTER DESIGN AND IMPLEMENTATION

This task is to design the AGC circuit to meet the system document specifications (Task 2) and the corresponding anti-aliasing filters. C-DOT is to take the lead on the design of the AGC circuit. Once finalized, CRC/RSS will implement and test the AGC circuit according to the test plan to ascertain its good operation. CRC/RSS will design and implement the anti-aliasing filters and will provide a test report as defined by the test plan.

# 3.8 TASK 8: I&Q BLOCK AND DEMODULATOR INTEGRATION AND TESTING

This task consists in designing and developing a PCB to include the I&Q ASIC and glue logic required to interface to the AGC and I&Q demodulator to be provided by C–DOT. The schematic diagram is to be provided by C–DOT to CRC/RSS that will fabricate the PCB. Both parties will perform jointly the assembly and testing of the PCB and generate a test report as required.

# 3.9 TASK 9: BASEBAND TEST TRANSMITTER DESIGN AND DEVELOPMENT

This task is to be conducted by CRC/RSS. A statement of work will be created to specify the functional and interface specifications of the baseband transmitter. Then a request for proposal will be issued and a contract awarded to a suitable private company to undertake the development of this baseband transmitter. The contract will be managed by CRC/RSS and is estimated at \$60K. Two fully populated boards and two unpopulated boards will be delivered to CRC/RSS of which one of each will be sent to C-DOT. A copy of the final report of the contract will be sent to C-DOT. If there is a need to perform adjacent channel interference tests (TBD), more units may need to be integrated.

# 3.10 TASK 10: CHANNEL NOISE GENERATION AND FILTER DESIGN AND IMPLEMENTATION.

CRC/RSS has designed and implemented a channel noise generator and noise limiting filter for their previous prototype work. This task consists in CRC/RSS providing C-DOT with the design details/specifications of the channel noise generator and a noise limiting filter to C-DOT with associated documentation and test reports.

#### 3.11 TASK 11: RECEIVER FINAL INTEGRATION AND TESTING

This task consists in integrating the three functional blocks together and to conduct receiver tests. This task will be conducted jointly by C-DOT and CRC/RSS. A test report according to the test plan will be generated in this task. Acceptance of the test report will conclude this project.

#### 4. SCHEDULE AND RESOURCES

Figure 2 shows the schedule for this project. The schedule identifies CRC/RSS human resource requirement for each task as well as the time span of each activity. It also indicates when C-DOT personnel is expected to be available at CRC/RSS.

#### 155 Mbps SATCOM K-BAND DIRECT RECEIVER

-

| Task                                                 | Effort from CRC/RS | Dec-99 | Jan-00 | Feb-00 | Mar-00 | Apr-00 | May-00 | Jun-00 | Jul-00 | Sep-00 | Oct-00 | Nov-00 | Dec-00 | Jan-01 | Feb-01 | Mar-01 |

|------------------------------------------------------|--------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| #1: Receiver system design document from C-DOT       |                    |        | _      |        |        |        |        |        |        |        |        |        |        |        |        |        |

| #2: Prototype receiver and baseband test transmitter | 0.5 p-m            |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |

| system design document                               |                    |        |        |        |        |        |        |        |        |        |        |        | _      |        |        |        |

| #3: Development of test plan                         | 0.5 p-m            |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |

| #4: I&Q regeneration algo final design               | 3 p-m              |        |        | _      |        |        |        |        |        |        |        |        |        |        |        |        |

| #5: ASIC design and fabrication                      |                    |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |

| #6: 5-port junction design&fabrication               | 2 p-m              |        |        |        |        |        |        |        | ~      |        |        |        |        |        |        |        |

| Mixer circuit design                                 |                    |        |        | _      | _      |        |        |        |        |        |        |        |        |        |        |        |

| Integration and video amplifiers                     | 1 p-m              |        |        |        |        |        |        |        |        |        |        | _      |        |        |        |        |

| #7: AGC circuit design                               |                    |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |

| AGC implementation and test                          | 0.75 p-m           |        |        |        |        |        |        |        |        |        |        |        |        |        |        | ,      |

| AAF design, implement and test                       | 0.25 p-m           |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |

| #8 : I&Q and demod integration                       | 1 p-m              |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |

| #9: Test transmitter dev. Contract                   | 1 p-m              |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |

| #10: Prototype receiver integration & test           | 3 p-m              |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |

| Management                                           | 1 p-m -            |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |

| Total effort                                         | 14 p-m             |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |

| RSS November 29, 1999                                |                    |        |        |        |        |        |        |        |        |        |        |        |        |        |        |        |

\_\_\_\_\_

Note: C-DOT personnel at CRC

Figure 2 : Schedule for the project

## DRAFT/DRAFT /DRAFT

### Project Definition/Ka-Band Propagation Concept Definition

#### **Brief Description:**

Ka-band earth-space propagation measurements in India will be feasible in the near future with the launch of a satellite carrying Ka-band beacons. Scientific merits and potential applications from C-DOT's point of view, along with technical requirements for implementation and conduct of such measurements, should be evaluated prior to initiation of a measurement program.

### **Specific Objectives:**

Objectives of the concept-definition phase include:

- Gather technical information needed for design of measurements, such as location of satellite, stationkeeping parameters, and relevant beacon specifications, along with site-specific (e.g., climatic) aspects and benefits of the measurements (C-DOT);

- Survey existing propagation facilities/institutes, and relevant propagation measurement results for India, and determine if collaborative alliances with other Indian organizations are beneficial for this project (C-DOT);

- Specify measurement goals, evaluate general measurement approaches, identify potential sources for requisite equipment, and estimate corresponding costs (C-DOT/CRC);

- Summarize software requirements for equipment control, data collection and analysis (CRC/C-DOT); and

- Conceptually design a Ka-band propagation measurement facility to achieve objectives of the project (CRC/C-DOT). [Responsibilities could be reversed here if C-DOT prefers.]

| Key Person at CRC:   | D.V. Rogers                         |

|----------------------|-------------------------------------|

| Key Person at C-DOT: | ?                                   |

| Time Frame/Duration: | 6 calendar months                   |

| Resources:           | TBD                                 |

| Deliverables:        | Report on Concept Phase (C-DOT/CRC) |

#### PROJECT TITLE: Development of Facilities for Propagation Research

DESCRIPTION: This project will allow a C-DOT engineer to gain experience in the field of radio propagation. This project is meant to acquaint the C-DOT engineer with the various phases of propagation of propagation research.

#### SPECIFIC OBJECTIVES:

1 The determination of the information needed by a project and to be obtained by measurements, 2- The determination of the experimental methods needed to obtain the required information, 3- The determination of the experimental apparatus needed to perform the experiments, 4- The design of the experimental apparatus, 5- The fabrication and testing of the experimental apparatus, 6- The planning of field measurements, 7- The taking of field measurements, 8- Data acquisition and data storage, 9-Software development for the purpose of data processing., 10-Data processing, 11- Interpretation of results, 12- Preparation of results for use in applications.

#### **KEY PERSON AT CRC:**

Dr. Jules LeBel

#### KEY PERSON AT CDOT:

TBD

#### TIME FRAME/DURATION:

This activity will extend over a period of two years, in three 6 month periods.

#### **RESOURCES**:

#### **CRC-VPRS**

Access to propagation laboratories and access to advice from propagation specialists. UNIX workstations and Pentium workstations.

C-DOT- 1 propagation engineer. Pentium and/or UNIX workstations.

#### DELIVERABLES/OUTPUTS:

Report on stay at CRC. Report(s) on field measurements. Publications – possible Training - propagation measurement techniques Training – propagation data interpretation

## MILTON (<u>Mi</u>crowave-<u>L</u>igh<u>t</u> <u>O</u>rganized <u>N</u>etwork)

## A Project of the Research Broad Band Wireless (RBBW) Group

The Broad Band Terrestrial Wireless Group at the Communications Research Centre undertakes the investigation, research, and development of wireless techniques used to support high capacity digital communications links.

## Objective:

The objective of the MILTON project is to develop new wireless techniques and technologies capable of providing data delivery densities of 100 to 1000 Megabits per second per square kilometer of urban area. This technology will be highly bi-directional supporting high speed data exchanges between subscribers and providing multi-media interactivity between users. As designed, system will distribute high quality video and audio information as well as standard internet-type data.

Because MILTON technology is wireless, there is no dependence on wire-line connections to make it fully functional. It is felt this technology can be quickly implemented in regions not having a coaxial (TV) cable and/or telephone line infrastructure. One of the objectives of this work is to develop technology for the export market. Realizing the sensitivities of such markets to cost, most of the technical objectives of the MILTON project can be achieved using existing technology taken from the satellite TV, personal computer, and the cellular/1900 MHz PCS telephony components industry.

## Applications:

Applications for this technology include wireless telephony using TCP/IP, broad band Internet access, video-on-demand, tele-presence, live music and theatre distribution, etc. In fact, any cultural, social, or educational event that can be produced, stored or recorded as electronic data and packaged as web-site information will be easily distributed by MILTON.

What differentiates MILTON from other (principally cable TV and telephone internet modem) technologies is its distributed network architecture. High bandwidth producers of information will no longer have to access central switching offices via dedicated broad band links so that their information becomes available to the network at large. It will be possible for subscribers to set up the equivalent of radio stations, television stations, video rental shops, and other audio/visual/multimedia resource centres from their homes and small offices. As a consequence, the high infrastructure costs associated with such information distribution endeavors (largely due to requirement for dedicated high band width links and associated network access costs) are mitigated.

MILTON is embodied within two physical subsystems that need to be described in order to appreciate the intended applications of the overall system.

First of all, MILTON is a microwave radio system that uses very low power signals to relay data between a hub antenna and urban users located within a 1-2 kilometers radius of the antenna (for rural the distance can be up to 5-10 km radius). Different deployment techniques are used for urban and rural environments. In an urban environment, there is the expectation of obstruction by foliage and buildings, hence the operational radius is smaller. In a rural environment, less obstruction is expected, thus resulting in longer communications distances. For rural applications it is envisaged that a single hub will provide the data requirements of a sparse, widely distributed population (within ~10 km of the hub). In an urban environment, numerous hubs would be required to meet the requirements of a higher population density.

The hub consists of an integrated antenna array, digital radio, and digital switch mounted on a power pole, lamp standard, or medium height (~5 story) building. The coverage pattern of the hub antenna is best visualized as rosette of antenna beams, each beam being an oblong radio micro-cell. Typically a rosette contains 32-48 micro-cells. This configuration of cells allows a very high data carrying capacity. Each fully loaded MILTON rosette is capable of receiving, transmitting, and switching in the order of 1000-1500 Megabits of information per second. This is equivalent to about 800-1000 simultaneous high quality video conferencing sessions; about 300-500 simultaneous video-on-demand sessions; or 1500-15000 unblocked Internet sessions running at modem speeds in excess of 100 kilobits per second (a conventional phone modem supporting Internet runs at about 20 to 60 Kilobits per second). MILTON rosettes can work individually, supporting the above capacities within their coverage areas, or they can be interconnected by optical fiber (light) to form a large metropolitan high speed data network. CRC is in the process of applying for a US patent covering this concept.

The second component of the system is the subscriber terminal. This unit is called an 'Internet Antenna'. The device mounts on the roof of the subscribers' buildings (wall or roof) and is oriented toward the rosette hub....perfect visibility of the hub is not necessary and clutter by trees and even partial obstructions by one or two adjacent buildings can be tolerated. CRC has conducted extensive propagation measurements using proposed MILTON frequencies, and is developing urban installation models which will ensure high availability of the system to users.

A personal computer is connected to the internet antenna via a standard, off-the-shelf Ethernet card. Software loaded into the PC and embedded within the Internet Antenna automatically sets up a high speed data link between the digital switch located at the hub and the PC. All protocols used in this operation are TCP/IP: ie, to the user the connectivity appears as an Internet connection.

For Wireless Local Loop applications requiring services such a telephone, an interface which provides dial tone on one side and a 10 Base T Ethernet TCP/IP port on the other is being developed. This device will allow Voice-over-Internet (VOIP) type telephone service. Because of the high speed and high QOS of the switching system present at the hub, latency and delay will not be a problem here as it is with conventional VOIP systems. Such telephony-only type services will not require the use of a personal computer to access the network.

Unlike conventional wireline Internet, this system will allow the rapid, almost real-time transfer of video files, digitized film, CD audio, digitized voice, and other high content electronic information that cannot be transferred because of "bandwidth bottlenecks". Individual users of the system can demand as little or as much bandwidth (~ 10 megabits/sec) as they need to support their requirements. One significant attribute of the system is its bi-directional capability. In theory, users will be able to download and upload data at megabit-per-second speeds. Information distribution centres that have files (such as digitized film and audio) will be able to use MILTON without the requirement for dedicated high bandwidth links to centralized data distribution points, which is typical of conventional wire-line high speed data systems. As a result, many new multimedia applications will be supported at low cost. A distributor of high content electronic data will only need a high capacity computer (a server) and a MILTON Internet Antenna connection to operate as a wireless multimedia resource centre.

Some means of billing for bandwidth used and collecting payments will have be devised for this system, especially since it will carry and distribute high value cultural content materials such a film and music, which are usually copyrighted. However, this issue is being considered with the Internet in general, and decisions and techniques formulated there will conceivably migrate to MILTON.

Some applications are:

1) Video-on-Demand file Server: A neighbourhood video store with a MILTON link could have a library of digitized films. These films would be stored as files on high capacity video server system computers. Users in the MILTON coverage area would access these files (just as a web site is accessed) and download them in real time for viewing. The video data is sent as high quality MPEG2 video streams which has significantly higher resolution than conventional VHS taped video. Unlike typical video tape distribution (rental) stores which only have thousands of the most popular video selections available; in MILTON the selection is limited only by the memory size of the aggregate digital video server population. This would allow the storage of more esoteric, less popular content that normally does not see commercial distribution (like National Film Board films, old CBC news clips, foreign language films, international television broadcasts, etc..).

2) Real-time Video Broadcast: Plays, theater, music performances, and other forms of live entertainment taking place at some locale within the MILTON coverage area could be broadcast through the MILTON system. Using real time digital video cameras (MPEG1) and sound encoding technology, such programs would be presented and addressed as Internet web-sites and accessed accordingly. Subscribers would view the programs on their computers or on home entertainment systems connected to computers. The advent of Digital Video Disk recording technology and low cost MPEG equipment and the use of MILTON as a distribution system, would allow the production and distribution costs of live entertainment to be significantly reduced.

3) CD Audio-on-Demand: As with video-on-demand, music could be stored on file server technology and called up remotely as a web site. Music would be downloaded to the subscriber computer and played on a home entertainment system. A typical MILTON channel would support about 60 simultaneous CD Audio-On-Demand sessions. Compressed audio files (such as the popular MP3 format) would be delivered at much faster rates. Musicians and other artists would not be faced with the large overhead costs typical of the current commercial music distribution industry. Using the inherent billing system based on credit card numbering of MILTON, revenue return to artists could almost be immediate and highly scaleable allowing extensive niche market penetration.

4) Interactive Distance Education: Course material could be presented to a distributed audience of pupils; real time interactivity would be facilitated by this system. Additionally, course notes could be stored as video files (containing problem solving examples, demonstrations of techniques, etc.) that would be electronically available through MILTON. Remote teacher-pupil interactivity on an individual basis would be supported. There are several rural pilot projects (Manitoba, Alberta) which already demonstrate the efficacy of such learning and teaching concepts. MILTON would allow the extension of these concepts to the urban core of cities.

5) High Speed Internet Access: Users to the system log onto downlink channels capable of data delivery speeds of up to 22.5 Megabits/Sec. Such channels are shared amongst users in a rosette petal. Users having large file transfers are automatically assigned dedicated channel slots which may be held for long periods of time. Uplink channels giving users return data rates in the order of 128 Kilobits/Sec to 6 Megabits/Sec are provided. The system automatically assigns bandwidth-on-demand. Competing Internet Service Providers (ISPs) can be accommodated on the same rosette and service providers do not have to have access to the hub to set up their service.

6) Rural Telephony: Using Dial Tone/TCP/IP interface devices this system will be able to route digitized telephony voice (from fixed telephones). A telephone switching network is created within a rosette and all telephones within the rosette can easily communicate with each other. To route calls outside the rosette, a TCP/IP to PBX bridge is used at the hub to connect the WLL telephones of the rosette to the world at large. This system has application in many rural parts of Canada not adequately serviced by conventional telephone because of distance, low user take up rates, or lack of wireline infrastructure.

7) Tele-medicine: The high data rate capability of MILTON allows high definition, information rich data files such as X-Rays; electrocardiograms; and electroencephalograms to be sent between doctor's offices and laboratories. These rates will also allow high quality (CD quality) sound to be transferred allowing cardiologists to listen to the heart sounds of distant patients. Such files and signals would normally require fiber optic cable to be installed on the doctors' premises, with MILTON, only Ethernet cabling would be require to a roof mounted antenna. Privacy is ensure by a number of TCP/IP based encryption standards which could be implemented; privacy is further enhanced by the containment of the RF signal to a highly localized locale.

## Conclusion

The MILTON project is an ambitious attempt to address the issues of bandwidth, capacity, and bidirectionality which underpin the development and evolution of the information highway. By using novel wireless network concepts and current technologies, researchers in the Broad Band Wireless Networks Group at CRC (VPTWS) are addressing these issues and outlining the technologies necessary to realize solutions. Work is currently being undertaken to study the information carrying capacity of the MILTON rosette system. Frequencies for the system are being chosen, and an investigation into the electromagnetic attributes of the system (antennas, signal transmission, etc) are being undertaken. CRC is working toward the development of a prototype system that would be installed in an urban neighbourhood for testing and evaluation. Collaborative links are also being formed with selected Canadian companies to help foster and exploit the technologies that are being developed within the project.

.

# **APPENDIX 2**

## BRIEF PROJECT DESCRIPTIONS AS DETAILED BY C-DOT

# LIST OF COLLABORATIVE PROJECTS

- MICROSTRIP PATACH ANTENNAS

- MMIC DEVELOPMENT

- SATCOM KA-BAND DIRECT RECEIVER AT 155 MBPS

- DSP VLSI / ASIC TECHNOLOGY

- BROADBAND APPLICATIONS CONNECTIVITY (BADLAB)

- BROADBAND WIRELESS LOCAL LOOP (BADLAB)

- OPTICAL TECHNOLOGIES

- PROPAGATION STUDIES

## **Project Proposal for Development of Patch Antennas**

Project Title : Low Gain L band ,S band and High Gain EHF band Microstrip Patch Antenna

## Background

:

The proposed EHF band point to point Digital Radio System for ATM connectivity will be a very compact suitcase terminal type of equipment suitable for outdoor deployment. Conventional high frequency radio systems had been using dish paraboloid kind of high gain antenna . These kind of antennas need separate mounting arrangement and they interface with the rest of the RF system using an external wave guide. With the emergence of Microstrip Patch Antennas and Patch Arrays , the trend is changing towards using more and more of these type of antennas . These antennas are relatively easy to manufacture and are quite low cost. These are two dimensional structures (flat ), considered to be the state of the art and they blend conveniently with the rest of the electronics of the system. They can even be mounted on the back of the front cover in a suitcase terminal type of equipment. CRC has very strong background in the field of antenna development , more specially the Microstrip Patch. Some of the best people of this field are working at CRC. It is proposed to develop a low gain L band and subsequently S band and EHF band Microstrip Patch Array Antenna in collaboration with CRC. The lower gain S band antenna will be used for VSAT. The L band antenna will be used in TDMA-PMP,CDMA-WLL wall mount unit and / or DECT-WLL wall mount unit . The high gain EHF band antenna will be used in the proposed EHF band Point to Point Digital Radio.

This project will give C-DOT engineers hands on experience on Antenna Technology and Measurements and will specially help them in gaining expertise in the design and development of Microstrip Patch Antennas which is an evolving technology. The project will also provide knowledge in the software tools and simulation techniques necessary for the development of Microstrip Patch Antennas. The C-DOT engineers will have the opportunity to

go through the full design cycle of it while designing different types of Microstrip Patches. The advantages and limitations of the technology will also be made clear.

## **Details of Project** :

The objective of the project is to design, fabricate, package and test a low gain L band antenna using two or three microstrip patches and a high gain EHF band antenna using microstrip patch arrays and suitable feed network. First a linearly polarized L band antenna will be developed which is relatively easier and as the experience is gained in the design process, a linearly polarized S band antenna will be taken up for design. After this the high gain pencil beam EHF band antenna with linear polarization will be developed. Near field and far field testing will be performed for all the antennas and radiation patterns will be plotted. The fabrication of the antennas will take place at CRC or locally available fabrication facility. Assembly and testing of these antennas will be done at CRC labs. At the end of the project two microstrip patch antennas will be delivered to C-DOT and the engineer from C-DOT would have gained enough expertise to take up new designs on his own to cater to the future needs of C-DOT . A suitable software simulation tool will also be identified which could be bought and installed at C-DOT so that the designs could be taken up locally.

| Manpower Resources | : | One engineer from C-DOT to work at CRC, preferably in spans of |

|--------------------|---|----------------------------------------------------------------|

| -                  |   | time with specific mission.                                    |

## **Equipment Resources**

From C-DOT Side : ENSEMBLE software tool for EM simulation of microwave structures, Testing instruments like VNA, Spectrum Analysers, Synthesized sweeper etc.

From CRC Side : ENSEMBLE, ARPS and IE3D software tool for EM simulation of microwave structures, Antenna prototype fabrication, including layout, mask, etching and assembly. Anechoic chambers for testing of antennas. Testing instruments like VNA, Spectrum Analysers, Synthesized sweeper etc.

## **Deliverable Outputs**

L band low gain antenna ,S band and EHF band high gain LP antenna. Expertise in Microstrip Patch Antenna design. Setting up antenna facility in CDOT. Expertise in near field and far field antenna measurement techniques, Reports, Technical Papers etc

## Work plan

## Start date 22/11/99

| SN   | Activity                                                                                                                                   | Responsibility     | Place of<br>Activity | M Ms<br>C-DOT | CRC |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------|---------------|-----|

| 部である | Low Gain L band Patch Antenna                                                                                                              | unsum line for the | 301 4701             | ha in Such    |     |

| A    | Reading manuals. Simulate patch on GML substrate to check for the bandwidth. Order material. Review design.                                | CRC & C-DOT        | C-DOT                | 0.25          |     |

| В    | If bandwidth can't be met, Design with air dielectric. Check<br>the parameters. Make single patch layout. Fabricate and test<br>the patch. | CRC & C-DOT        | CRC                  | 0.25          |     |

| С    | Learn ARPS. Layout with ideal feeds. Design feed and test.<br>Combine patch and feed. Review array design.                                 | CRC & C-DOT        | CRC                  | 0.25          |     |

| D    | Layout of array. Creating mask. Fabrication and testing of array                                                                           | CRC & C-DOT        | CRC                  | 0.25          |     |

| E    | Radome analysis. Learning ensemble 6. Making field model                                                                                   | CRC & C-DOT        | CRC                  | 0.25          |     |

| F    | Making measurements in anechoic chamber                                                                                                    | CRC & C-DOT        | CRC                  | 0.25          |     |

| G        | Make report. Get details of substrate selection, Radome | CRC & C-DOT | CRC | 0.25 |

|----------|---------------------------------------------------------|-------------|-----|------|

| 4月17日18月 | selection. Get the details of system requirements.      |             |     |      |

| H        |                                                         |             |     |      |

### Contact persons:

CRC Jeet Hothi: jeet.hothi@crc.ca Michel cuhachi : michel.cuhachi@crc.ca

## CDOT

Jayant Bhat nagar: jayant@cdotd.ernet.in N.K.Gupta : <u>nkg@cdotb.ernet.in</u> V.Srikrishnan : <u>sriki@cdotb.ernet.in</u>

After designing the L band antenna, the Sband antenna design will be taken up in CDOT with the soft ware tools available in CDOT. The low gain S band antenna design activity will extend over three to four months including fabrication and testing. The high gain EHF band antenna will take about four to six months for design, fabrication and testing. Radom effect analysis and rework could take another two to three months. Hence the total activity will extend over an year.

# **Project Proposal for Development of MMICs**

**Project Title** : Low Noise Amplifier & Direct Modulator MMICs

## Background

:

C-DOT has been working on transmission technologies and has developed good expertise in point to point digital radios, TDMA Point to Multipoint Radio System, Wireless Local Loop System and Satellite Communication systems. We have a strong RF team which has expertise in the design of various RF sub-systems like Amplifiers, LNAs, mixers, synthesizers etc. using hybrid MIC technology. These technologies are relevant at lower frequency bands like L, S, and C bands but start showing their limitations at higher frequencies like EHF band. CRC's key RF people are currently working in the 20-30 GHz range and have developed good expertise in design of MMICs and MHMICs at these frequencies. They also have a state of the art testing and wafer probing facility for MMICs. It is proposed to develop a low noise amplifier and a direct modulator MMICs in the EHF band in collaboration with CRC which will eventually be used in the Extra High Frequency Point to Point Digital Radio System.

# **Details of Project** :

The design and characterisation of a EHF band Low Noise Amplifier and a Direct Modulator/Demodulator for use in the receiver and transmitter sections of the proposed Digital Radio System will be accomplished. The first, a medium gain low noise amplifier design will use small signal analysis and linear simulation techniques. The second, a direct I-Q Modulator/Demodulator will use Linear simulations as well as non linear harmonic balance analysis. CRC has good understanding with some of the GaAs foundries and these MMICs will be fabricated at Phillips Foundry at Paris. Wafer probing and testing of these MMICs will be performed at CRC labs. At the end of the project C-DOT will have two EHF band MMICs which will be used in the proposed EHF band point to point digital radio system.

The LNA being designed is a three stage device. CRC is sending some of its MMIC designs to the foundry for MMIC fabrication by 20/12/99. As it is not possible to complete the whole LNA MMIC design in the remaining four weeks and CRC goes to the foundry only twice or thrice a year, it is proposed that a single stage LNA MMIC be designed and fabricated in this foundry run. This would not only give C-DOT a good exposure to the complete MMIC development cycle in a short period, but would also aid in verifying the behavioural models of the Coplanar Wave transmission lines which are proposed to be used in the LNA as well as the Direct Modulator Designs. The wafer is expected to be back at CRC after fabrication by last week of March.

| SN   | Activity                                                                                                                                                                                      | Responsibility | Place of<br>Activity | Duration<br>(Weeks)<br>C-DOT | Duration<br>(Weeks)<br>CRC |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------------|------------------------------|----------------------------|

| 权理局部 | Low Noise Amplifier MMIC (Start of Activity: 15/11/1999)                                                                                                                                      |                |                      | 1                            |                            |

| A    | Defining the specifications                                                                                                                                                                   | C-DOT          | C-DOT                | completed                    | completed                  |

| В    | Investigate Properties of PHEMT & Foundry Process                                                                                                                                             | CRC & C-DOT    | CRC                  | 1                            |                            |

| C    | Stabilize the PHEMT and Perform Noise Figure and Gain Trade-off<br>of First Stage of the 3 Stage LNA                                                                                          | CRC & C-DOT    | CRC                  | 1                            |                            |

| D    | Developing Ideal Matching Circuits for the first stage                                                                                                                                        | CRC & C-DOT    | CRC                  | 1                            |                            |

| Е    | Changing ideal elements to MMIC elements of first stage                                                                                                                                       | CRC & C-DOT    | CRC                  | 1                            |                            |

| F    | Layout and Preliminary ElectroMagnetic(EM) analysis of first stage<br>– Ready for MMIC fabrication                                                                                            | CRC & C-DOT    | CRC                  | 1                            |                            |

| G    | Developing ideal Matching circuits for second and third stages                                                                                                                                | CRC & C-DOT    | CRC & C-DOT          | 1-CRC<br>2-C DOT             |                            |

| H    | Layout and detailed EM analysis of the complete 3 stage LNA                                                                                                                                   | CRC & C-DOT    | CRC & C-DOT          | 1 – CRC<br>3– CDOT           |                            |

| I    | Testing of the single stage MMIC in the 2 <sup>nd</sup> Week of April                                                                                                                         | CRC & C-DOT    | CRC                  | 1.5                          |                            |

| . J  | Changes (if required) to be made on the 3 stage LNA design based<br>on the single stage LNA test results. Integration with CRC foundry<br>process. MMIC design ready for the May foundry run. |                | CRC                  | 1 to 3                       |                            |

| J    | Testing of the 3 stage LNA in the month of August(tentative)                                                                                                                                  | CRC & C-DOT    | CRC                  | 1.5                          |                            |

| SN | Activity                                                                                                                                                                           | Responsibility | Place of<br>Activity                 | Duration<br>(Weeks)<br>C-DOT | Duration<br>(Weeks)<br>CRC |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------------------|------------------------------|----------------------------|

|    | Direct Modulator MMIC                                                                                                                                                              |                | ALC: NO                              |                              | The C                      |

| A  | Defining the specifications                                                                                                                                                        | C-DOT          | C-DOT                                |                              |                            |