# Communications Research Centre

# IMPLEMENTATION OF HIGH SPEED FFTs FOR RADAR SIGNAL PROCESSING

by

H.C. Chan

#### CAUTION

The use of this information is permitted subject to recognition of proprietary and patent rights.

> CRC REPORT NO. 1394 OTTAWA, AUGUST 1985

TK 5102.5 Government of Canada Department of Communications C673e

IC

#1394

Gouvernement du Canada Ministère des Communications

#### COMMUNICATIONS RESEARCH CENTRE

## DEPARTMENT OF COMMUNICATIONS CANADA

Industry Canada Library - Queen

AOUT 2 9 2012

Industrie Canada Bibliothèque - Queen

#### IMLEMENTATION OF HIGH SPEED FFTs FOR RADAR SIGNAL PROCESSING

by

H.C. Chan

(Radar and Communications Technology Branch)

**CRC REPORT NO. 1394**

August 1985 OTTAWA

This work was sponsored by the Department of National Defence, Research and Development Branch under Sub Program 33C.

#### CAUTION

The use of this information is permitted subject to recognition of proprietary and patent rights.

1K2.5 51021324 #1394

PAGE

#### TABLE OF CONTENTS

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |                                                                                                                          |                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | LIST | OF FIGURES                                                                                                               | iii                                                   |

| 1.1 A survey of existing hardware FFT processors 2  2. THE FFT ALGORITHM 3  2.1 Two-dimensional representation of the DFT of a one-dimensional sequence 3  2.2 Generalized FFT procedures 7  2.2.1 Twiddle factor 8  2.2.2 Butterfly 10  2.2.3 Radix 12  2.3 Alternative decimation processes 12  2.3.1 Decimation-in-frequency 12  2.3.2 Decimation-in-time 13  2.3.3 Digit reversal 14  3. REDUCING THE COMPUTATIONAL REQUIREMENTS FOR DFT ALGORITHM AND ITS PROCESSING COMPONENTS 15  3.1 Reduction of computational effort 15  3.2 Radix-r butterfly and radix-r FFT 16  3.2.1 Radix-2 butterfly and 4-point DFT 18  3.2.2 Radix-4 butterfly and 4-point DFT 20  3.3 Pipelining of the butterfly for maximum throughput 23  4. HARDWARE IMPLEMENTATION OF THE FFT ALGORITHM 27  4.1 Parallel-pipeline FFT 29  4.1.1 Radix-2 parallel-pipeline 16-point FFT 29  4.1.2 Radix-4 parallel-pipeline 16-point FFT 30  4.2 Single-pipeline FFT 30  4.2.1 Radix-2 single-pipeline 16-point FFT 30  4.2.2 Radix-4 single-pipeline 16-point FFT 30  4.2.3 Radix-r single pipeline FFT 40  4.3 Radix-r single pipeline FFT 40  5. DESIGN FOR A DOPPLER PROCESSOR DISCRIMINATOR AND A 2-DIMENSIONAL DIGITAL BEAMFORMER BASED ON A HIGH SPEED 16-POINT FFT IMPLEMENTATION 51  5.1 Doppler processing and digital beamforming 51  5.1 DOPPLER PROCESSOR DISCRIMINATOR AND A 2-DIMENSIONAL DIGITAL BEAMFORMER BASED ON A HIGH SPEED 16-POINT FFT IMPLEMENTATION 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |                                                                                                                          |                                                       |

| 2. THE FFT ALGORITHM 3  2.1 Two-dimensional representation of the DFT of a one-dimensional sequence 3 2.2 Generalized FFT procedures 7 2.2.1 Twiddle factor 8 2.2.2 Butterfly 10 2.2.3 Radix 12 2.3 Alternative decimation processes 12 2.3.1 Decimation-in-frequency 12 2.3.2 Decimation-in-frequency 12 2.3.3 Digit reversal 14  3. REDUCING THE COMPUTATIONAL REQUIREMENTS FOR DFT ALGORITHM AND ITS PROCESSING COMPONENTS 15  3.1 Reduction of computational effort 15 3.2 Radix-r butterfly and radix-r FFT 16 3.2.1 Radix-2 butterfly and 2-point DFT 18 3.2.2 Radix-4 butterfly and 4-point DFT 18 3.2.2 Radix-4 butterfly and 4-point DFT 20 3.3 Pipelining of the butterfly for maximum throughput 23  4. HARDWARE IMPLEMENTATION OF THE FFT ALGORITHM 27  4.1 Parallel-pipeline FFT 29 4.1.1 Radix-2 parallel-pipeline 16-point FFT 29 4.1.2 Radix-4 parallel-pipeline 16-point FFT 30 4.2.2 Radix-4 single-pipeline 16-point FFT 30 4.2.1 Radix-2 single-pipeline 16-point FFT 30 4.2.2 Radix-4 single-pipeline 16-point FFT 30 4.2.1 Radix-2 single-pipeline 16-point FFT 30 4.2.2 Radix-4 single-pipeline 16-point FFT 30 4.2.1 Radix-2 single-pipeline 16-point FFT 30 4.2.2 Radix-4 single-pipeline 16-point FFT 30 4.2.1 Radix-2 single-pipeline 16-point FFT 30 4.2.2 Radix-4 single-pipeline 16-point FFT 30 4.2.3 Radix-r single pipeline FFT 30 4.2.4 Radix-r single pipeline FFT 30 4.2.1 Radix-r single pipeline FFT 30 4.2.1 Radix-r single pipeline FFT 30 4.2.2 Radix-4 single-pipeline 16-point FFT 30 4.3 Radix-r single pipeline FFT 30 4.3 Radix-r s | 1. 1 | NTRODUCTION                                                                                                              | 1                                                     |

| 2.1 Two-dimensional representation of the DFT of a one- dimensional sequence 3  2.2 Generalized FFT procedures 7  2.2.1 Twiddle factor 8  2.2.2 Butterfly 10  2.2.3 Radix 12  2.3 Alternative decimation processes 12  2.3.1 Decimation-in-frequency 12  2.3.2 Decimation-in-time 13  2.3.2 Decimation-in-time 13  2.3.3 Digit reversal 14  3. REDUCING THE COMPUTATIONAL REQUIREMENTS FOR DFT ALGORITHM AND ITS PROCESSING COMPONENTS 15  3.1 Reduction of computational effort 15  3.2 Radix-r butterfly and radix-r FFT 16  3.2.1 Radix-2 butterfly and 2-point DFT 18  3.2.2 Radix-4 butterfly and 4-point DFT 20  3.3 Pipelining of the butterfly for maximum throughput 23  4. HARDWARE IMPLEMENTATION OF THE FFT ALGORITHM 27  4.1 Parallel-pipeline FFT 29  4.1.1 Radix-2 parallel-pipeline 16-point FFT 29  4.1.2 Radix-4 bartallel-pipeline 16-point FFT 30  4.2 Single-pipeline FFT 30  4.2.1 Radix-2 single-pipeline 16-point FFT 30  4.2.2 Radix-4 single-pipeline 16-point FFT 32  4.2.2 Radix-4 single-pipeline 16-point FFT 30  4.2.1 Radix-2 single-pipeline 16-point FFT 30  4.2.2 Radix-4 single-pipeline 16-point FFT 30  4.2.1 Radix-2 single-pipeline 16-point FFT 30  4.2.2 Radix-4 single-pipeline 16-point FFT 30  4.2.1 Radix-2 single-pipeline 16-point FFT 30  4.2.2 Radix-4 single-pipeline 16-point FFT 30  4.2.3 Radix-r single pipeline FFT 49  5. DESIGN FOR A DOPPLER PROCESSOR DISCRIMINATOR AND A 2-DIMENSIONAL DIGITAL BEAMFORMER BASED ON A HIGH SPEED 16-POINT FFT IMPLEMENTATION 51  5.1 Doppler processing and digital beamforming 51  5.1 Doppler processing and digital beamforming 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1    | .1 A survey of existing hardware FFT proc                                                                                | essors 2                                              |

| dimensional sequence 3  2.2 Generalized FTT procedures 7  2.2.1 Twiddle factor 8  2.2.2 Butterfly 10  2.2.3 Radix 12  2.3 Alternative decimation processes 12  2.3.1 Decimation-in-frequency 12  2.3.2 Decimation-in-time 13  2.3.3 Digit reversal 14  3. REDUCING THE COMPUTATIONAL REQUIREMENTS FOR DFT ALGORITHM AND ITS PROCESSING COMPONENTS 15  3.1 Reduction of computational effort 15  3.2 Radix-r butterfly and radix-r FFT 16  3.2.1 Radix-2 butterfly and 2-point DFT 18  3.2.2 Radix-4 butterfly and 2-point DFT 18  3.2.2 Radix-4 butterfly and 4-point DFT 20  3.3 Pipelining of the butterfly for maximum throughput 23  4. HARDWARE IMPLEMENTATION OF THE FFT ALGORITHM 27  4.1 Parallel-pipeline FFT 29  4.1.1 Radix-2 parallel-pipeline 16-point FFT 29  4.1.2 Radix-4 variallel-pipeline 16-point FFT 30  4.2 Single-pipeline FFT 30  4.2.1 Radix-2 single-pipeline 16-point FFT 30  4.2.2 Radix-4 single-pipeline 16-point FFT 30  4.2.1 Radix-7 single pipeline FFT 30  4.2.2 Radix-4 single-pipeline 16-point FFT 30  4.2.2 Radix-4 single-pipeline 16-point FFT 30  5. DESIGN FOR A DOPPLER PROCESSOR DISCRIMINATOR AND A 2-DIMENSIONAL DIGITAL BEAMFORMER BASED ON A HIGH SPEED 16-POINT FFT IMPLEMENTATION 51  5.1 Doppler processing and digital beamforming 51  5.1 Doppler processing and digital beamforming 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2. I | HE FFT ALGORITHM                                                                                                         | 3                                                     |

| 3.1 Reduction of computational effort                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2    | dimensional sequence                                                                                                     | 3 7 7 8                                               |

| 3.2 Radix-r butterfly and radix-r FFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |                                                                                                                          |                                                       |

| 4.1 Parallel-pipeline FFT 4.1.1 Radix-2 parallel-pipeline 16-point FFT 29 4.1.2 Radix-4 parallel-pipeline 16-point FFT 30 4.2 Single-pipeline FFTs 30 4.2.1 Radix-2 single-pipeline 16-point FFT 32 4.2.2 Radix-4 single-pipeline 16-point FFT 40 4.3 Radix-r single pipeline FFT 49 5. DESIGN FOR A DOPPLER PROCESSOR DISCRIMINATOR AND A 2-DIMENSIONAL DIGITAL BEAMFORMER BASED ON A HIGH SPEED 16-POINT FFT IMPLEMENTATION 5.1 Doppler processing and digital beamforming 51 COMMUNICATIONS CANADA C R C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3    | .2 Radix-r butterfly and radix-r FFT<br>3.2.1 Radix-2 butterfly and 2-point DF<br>3.2.2 Radix-4 butterfly and 4-point DF | T 18 T 20                                             |

| 4.1.1 Radix-2 parallel-pipeline 16-point FFT 4.1.2 Radix-4 parallel-pipeline 16-point FFT 30 4.2 Single-pipeline FFTs 30 4.2.1 Radix-2 single-pipeline 16-point FFT 32 4.2.2 Radix-4 single-pipeline 16-point FFT 40 4.3 Radix-r single pipeline FFT 49 5. DESIGN FOR A DOPPLER PROCESSOR DISCRIMINATOR AND A 2-DIMENSIONAL DIGITAL BEAMFORMER BASED ON A HIGH SPEED 16-POINT FFT IMPLEMENTATION 5.1 Doppler processing and digital beamforming 5.1 COMMUNICATIONS CANADA C R C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4. H | ARDWARE IMPLEMENTATION OF THE FFT ALGORIT                                                                                | нм 27                                                 |

| 5.1 Doppler processing and digital beamforming  COMMUNICATIONS CANAGA  CRC  (NOV 13 1986                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4    | 4.1.1 Radix-2 parallel-pipeline 16-poi<br>4.1.2 Radix-4 parallel-pipeline 16-poi<br>2 Single-pipeline FFTs               | nt FFT                                                |

| COMMUNICATIONS CANABA<br>CRC<br>.(NOV 13 1986                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |                                                                                                                          |                                                       |

| a finalities and a second of the second of t | 5    | .l Doppler processing and digital beamfor                                                                                | COMMUNICATIONS CANADA<br>CRC<br>.( <b>NOV</b> 13 1986 |

|    | 5.2 Implementation of a 2-Dimensional digital beamformer and a Targe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | et |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|    | Doppler processor 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 51 |

|    | 5.2.1 A modified 2-dimensional digital beamformer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 51 |

|    | a. modified parallel-pipeline 16-point FFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 51 |

|    | b. An 8x16 row-column transposition network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 53 |

|    | 5.2.2 Target Doppler Processor employing the modified                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|    | parallel-pipeline 16-point FFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 54 |

|    | • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

| 6. | HIGH SPEED FFT PROCESSORS FOR OTHER RADAR APPLICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 68 |

|    | 6.1 Digital pulse compression and radar image processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 68 |

|    | 6.2 Component count reduction versus throughput reduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|    | 6.3 Parallel-pipeline FFTs of larger dimension                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|    | ors relative processes in the second of the |    |

| 7. | ACKNOWLEDGEMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 77 |

| Q  | PEFFRENCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 78 |

PAGE

#### LIST OF FIGURES

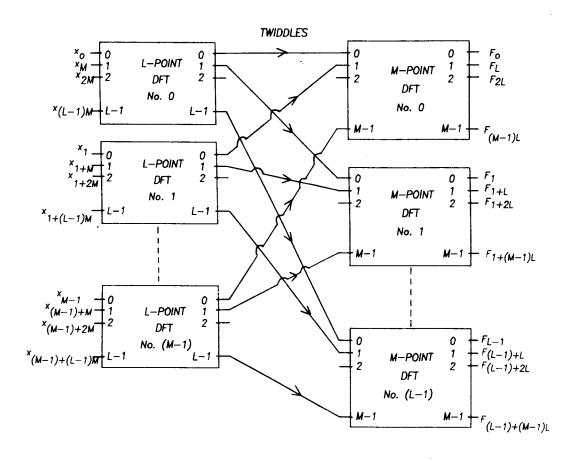

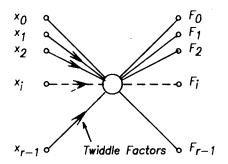

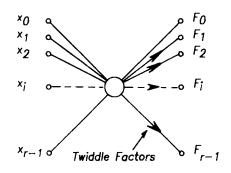

| Figure | 1   | Signal flow diagram of the generalized FFT procedures                         | 1   |

|--------|-----|-------------------------------------------------------------------------------|-----|

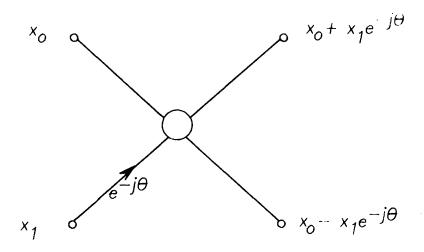

| Figure | 2   | Symbolic diagram of a radix-2 butterfly and schematic                         |     |

|        |     | diagram of a 2-point DFT                                                      | 19  |

| Figure | 3   | Symbolic diagram of a radix-4 butterfly                                       | 2   |

| Figure | 4   | Schematic diagram of a 4-point DFT                                            |     |

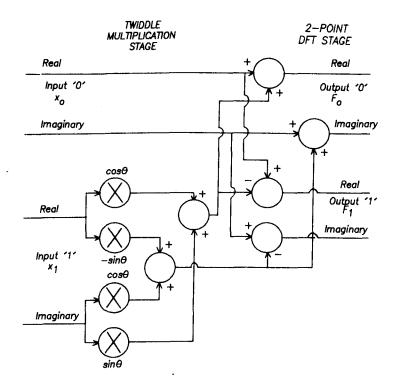

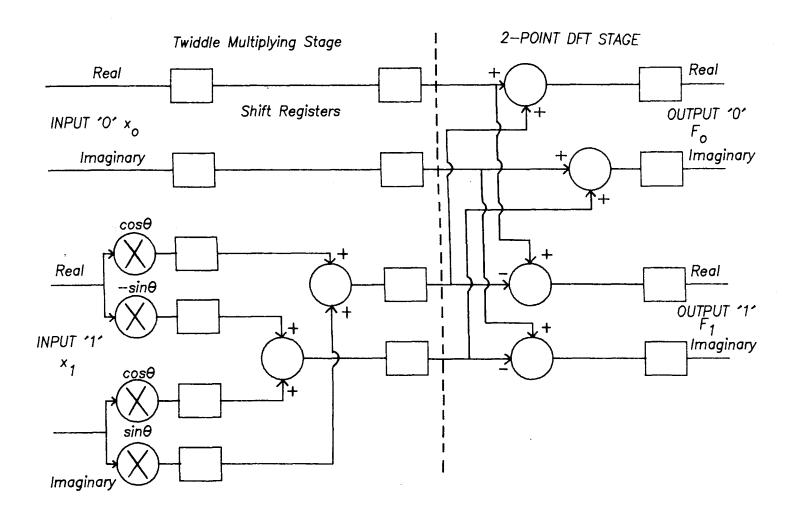

| Figure | 5   | Schematic diagram of a pipelined radix-2 butterfly                            |     |

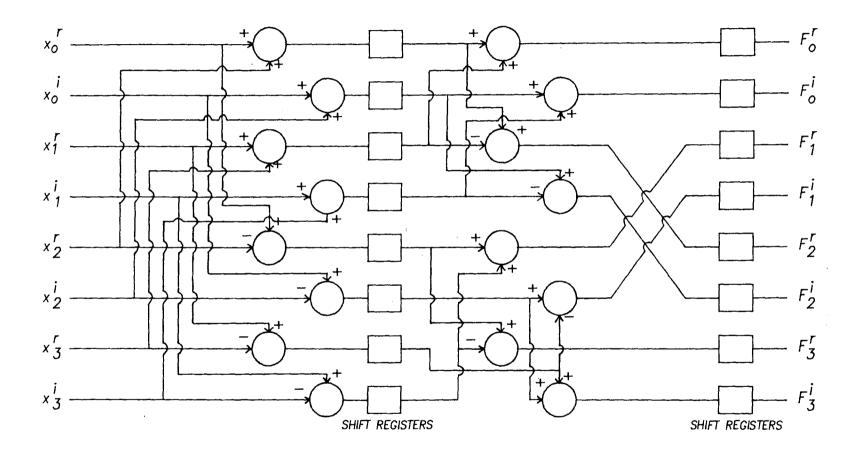

| Figure | 6   | Schematic diagram of a pipelined 4-point DFT                                  | 20  |

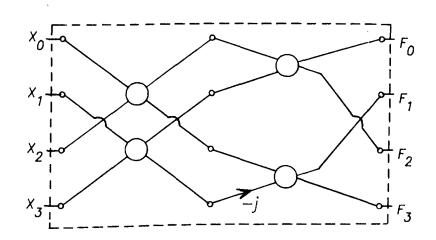

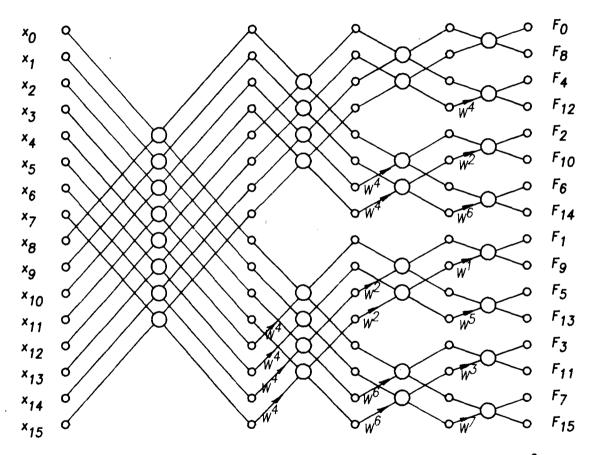

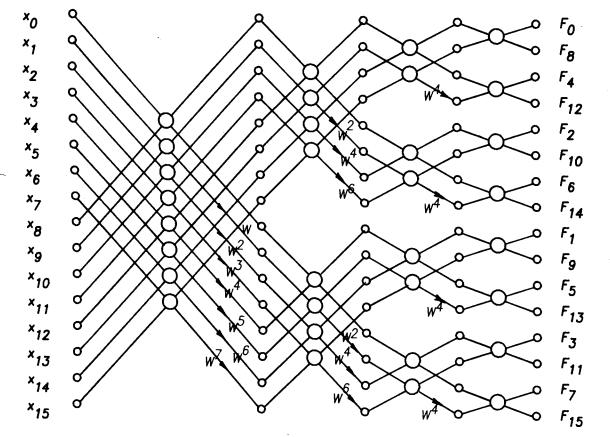

| Figure | 7   | Signal flow diagram of the radix-2 DIT 16-point FFT                           |     |

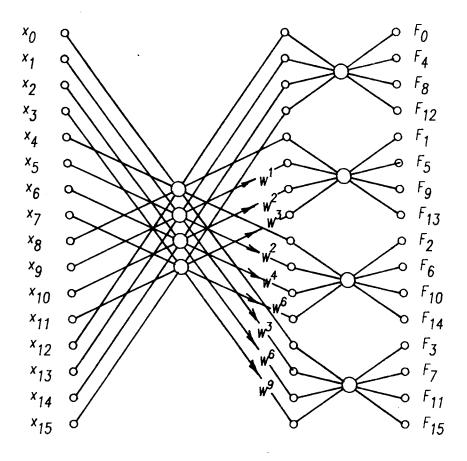

| Figure | 8   | Signal flow diagram of the radix-4 16-point FFT                               |     |

| Figure | 9   | Signal flow diagram of the radix-2 DIF 16-point FFT                           |     |

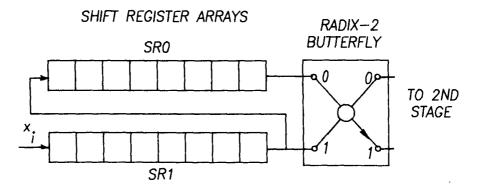

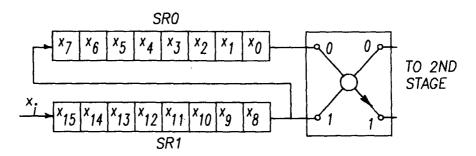

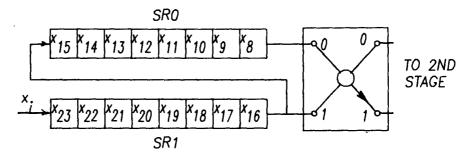

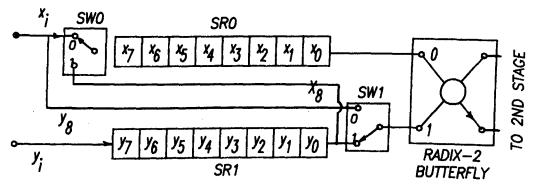

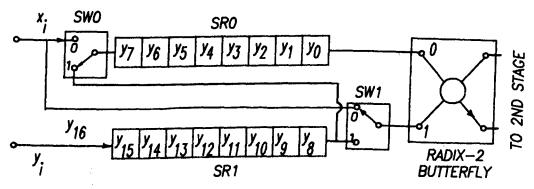

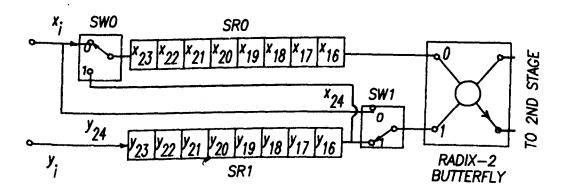

| Figure | 10  | Data buffering scheme for a radix-2 butterfly                                 |     |

| Figure | 11  | Schematic diagram of a radix-2 commutator                                     | 35  |

| Figure | 12  | Summary of steps of the generalized FFT procedures as                         |     |

|        |     | applied to the radix-2 DIF 16-point case                                      |     |

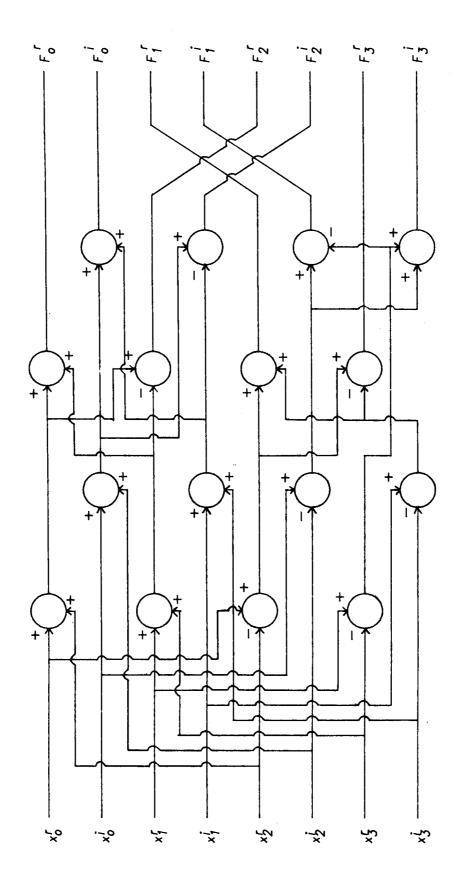

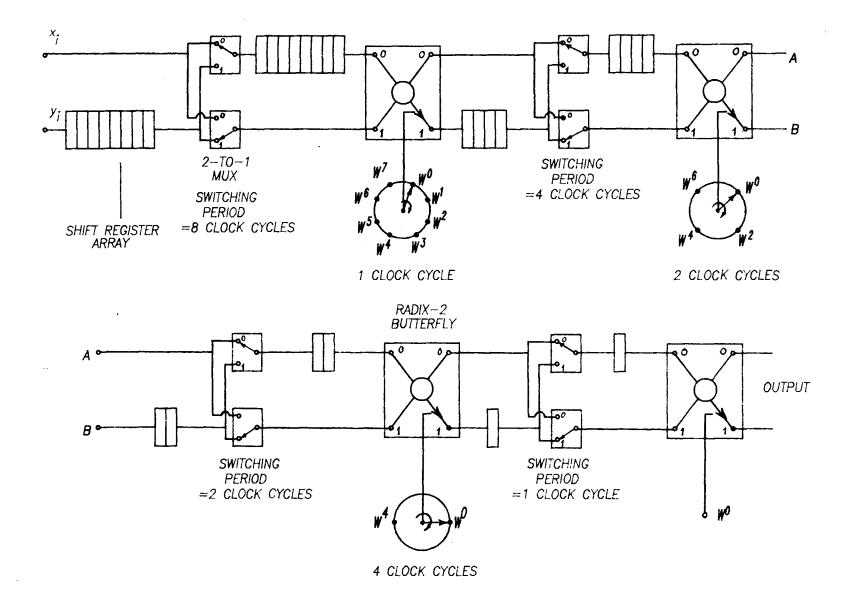

| Figure |     | Schematic diagram of a radix-2 DIF single-pipeline FFT                        |     |

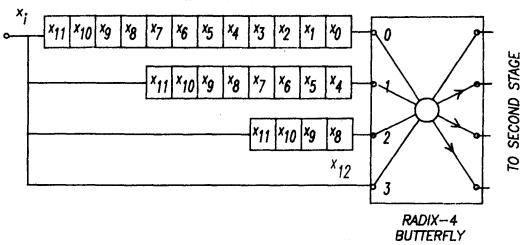

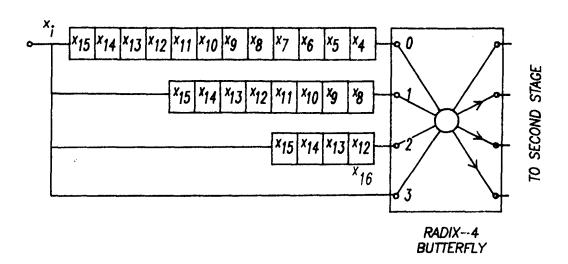

| Figure |     | Data buffering scheme for a radix-4 butterfly                                 |     |

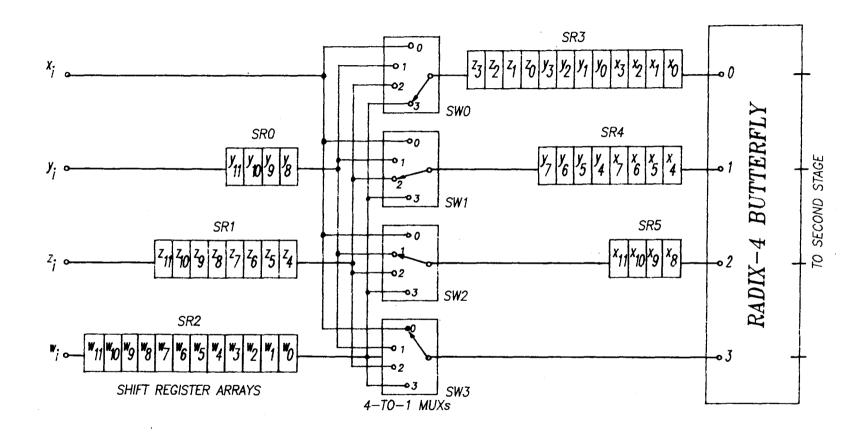

| Figure |     | Schematic diagram of a radix-4 commutator                                     | 42  |

| Figure | 16  | Illustration of the input-output data arrangement for a                       |     |

|        |     | radix-4 commutator                                                            | 45  |

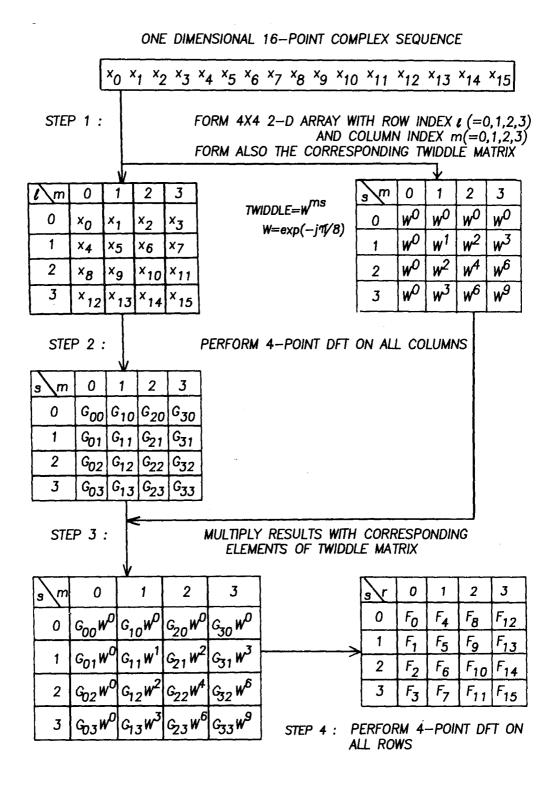

| Figure | 17  | Summary of steps of the generalized FFT procedures as                         |     |

|        |     | applied to the radix-4 16-point case                                          | 46  |

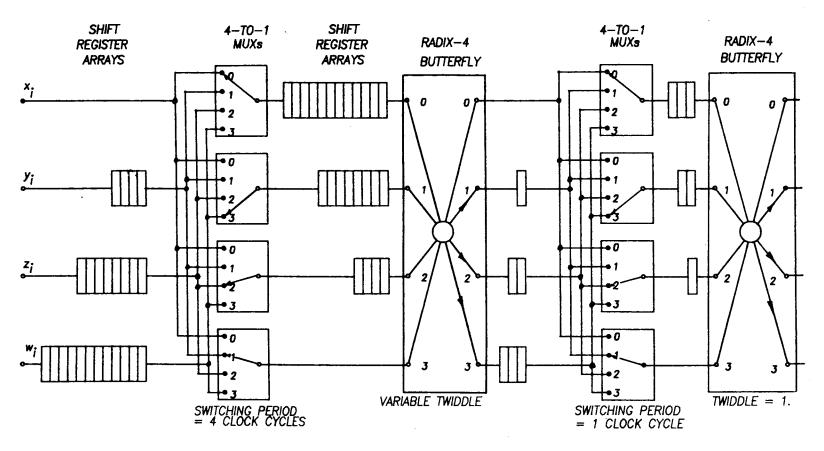

| Figure | 18  | Schematic diagram of a radix-4 single-pipeline 16-point                       |     |

|        |     | FFT                                                                           |     |

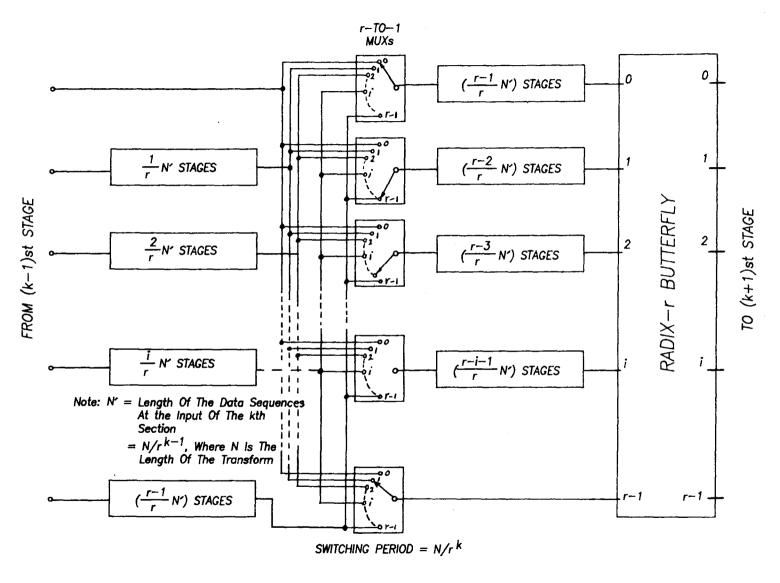

| Figure |     | Schematic diagram of a radix-r single-pipeline FFT                            |     |

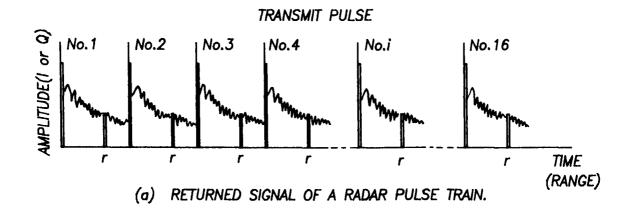

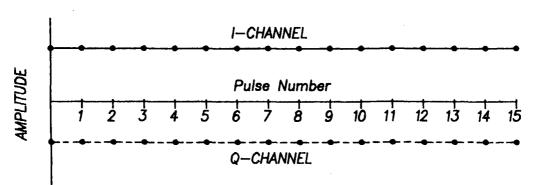

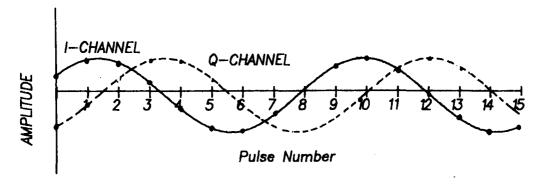

| Figure |     | Digital representation of radar signals                                       | 52  |

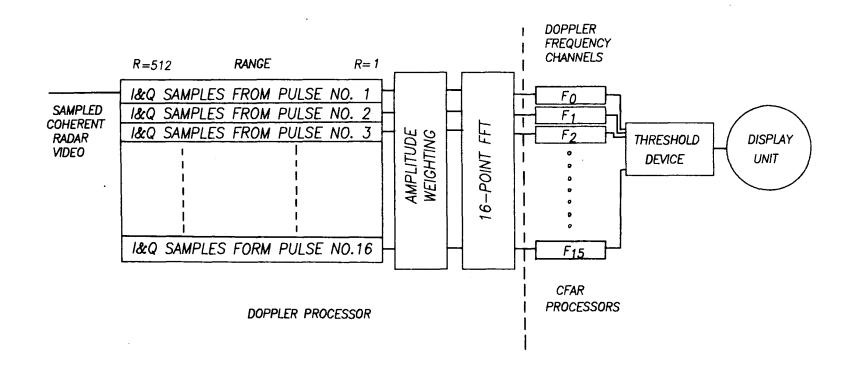

| Figure | 21  | Block diagram of a radar signal processing system                             |     |

|        |     | employing a target Doppler discriminator                                      | 55  |

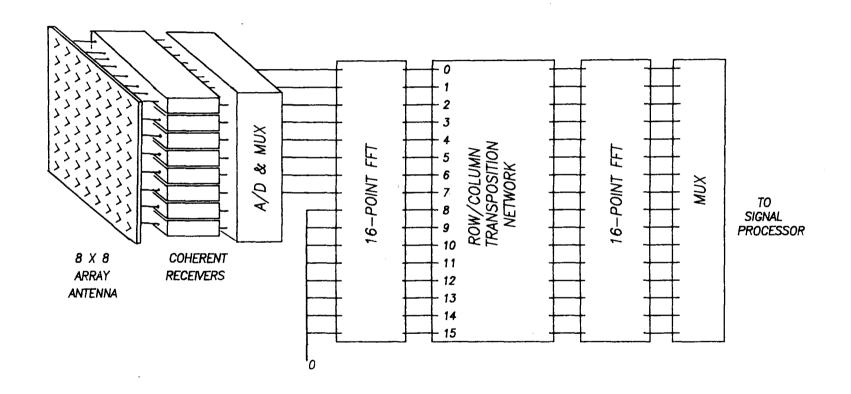

| Figure |     | System block diagram of an 8x8 SAMPAR system                                  | 58  |

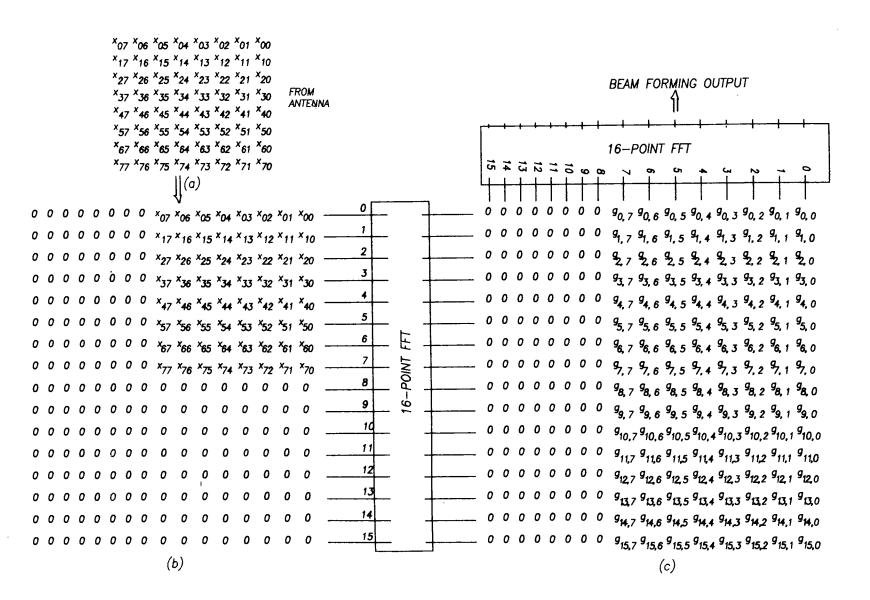

| Figure |     | Data permutation in a 2-dimensional beamformer                                | 59  |

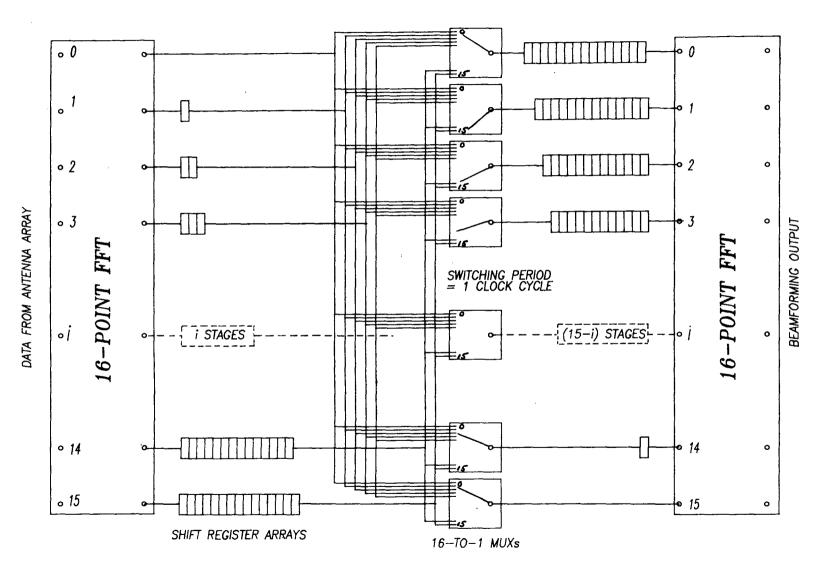

| Figure | 24  | Schematic diagram of a 16x16 2-Dimensional digital                            |     |

|        | 0.5 | beamformer                                                                    | Öυ  |

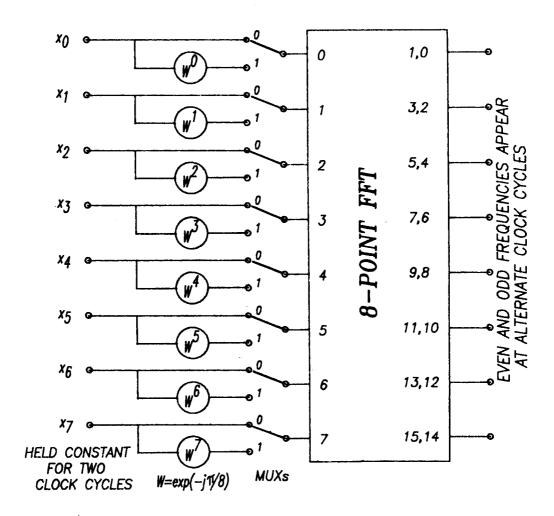

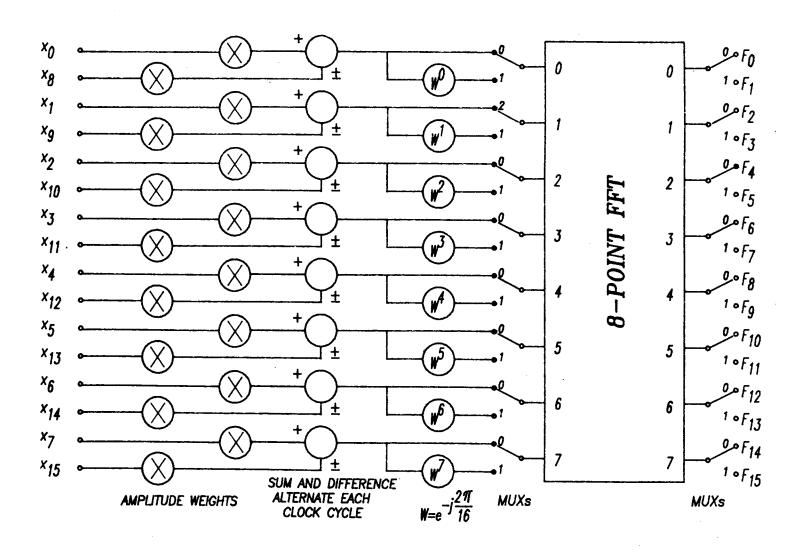

| Figure | 25  | Schematic diagram of a modified parallel-pipeline                             | د ۲ |

|        | 0.0 | 16-point FFT processor                                                        | 02  |

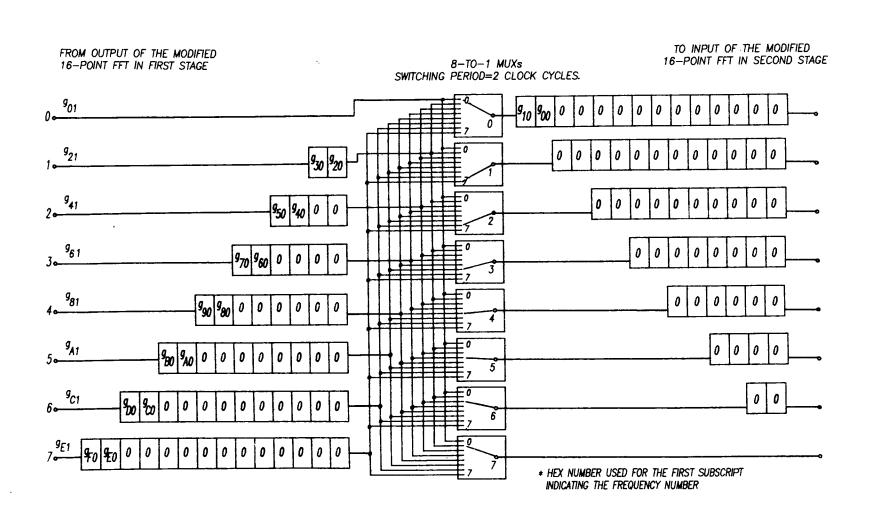

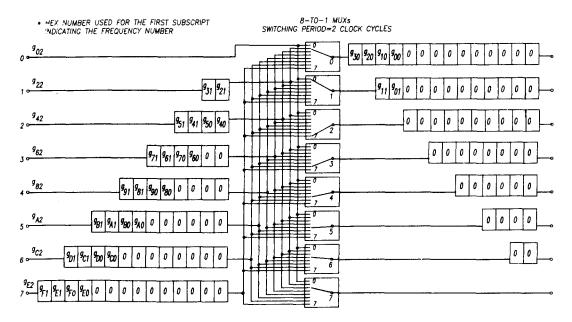

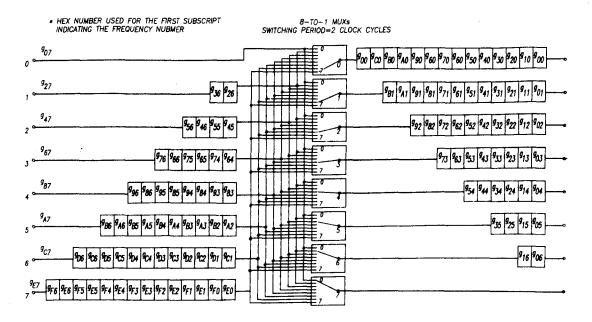

| Figure | 26  | Schematic diagram of a 8x16 row-column transposition                          | 65  |

| Md     | 27  |                                                                               | U.  |

| Figure | 21  | Required data arrangement for the 8x16 row-column transposition network       | 66  |

| Figure | 20  | Operation of the 8x16 row-column transposition network                        | v   |

| rgure  | 20  | at various clock cycles                                                       | 67  |

| Figure | 20  | Schematic diagram of a Target Doppler discriminator                           | 07  |

| rRate  | 47  | employing a modified parallel-pipeline 16-point FFT                           | 60  |

| Figure | 30  | Prototype of the Doppler Processor                                            |     |

| Figure |     | Prototype of the 2-D digital Beamformer                                       |     |

| Perre  | J.  | TIOCOCYPE OF CHE P. OFFORER DEGILIOTHER #111111111111111111111111111111111111 | , , |

#### LIST OF TABLES

| Table    | I.     | Two-dimensional representation of the DFT of a                              |     |

|----------|--------|-----------------------------------------------------------------------------|-----|

|          |        | one-dimensional sequence                                                    | 7   |

| Table    | II.    | Two-dimensional representation of a one-                                    |     |

|          |        | dimensional sequence                                                        | 8   |

| Table    | III.   | Two-dimensional representation of the twiddle                               |     |

|          |        | factor                                                                      | 9   |

| Table    | IV.    | Result of column-DFTs and twiddle multiplication                            | 9   |

| Table    | V.     | Steps of the generalized FFT procedures                                     | 10  |

| Table    | VI.    | Data arrangement of a time sequence using the                               |     |

|          |        | decimation-in-frequency procedure                                           | 12  |

| Table    | VII.   | Data arrangement of the DFT of a time sequence                              |     |

|          |        | using the decimation-in-frequency procedure                                 | 13  |

| Table    | VIII.  | Data arrangement of a time sequence using the                               |     |

|          |        | decimation-in-time procedure                                                | 13  |

| Table    | IX.    | Required number of complex multiplications for                              |     |

|          |        | an N-point radix-2 and radix-4 FFTs                                         | 23  |

| Table    | Х.     | Component counts of pipelined 2-point and 4-                                |     |

|          |        | point DFTs and twiddle multiplier                                           | 27  |

| Table    | XI.    | Component count for a radix-2 parallel-pipeline                             |     |

|          |        | 16-point FFT                                                                | 30  |

| Table    | XII.   | Component count for a radix-4 parallel-pipeline                             |     |

|          |        | 16-point FFT                                                                | 30  |

| Table    | XIII.  | Component count for a radix-2 single-pipeline                               |     |

|          |        | 16-point FFT                                                                | 40  |

| Table    | XIV.   | Switch connections as a function of clock cycles                            |     |

|          | ••••   | for the MUXs in a radix-4 commutator                                        | 43  |

| Table    | XV.    | Component count for a radix-4 single-pipeline                               | , , |

| m        | 3277   | 16-point FFT                                                                | 48  |

| Table    | XVI.   | Comparison of component counts for various                                  | 48  |

| m -1 1 - | VIII T | 16-point pipeline FFT structures                                            | 48  |

| Table    | YATT.  | Comparison of component counts for various 64-point pipeline FFT structures | 49  |

| Table    | VVITTT | Component count of a modified parallel-pipeline                             | 47  |

| rabre    | VATIT. | 16-point FFT                                                                | 63  |

| Table    | XIX    | Switch connections of the MUXs in the 8x16                                  | UJ  |

| тарте    | VIV    | row-column transposition network through 20 clock                           |     |

|          |        | cycles                                                                      | 64  |

| Table    | YY     | Comparison of IC chip counts between two                                    | U-7 |

| TANTE    | AA.    | implementations of the 2-D digital beamformer                               | 74  |

## IMPLEMENTATION OF HIGH SPEED FFTs FOR RADAR SIGNAL PROCESSING

bу

H.C. Chan

#### ABSTRACT

Discrete Fourier Transform (DFT) has found wide application in radar and sonar systems. With an increased emphasis on digital signal processing, radar systems have requirements for DFTs with ever increasing data rates. The Fast Fourier Transform (FFT) algorithm permits efficient computation of the DFT. In this work, both the fundamentals of FFT algorithms and their implementation are discussed, with emphasis on hardware design. Designs are presented for two radar signal processors employing high speed FFTs, i.e., (1) a high speed Doppler processor and (2) a two-dimensional digital beam-former.

#### 1. INTRODUCTION

The discrete Fourier Transform (DFT) has found wide application in radar and sonar systems. In the case of radar, there is a requirement for DFT processors capable of very high data rates. Some examples of typical radar applications are the following: target Doppler processing, pulse Doppler processing, pulse compression, matched filtering, radar imagery processing and, recently, digital beam-forming. The processing speed requirements range from several MHz in the case of a Doppler processor to over a GHz for a digital beam-former. In this report, some aspects of the hardware implementation of the Fast Fourier Transform (FFT) are considered. It is intended in this report to provide some insight into the problem of developing:

- (a) techniques for implementing the FFT algorithm in a form suitable for radar signal processing,

- (b) techniques for increasing processing speed and efficiency,

- (c) techniques for reducing the hardware component count,

- (d) techniques for achieving greater parallelism so that higher throughput rate can be realized.

#### 1.1 A survey of existing hardware FFT processors

It is instructive to survey the literature and determine if any "off-the-shelf" hardware FFT processors are able to fulfill the requirements outlined in the previous section. In a paper published in 1969, Bergland [1] tabulated the characteristics of over twenty hardware FFT processors which existed at that time. The comparison is based on processor architecture, function and performance characteristics, system hardware features and cost. Most of these processors were produced by research laboratories, such as Bell Laboratory, Stanford Research Institute, MIT Lincoln Laboratory, for specific applications. A few were produced by computer manufacturers such as IBM, Control Data Corp. Processing speeds for these processors were measured in terms of the time required to compute a 1024-point complex FFT. The speeds range from a high of 1 ms for the MM DSP of Emerson Electric to a low of 600 ms for the CSS-3 of Computer Signal Processors, Inc. Typically, the execution time for a 1024-point complex FFT is in the tens of milli-These times compare very favorably with those achieved by present-day commercial data processors.

Over a decade has past since the publication of this survey paper. Many special purpose high-speed FFT processors undoubtedly have been built by various research laboratories and in the industry. However, their technical characteristics are not generally available. More importantly, there appears to be no commercially available processors which are directly applicable to real-time radar signal processing functions. Commercially available FFT processors usually take the form of an array processor. Array processors lean towards high flexibility and tend to be software orientated. Examples of these processors include the Floating Point System (FPS) family of array processors, Star-100 array processor developed by Star Technologies Inc., and the TASP array processor developed by ESE. The throughput rates of these systems, measured in terms of millions of floating point operations (Mega-flops), are very impressive, ranging from 25 Mega-flops for an AP-120B to over 100 Mega-flops for the TASP. With respect to FFT processing, the execution time for a 1024-point complex FFT ranges from 5 msec for a FPS AP120B to about 800 micro-seconds for the TASP. However, the operation of array processors is input/output (I/0)-limited. For applications such as a 2-D digital beamformer, where the data are available simultaneously, their throughput rate is limited by the data transfer rate of the I/O interface.

Families of IC chips specially designed for FFT processing are available from a few device manufacturers. Examples of these IC chips are the AM29500 family by Advanced Micro Devices, and the Weitek family signal processing ICs. Recently, IBM and Sony of Japan each introduced a family of monolithic devices suitable for the implementation of systolic array processors[2]. These devices may be used to form the building blocks of a high speed FFT processor for real-time radar applications. However, the cost of these devices is currently very high. Consequently, it is more economical to develop high speed digital radar signal processors with inexpensive and commercially available ICs.

It is well known that there tends to be a tradeoff between processing speed and processing flexibility in the design of digital hardware. Due

to the extremely high data rate requirements in radar applications, it is usually necessary to sacrifice flexibility in favour of speed and to use special purpose hardware. In a later section, the designs of a target Doppler processor and a two-dimensional digital beamformer will be discussed. These two examples will serve to demonstrate how one maximizes throughput rate and minimizes component count.

#### 2. THE FFT ALGORITHM

In order to select the most suitable approach to the hardware implementation of an algorithm, it is essential that one thoroughly understands the structure of the algorithm. This understanding will enable the circuit designer to take advantage of any parallelism or special constructs of the algorithm and match these to the capabilities of state-of-the-art hardware components.

In most standard digital signal processing texts [3]-[5], the FFT algorithm is explained both in terms of the decimation-in-time (DIT) and the decimation-in-frequency (DIF) processes. Generally, when these descriptions are applied to the FFT algorithm, they are meant to refer to any procedure in which the DFT of an N-point sequence is obtained by first computing the DFTs of two or more sub-sequences; i.e., by decimating the original sequence and then combining them in some fashion. The premise is that the total effort required for computing the smaller DFTs and combining the results is always less than that required for directly computing the DFT of the original N-point sequence. We will not proceed immediately with a proof of this premise, but rather, we will first discuss the basic concept underlying the FFT. It will then be shown that this decomposition reduces the computational overhead.

2.1 Two-dimensional representation of the DFT of a one-dimensional sequence

The DFT of an N-point complex sequence  $S:\{x_0,x_1,x_2,\ldots,x_{N-1}\}$  is defined as:

$$F_k = \sum_{n=0}^{n=N-1} x_n \exp(-j2\pi nk/N)$$

(1)

$$k=0,1,2,...,N-1$$

It is clear that to evaluate  $F_k$  for all N values of k,  $(N-1)^2$  complex multiplications and N(N-1) complex additions are required. A complex multiplication requires four real multiplications and two real additions. A complex addition requires two real additions. In subsequent discussions, unless otherwise noted, the terms multiplication and addition are understood to mean complex multiplication and addition, respectively. This estimate of the number of multiplications takes into account the fact that the exponential term  $\exp(-j2\pi nk/N)$  is unity for n=k=0. Although the term FFT was used initially in the work of Tukey et al [6] to mean a specific algorithm, much progress has been made since. Consequently, the FFT algorithm may now be regarded as any computational procedure which reduces significantly the required computational effort in evaluating Eqn (1).

It can be shown that both the so-called DIT and DIF processes lead to the same interpretation of the FFT algorithm. Rabiner and Gold[3] developed the mathematical treatment which led to a unified approach to the FFT. Their approach is based on the two-dimensional representation of a one-dimensional sequence. The DFT sum is transformed into a double summation. In the following, we shall present a development which shows how the two-dimensional representation of the DFT can be arrived at through the process of decimation. It will provide the linkage between the concepts of DIT and DIF. Some of the special terms such as butterfly, radix, twiddle factor and digit reversal will become clear as the development unfolds.

Consider an N-point complex sequence  $S:\{x_0,x_1,x_2,...,x_{N-1}\}$ . If N is not a prime number, then it can be expressed as a product of at least two numbers L and M, i.e.,

$$N = L \times M \tag{2}$$

The N-point sequence can be expressed as the sum of a number of auxiliary sequences. These auxiliary sequences are constructed from the original sequence by retaining a subset of the samples and padding the rest with zeros. One particular construction is as follows:

The N-point sequence is expressed as the sum of L auxiliary sequences  $S^0$ ,  $S^1$ ,  $S^2$ ,..., $S^{L-1}$ , which are defined in Eqn (3).

M Entries