CRC-CR-92-017 Roleasable.

# Analog-to-Digital Converter Technology for Digital Radio

Final Report

30th. March 1992

CONTRACTOR:

queens university

CRC SC. AUTH: V. Szwarc

DSS CONTRACT NO:

36001-1-3931

DATE OF REPORT:

1992

D. G. Nairn and W. M. Snelgrove

# Analog-to-Digital Converter Technology for Digital Radio

Table of Contents

- 1. Report on Analog-to-Digital Converter Technology for Digital Radio.

- 2. Appendix A Published Analog-to-Digital Converters 1980 1992

- 3. Appendix B Commercial Analog-to-Digital Converters

Industry Canada Library - Queen

AUG 2 0 2012

Industrie Canada Bibliothèque - Queen

# **CRC Report: Data converters for Digital Radio**

# 1: Introduction: Data converters in digital radio

Digital implementation of radios, as proposed in the CRC report "Proposal to Develop a Proof-of-Concept Digitally-Implemented Narrowband Radio" [1], offers advantages in flexibility and cost over purely analogue architectures. This report focuses on the data conversion issues for radios in which the IF and baseband signal processing are digital. Data converters would have to handle IF signals with centre frequencies in the 10-70MHz range, with bandwidths varying from a few kilohertz to more than a megahertz, and with SNR of about 70dB.

These are stringent requirements for the data converters, particularly for the A/D. When the radio is to be portable, power requirements are also tough. D/A converters exist that have the required speed and resolution at reasonable power, but A/Ds do not. This report shows why they don't, yet, but suggests that the problem is not fundamental.

We see two general approaches to data conversion at IF: broadband and bandpass conversion, where the latter is a very new technology. The original system design [1] assumes a broadband 8-bit converter running at 280MHz, giving roughly 9-bit accuracy in a 40MHz band (or 12 bits in 1MHz) through oversampling. Equivalent performance from a bandpass converter would be acceptable.

Data converters limit short-term development, because they make credible radio prototypes difficult to put together, and may — if fundamental — affect long-term radio architecture. Here we review the state of the art in converter performance, and estimate the likely progress of the technology by identifying theoretical and practical limitations on performance.

# 2: Video, voice and audio applications

Data converters currently available are aimed at applications other than digital radio. Comparing these applications with radio, in terms of conversion requirements, helps in seeing what issues will be important and what problems early prototypes can expect to have.

Table 1 summarizes major present applications and compares them to the radio needs outlined in [1]. Where a parameter is not critical, the entry is "—".

**Table 1: Data Converter Applications**

| *****                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |                                         |                                        |                                                             |                           |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------------|----------------------------------------|-------------------------------------------------------------|---------------------------|

| Application                       | Sample rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | bits  | Max<br>power                            | Linearity                              | Market                                                      | Nearest radio application |

|                                   | A CONTRACTOR OF THE CONTRACTOR |       | Analogue                                | to Digital                             |                                                             |                           |

| 70MHz IF                          | 280MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8 .   | 100mW                                   | high                                   | digital radio                                               | All                       |

| 10MHz IF                          | 40MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8     | 100mW                                   | high                                   | digital radio:<br>less general                              | BW<1Mhz                   |

| Sampling oscilloscope             | 50MHz-<br>2GHz -∞                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-7   |                                         |                                        | scientific                                                  | All except portables      |

| Radar                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | ·                                       |                                        | military                                                    | All except portables      |

| HDTV<br>(1125/60)                 | 75MHz or<br>muxed<br>150MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8     |                                         |                                        | consumer TV                                                 | 20MHz IF                  |

| TV (CCIR spec)                    | 13.5MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8     |                                         | ·                                      | multimedia,<br>eventually<br>consumer                       | 5-10MHz IF,<br>FM, TV     |

| N-ISDN                            | 200kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 14    | <u>:</u>                                | high                                   | business, then consumer telephone                           | FM                        |

| DAT                               | 50kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16-18 | some por-<br>tables                     | very high                              | consumer<br>audio                                           |                           |

| Voice codec                       | 8kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 13    |                                         |                                        | 1 per 'phone<br>at central<br>office; con-<br>sumer gadgets | AM                        |

| Meters                            | 10Hz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 20+ | some<br>handheld                        | high                                   | scientific and industrial                                   |                           |

| ;                                 | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       | Digital to                              | Analogue                               |                                                             |                           |

| Computer graphics and HDTV [2,23] | 130MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8     | 150mW                                   |                                        | professional/<br>scientific and<br>high-end con-<br>sumer   | 20MHz IF                  |

| TV-NTSC                           | 14.25MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8     | *************************************** |                                        | consumer                                                    |                           |

|                                   | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | L     | ·                                       | .l.,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 1                                                           | <u> </u>                  |

<sup>2:</sup> Converters for Digital Radio

**Table 1: Data Converter Applications**

| Application    | Sample rate | bits  | Max<br>power | Linearity | Market                                  | Nearest radio application |

|----------------|-------------|-------|--------------|-----------|-----------------------------------------|---------------------------|

| TV-<br>MAC[24] | 27MHz       | 8     | ·            |           | consumer                                | 10MHz IF                  |

| N-ISDN         | . 200kHz    | 14    |              | high      | business, then<br>consumer<br>telephone | FM                        |

| CD/DAT<br>[26] | 50kHz       | 16-18 | 15mW         | high      | consumer                                | FM/cellular               |

| Codec          | 8kHz        | 13    |              |           | telephony etc.                          | AM                        |

For speed, digital radio requirements are comparable with those for video and 'scope applications; but linearity and power (for portables) specifications are more stringent. In terms of circuits and performance limits, broadband converters for digital radio will therefore probably resemble video converters.

In terms of bandwidth and linearity, ISDN converters might be a better analogy. A bandpass converter would be likely to resemble these.

Converters are also produced as results of curiosity-driven research, with specifications not particularly adapted to any of the above applications.

This report therefore focuses on the types of converters used for video and ISDN, extrapolating their techniques and performance to the levels required for digital radios.

# 3: Converter speed, power and resolution: present art

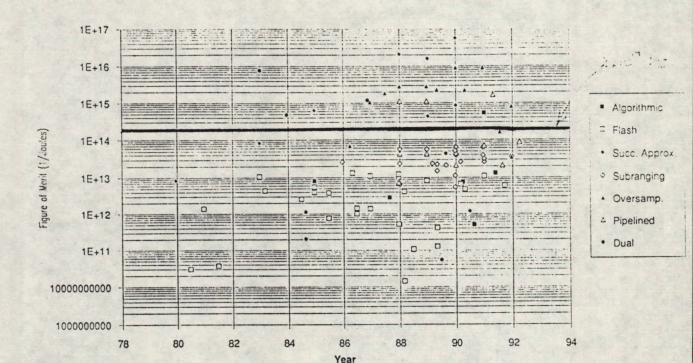

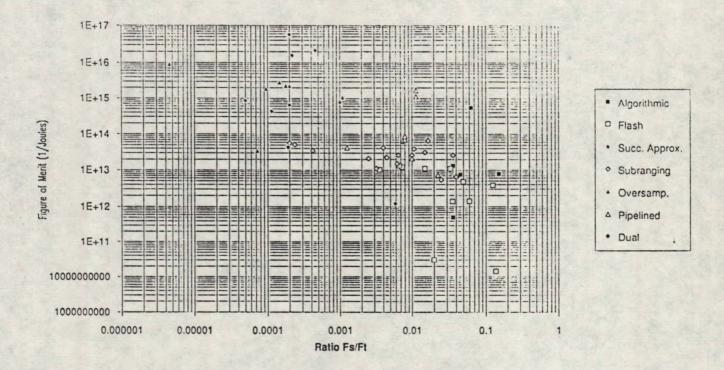

There are several trade-offs in converter design; the plots presented here illustrate them and show where the needs for digital radio fit in. Advancing technology improves performance, so plots present figures of merit against time to get an estimate of "how close" current technology is to being able to produce the devices required.

In these graphs there are generally large clusters of points, each corresponding to a choice of technology and to an application. Technology choices are distinguished by symbols, keyed in the graphs to descriptions which we elaborate in later sections.

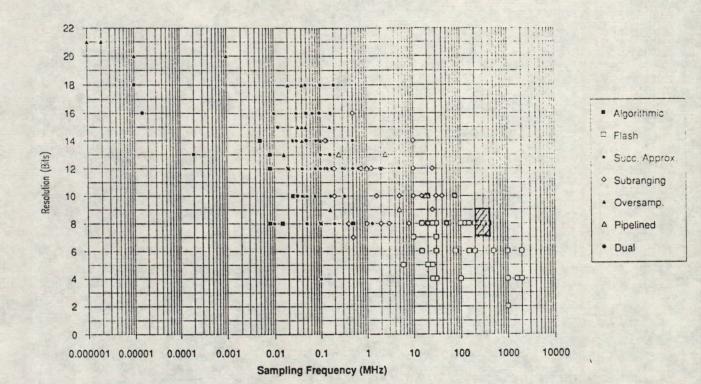

Accuracy and speed are competing objectives in converter circuit design. Figure 1 plots resolution (in bits) against sampling rate for about two hundred converters from the academic and industrial literature. There is a general downward trend indicating a trade-off of about 1 bit per octave in the best converters.

Figure 1: Resolution versus sampling rate

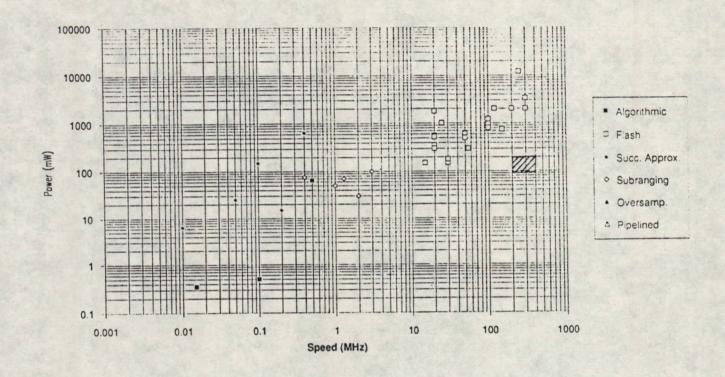

High-speed operation costs power: the power consumption of most converters has a large dynamic component, so that for a given converter  $P_d \propto f_s$ . There is also a fundamental limit requiring converters to draw a certain amount of power to get samples above thermal noise. This gives a lower bound on power that is proportional to frequency for a given resolution. Figure 2 plots power consumption against sampling rate for 8-bit converters. At present even the best converters require too much power for portable radios, but the 80MHz specification is close enough to the curve that a custom-designed part could probably be made with present technology. The 280MHz specification will require about an order of magnitude improvement.

Figure 2: Power versus sample rate for eight-bit ADCs

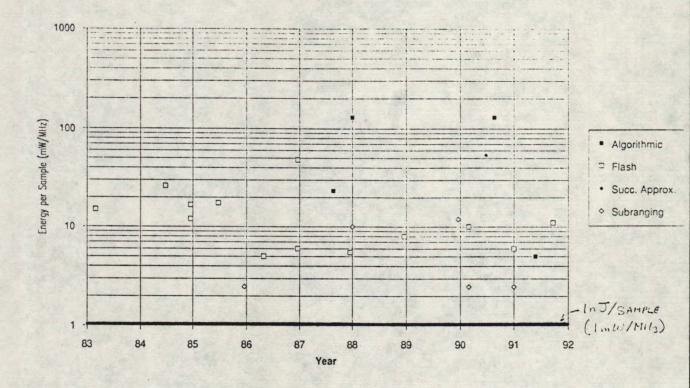

Advancing process and circuit technology can be used to improve power-efficiency or increase speed. Figure 3 plots a figure of merit — energy per sample — against the year of publication for eight-bit converters running in the MHz range. Commercial products are not directly shown, since their dates of introduction do not appear in manufacturer's data, but many commercial converters have been described in the technical literature, and these do appear. At 1nJ/sample (or 1mW/MHz, the bottom of the graph), a 280MHz converter would consume 280mW, and be a plausible component of a digital radio. The best 8-bit parts are running at about 2.5mW/MHz, and most run at about 10 — far too much for a portable radio. At the eight-bit level, designers are typically pushing speed rather than power.

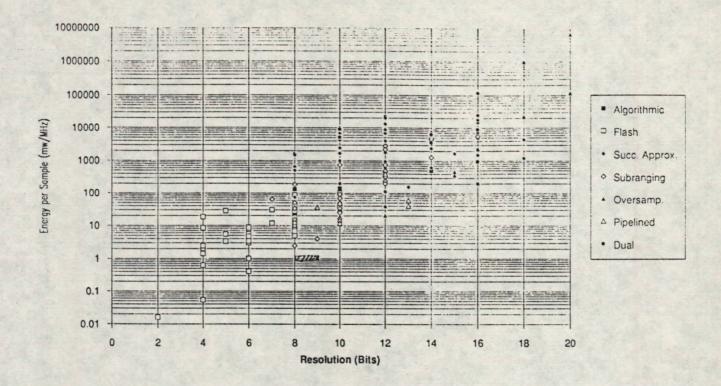

High resolution also costs power, so figure 4 plots energy/sample against resolution. The plot indicates an increase of a factor between 2 and 4 in power per bit of resolution, with a few high-resolution converters doing significantly better than the overall pattern.

Figure 3: Energy per sample versus time for eight-bit ADCs

The cost of resolution can be factored into a more sophisticated figure of merit with a (distant!) physical bound, SNR/ (energy/sample) [51,60]:

$$\frac{2^{2 \times \text{resolution}}}{\text{energy / sample}}$$

Eq. 1

The simplest bound on this quantity comes from the need for the energy on a sampling capacitor to exceed the thermal noise energy by a margin large enough to give the required dynamic range, and from assuming that this signal energy is dissipated when a new sample is read in. Equipartition of energy among thermodynamic states guarantees that thermal sources (such as thermal motion in channel charges of a switch) will leave an average noise energy (kT)/2 on the sampling capacitor. For a useful converter, the LSB can't afford to be smaller than this noise, so that the maximum signal voltage must by about  $2^N$  times larger — i.e. the maximum signal energy must be at least  $2^{2N}$  times larger, at

$$2^{2N-1}kT = 2^{2N}2.08 \times 10^{-21}$$

Joules

Figure 4: Energy/sample versus resolution

So the SNR/ (energy/sample) figure is bounded below

$$\frac{\text{SNR}}{\text{energy/sample}} < \frac{2}{kT} \approx 4.8076923 \dots \times 10^{20} \text{ Joules}^{-1}$$

Eq. 3

For 16-bit conversion, this bounds energy/sample above  $8.933532... \times 10^{-12}$  Joules — about  $9\mu W/MHz$ . A 280MHz/eight-bit converter running at the limit would dissipate only

$$2^{2(8)}2.08 \times 10^{-21}280 \times 10^6 \approx 38.168166... \text{ nW}$$

. Eq. 4

and conversely a "tolerable" 100mW dissipation level in the same converter would correspond to

$$\frac{\text{SNR}}{\text{energy/sample}} = \frac{280 \times 10^6 2^{16}}{0.1} \approx 1.835008 \times 10^{14} \text{Joules}^{-1}$$

Eq. 5

No present converters are near the ideal performance level, but quite a few are better than tolerable. Plotting the figure against year of publication gives figure 5. It is clear that there has been steady progress towards the bound, and that the best converters are within striking distance.

Figure 5: Energy/(sample.SNR) versus time, with a thermal bound

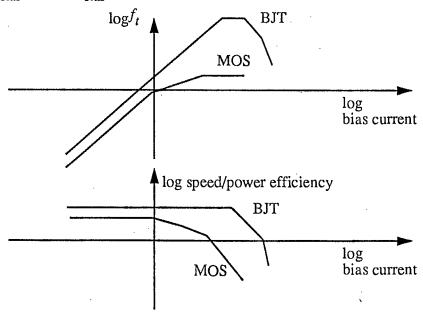

Practical video converters are orders of magnitude below the limit, and their performance is dominated by a range of practical problems. Technological changes are attacking these problems in a reasonably predictable way, which we will look at in more detail in sections 9. A way to summarize the effect of technology on performance is to look at converter speed as a fraction of  $f_t$ , the unitygain frequency of the transistors provided by the process. Over time the maximum attainable  $f_t$  (for MOSFETs, at any rate) has been steadily improving, pulling converter speeds in its wake. BJT  $f_t$  has been at a plateau for several years, but heterojunction bipolars will give an order of magnitude improvement in a few years.

Figure 6 plots energy efficiency (SNR/(energy/sample)) against sample rate relative to technology limits, showing the power penalty for running near the limits of a given process. The  $f_t$  figure used for BJTs is the maximum attainable, but that for MOSFETs is  $f_t$  when the devices are operated at the edge of the subthreshold region. This is because MOSFETs are often operated well below their best  $f_t$  because they have poor power efficiency at high bias levels. Some CMOS converters appear to operate very close to  $f_t$  because these are circuits that run their devices at an inefficient (but fast) high bias level.

Figure 6: SNR/(energy/sample) versus sample rate relative to unity-gain

A major part of the power penalty for "pushing" performance in a given technology comes from the need to use inefficient architectures at high relative speeds, as suggested by the keying of plot symbols to architectures — architectures change as speed goes up. These architectures are discussed in section 9.

### summary

A survey of some two hundred converters shows trade-offs among speed, power and resolution. Steady progress is being made in pushing back the envelopes defined by these trade-offs. The requirements for data converters for a 70MHz IF in a handheld radio (as in [1]) are beyond present technology but not implausible within a few years; a 20MHz IF at 200mW may be possible in a custom design with present technology. The input sample/hold is a problem all by itself, particularly for fast-slewing signals.

# 4: Sample/hold Performance: Limitations and Current Art

The input sample/hold circuit of an A/D is a problem for high-frequency inputs, and in fact aggressive tests of converter performance often drive inputs with large signals at frequencies comparable to the sampling rate in order to detect sample/hold errors. These are exactly the kinds of signals that can be expected in digital radios. Silicon sample/hold circuits have SNR below 40dB when input signals are in the 100MHz range, while GaAs gets similar accuracy out to 500MHz[36].

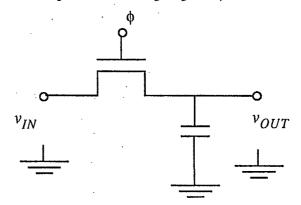

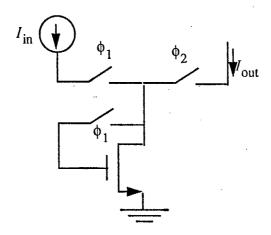

Figure 7 shows a basic sampling circuit: when  $\phi$  is **high** the output and input are supposed to track; when it goes **low** the value of the input at the falling edge of  $\phi$  should be held on C.

Figure 7: A simple sample/hold circuit

Firstly, when "on" the MOS switch has finite resistance. This means that the signal being tracked is a low-pass filtered version of the input. Converters are sometimes tested with high-frequency inputs to discover the 3dB frequency of the input sampler. Typically, if the switch has  $10k\Omega$  onresistance and C is 1pF, then the 3dB frequency is about 15MHz.

Secondly, the transistor doesn't turn "off" cleanly, but injects charge from the transistor channel into the sampling capacitor. There is a relationship between bandwidth for the "on" state and the error voltage from charge injection [17] that puts the resulting error in signal voltage at the 100mV level for fast samplers. This relationship is:

$$\Delta V = \frac{1}{\tau} \frac{L^2}{2\mu}$$

Eq. 6

where  $\tau$  is the lowpass time-constant when tracking, L is channel length,  $\mu$  is mobility and  $\Delta V$  is the minimum attainable error voltage.

For a 280MHz sampler to have 6τ to settle, and for 1μm n-channel devices,

$$\Delta V = \frac{6(280) \times 10^6}{1} \frac{10^{-12}}{2(0.066)} = 12.727273...\text{mV}$$

Eq. 7

The offset voltage that this produces is not critical for digital radio, but there are important secondorder effects because the amount of charge injected depends on the signal. In particular, there is a nonlinear component to the dependency that will contribute intermodulation distortion to the signal. Techniques used to reduce this problem are

- the use of balanced signals to cancel offset and even-order distortion products. This is more difficult if the original signal is single-ended, as the circuits for converting single-ended to balanced signals have their own problems, and does not reduce odd-order products such as the  $2f_1 f_2$  terms important in radio

- "bottom plate sampling", in which an additional switch disconnects the capacitor from ground in order to effect sampling. This reduces the signal voltage on the critical switch, so that charge dependencies are minimized. For high-frequency input signals, though, large  $C\frac{dv}{dt}$  signal currents force significant signal-related voltages across even a grounded switch and there is still a significant problem

- the use of short channel-length or high-mobility devices available in advanced process technologies

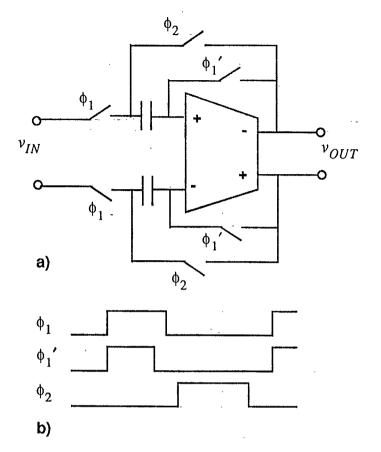

Figure 8a shows a typical modern balanced sample/hold [136]. It uses the clocks shown in figure 8b, includes a balanced buffer, and is also insensitive to capacitor nonlinearities.

Figure 8: Balanced sample/hold and its clocks

## aperture time and jitter

Small timing errors in sampling can contribute significant errors: a peak error of  $0.5\Delta$  will result, when a full-scale sine at the Nyquist frequency is applied, if the sampling time is wrong by one part in  $\pi 2^N$  — about 0.1% accuracy for compatibility with an 8-bit converter. These timing errors can come from clock jitter or from second-order circuit effects. For example, the simple sampler of figure 7 effectively samples when the transistor turns off, and that in turn is a function of the input voltage and the slope of the clock signal. Dependence of sampling time on signal voltage creates a kind of FM distortion, and practical clock slopes are slow compared to 0.1% of the sampling rates required for digital radio. Even the more sophisticated sampler of figure 8 has some sensitivity of sampling time to the slew rate of the input signal.

There is little uniformity in the literature as to reporting the linearity of input sample/hold circuits for high-frequency inputs, so the kind of summary data that is available for speed, resolution and power cannot be obtained. For example, though, the SNR of the AD9028 drops from 47dB at DC through 43dB for a 40MHz input to 36dB (equivalent to less than 6 bits) with a 92MHz input.

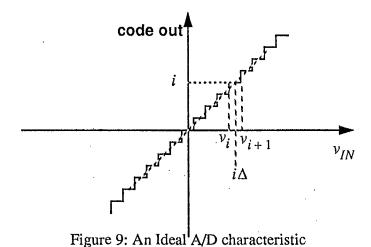

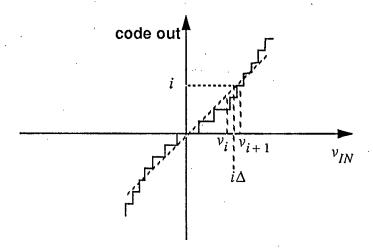

# 5: Linearity: Current Art

An ideal A/D converter is usually defined to have the "staircase" transfer characteristic shown in figure 9. Real converters are generally characterized by two different kinds of nonlinearity [5]: differential nonlinearity (DNL) models small perturbations of individual stepsizes from their ideal widths and integral nonlinearity (INL) describes maximum overall deviation from a best-fit straight line characteristic. Figure 10 shows a characteristic with high DNL, while figure 11 shows one with low DNL but high INL. High DNL implies high INL, but not vice-versa.

code out  $v_i$   $v_{i+1}$   $v_{IN}$

Figure 10: Non-ideal A/D characteristics with high DNL

Mathematically, differential and integral nonlinearity are functions of code output i:

Figure 11: Non-ideal A/D characteristics with high INL

$$DNL_i = (v_{i+1} - v_i) - \Delta$$

Eq. 8

$$INL_i = i\Delta - (\frac{v_i + v_{i+1}}{2})$$

Eq. 9

where  $\Delta$  is the step size (usually defined after the fact to minimize peak INL, so that gain errors are factored out) and the  $v_i$  are input voltages at which code transitions occur as shown in the figures. When a single figure is given for INL or DNL, it is the maximum of the function over i.

Differential nonlinearity usually limits practical resolution in video-type converters, so that typically converters are designed to have DNL levels on the order of one-half of the size of the least significant bit. The importance of DNL is often reduced by oversampling because large input signals convert the resulting error into a nearly-random component. For small inputs, though, it produces large relative amounts of intermodulation distortion products. Adding dither, a random noise component at the input, can randomize this error and convert distortion to (less noxious) noise[6].

Many practical converter architectures have their worst performance at the point where the MSB changes; since that is usually at zero input, where random signals spend most of their time, these converters are used at their worst-case operating point for DNL.

Noise-shaped converters (for details see section below) naturally dither their inputs, so that they usually have lower IM (especially for small inputs) than even an ideal converter. That could be very useful for digital radio. Circuit difficulties, specifically finite amplifier gain, and mathematical peculiarities degrade the effectiveness of this mechanism.

Integral nonlinearity can be input-referred to an equivalent polynomial distortion on the input, a type of nonlinearity familiar to radio engineers. It is not reduced by oversampling, and in many converters (especially video-rate converters) is larger than the LSB in peak magnitude. The nonlinearity of the sample/hold contributes to INL, but component nonlinearities and mismatches contribute too. These internal problems can add distortion terms of high degree, so that while third-order IM can be assumed to dominate conventional RF circuits the same cannot necessarily be said of an A/D. These high-degree terms may be a problem for digital radio, generating exotic mixing products.

The AD9028 converter, for example, specifies 1-bit INL and DNL, while the (slower, more accurate) AD9020 specifies 1 bit of DNL and 1.25 of INL.

Peak DNL and INL are good accuracy measures for instrumentation purposes, but not necessarily for radio. Video converters are often specified in terms of their signal/(noise+distortion) ratio for maximum-amplitude sines.

There are many other measures of nonlinearity: for example, when DNL is large enough output codes can disappear as the range of inputs able to produce them shrinks; converters without this problem are said to have "no missing codes", and any converter with worst-case DNL less than 0.5LSB is guaranteed to have no missing codes. Probably the most interesting such measure for digital radio is **noise power ratio**, which measures the extent to which IM distortion "fills in" a notch in an otherwise white input signal; this would be a good measure of receiver image rejection, but is rarely quoted.

#### Self-calibration

Some converters [97,98,99,101] obtain high resolution (14 bits or more) by including calibration circuitry. They usually require that the converter be taken off-line during calibration, and are significantly more complex than uncalibrated converters.

The most common technique [101] forces the analog step-size  $\Delta$  at each bit transition to be correct by measuring it during the calibration phase, then adding compensation components at run-time. In terms of the transfer characteristic, it moves thresholds left or right to their proper positions. These converters have been aimed at the audio market, and so are too slow for digital radio. The general idea could be applied at higher speeds, but video converters haven't usually demanded high resolution. The particular architectures to which self-calibration has been applied have been slow ones, so the details of the technique would have to be changed.

Another technique, not currently in a commercial converter, corrects on the digital side: the output of a nonlinear converter addresses a RAM containing accurate digital estimates of the corresponding analog transitions. In terms of the converter transfer characteristic, it leaves the thresholds where it finds them, but moves steps up and down. The output of the RAM is usually one or two bits wider than the converter data. The RAM is loaded by applying a test signal of known statistics during a calibration cycle. There are two problems with this for digital radio: it doesn't improve resolution, since many of the possible output values become missing codes; and the DSP requirements are increased because the words that must be handled are wider than the useful resolution.

A more recent technique currently under development [21] by Gu and Snelgrove does self-calibration of video converters on-line, moving analog thresholds so as to minimize DNL. It does not attempt to correct INL, but may improve the speed and resolution available in moderately power-efficient converters. If commercially practical, it may be a good candidate for oversampled digital radio in five to ten years. It will still need to be augmented by some technique to correct INL.

## Process scaling and device matching

As MOS process technology advances, the minimum channel-length gets smaller. This steadily improves area, speed and power consumption for digital circuits, but analogue circuits do not scale quite as well. Power limits from the need for signal energy to dominate thermal noise are unaffected by scaling, and the amount of energy that can be stored in a given silicon area actually decreases in newer technologies: thinner oxides increase capacitance per unit area but decrease allowable voltages, and because capacitor energy is  $(1/2) CV^2$  the net result is a loss. The components in newer technologies also suffer from non-ideal effects (like channel-length modulation, velocity saturation, threshold drifts and nonlinearities in passive components) at higher levels relative to the nominal behaviour, and circuit design is increasingly tightly constrained by the low power-supply voltages needed for the new small devices. Further: good matching of, for example, threshold voltages requires large areas even in a small-geometry process [18-].

These effects tend to push the natural division of functions between analogue and digital technologies towards the digital side. This is, of course, a major reason for the interest in digital radio, but it also pushes data converter design towards techniques that rely on digital processing rather than analog precision. This is a long-term force favouring oversampled techniques.

#### summary

Data converters have very complex nonlinearities, not generally well characterized for digital radio because the converters are designed and tested for other applications. Integral nonlinearity can be expected to be a problem, especially for a 70MHz input signal. Self-calibration techniques have been proposed that may mitigate linearity errors, but they remain to be proven for radio.

## 6: Oversampling and noise shaping

There are two related techniques, oversampling and noise shaping [63-86], that are important for digital radio. They are often conflated, but should be treated separately. "Oversampling" refers to sampling above the Nyquist rate, while "noise shaping" is a technique that uses feedback to control the spectrum of quantization noise. Noise shaping is most useful in combination with oversampling, and the combination is often loosely called "oversampling".

Sampling above the theoretical minimum rate has two general advantages: it eases specifications on analogue anti-aliasing (for A/D) and smoothing filters (for D/A) and it allows error averaging so that a lower-resolution converter can be used — an advantage of 1/2 bit per octave of oversampling. The disadvantages are that a faster converter is needed and that more computation is needed on the digital side.

From the point of view of converter requirements, oversampling trades speed for resolution. This has strong practical implications, because it gives the system designer a degree of freedom in choosing a converter and because any given technology has practical constraints on the frequency and resolution of which it is capable. The trade-off is in principle neutral as far as power dissipation is concerned, because for a given SNR in a given bandwidth the thermal-noise bound on power (see section 3 above) sees cancelling effects from increased frequency and decreased resolution. In practice it means that the freedom to exchange speed and resolution can be used to choose a converter that is well adapted to its technology.

The effect of oversampling on linearity is more complicated than its effect on noise. When signals are large and spectrally rich, differential nonlinearity may be randomized and so not be a problem; integral nonlinearity, however, can cause intermodulation products that are not affected by oversampling. Getting 12-bit conversion by oversampling an 8-bit A/D would call for an 8-bit converter with INL at the 12-bit level, and these converters do not exist — in fact it is more common that 8-bit converters have INL at the 6 or 7 bit level.

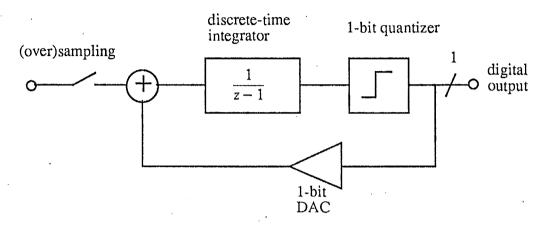

## Noise shaping

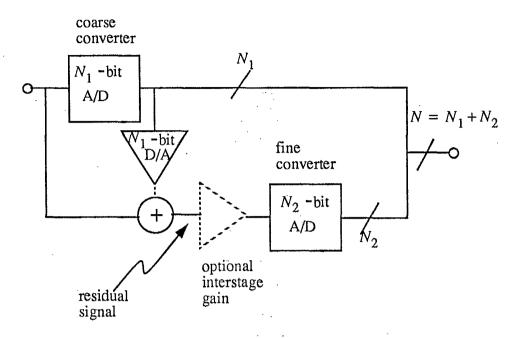

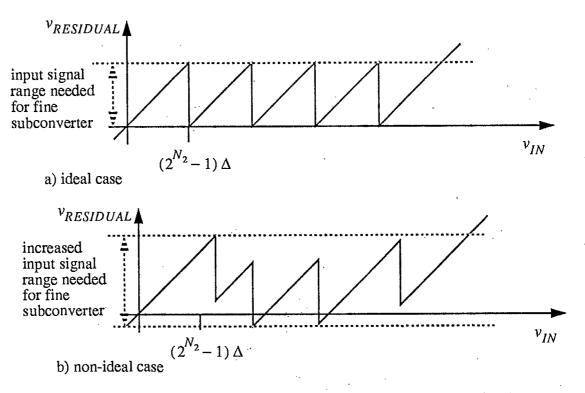

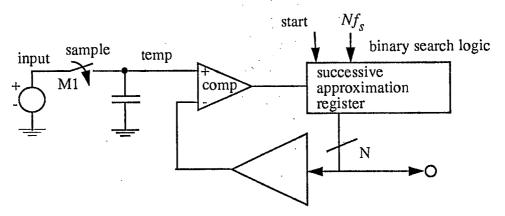

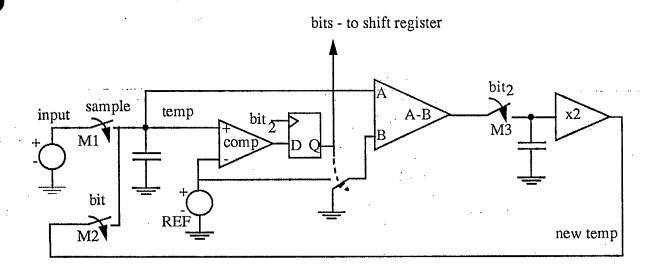

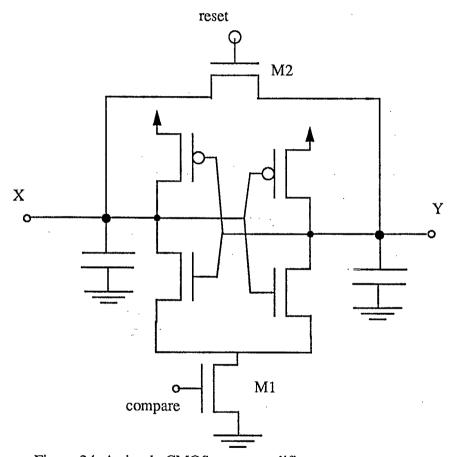

Noise shaping is a variation of oversampling in which quantizer outputs are fed back, through a filter, to the quantizer input in such a way that feedback controls the spectrum of quantization noise [8]. The resulting circuits are also called delta-sigma, sigma-delta, or bit-stream converters. Figure 12 is a block diagram of the well-known first-order noise-shaped A/D that illustrates the idea.

Figure 12: A first-order sigma-delta converter

First, a basic summary of A/D operation: if the signal at the output of the (discrete-time) integrator stays finite (because of the overall negative feedback), then the DC component at its input must be zero; but this means that the DC (average) value of the binary output stream is equal to the DC component of the analogue input. So averaging the binary output with a digital filter gives an A/D converter. The result is an extremely simple circuit (although only exactly described by very sophisticated mathematics) that produces highly linear converters tolerant of a wide range of circuit errors. Finite integrator gain and internal distortions seem to be the dominant problems.

For a first-order converter, linearity is dominated by the linearity of the feedback D/A converter. For this reason, one-bit converters are very popular: a converter that only has to produce two different values is inherently "linear". DNL is in fact very good, though there are second-order effects that can compromise INL. There is still an input sample/hold, so its contribution to INL remains.

A more sophisticated analysis of the first-order circuit [10] shows that the negative feedback does work, and that the feedback attenuates quantization noise in a band around DC. As sampling rate increases the noise shaping is proportionately more effective, so that it yields 1 bit less noise for each octave of oversampling; adding this to the 1/2b per octave gain from ordinary oversampling gives an overall noise-shaped oversampling gain of 1.5 bits per octave. Thus a 280MHz sampler

used in a first-order loop would have approximately 11-bit performance for a 40MHz signal bandwidth around DC (it has almost two octaves of oversampling beyond the 80MHz Nyquist rate, hence almost 3 bits of gain), where simple oversampling gives only about 9 bits.

Higher-order filters can be used, and give better performance; a second-order loop, for example, has a 2.5b/octave oversampling gain. Higher-order loops are also harder to design, as the mathematical theory needed to demonstrate their internal stability does not yet exist. This is a very active research area, and there is no clear consensus yet on attainable performance or best architectures. High-order filters tend, for example, to be stable with high-resolution quantizers in the loop and to dither DAC errors more thoroughly, but low-resolution D/A converters give better linearity. Despite their novelty and the difficulty of design, these converters are already dominant in high-linearity applications at moderate speed and should be taken seriously for digital radio.

#### Decimation

The high-rate digital signals from sigma-delta modulators are generally filtered and decimated down to baseband, and the DSP to do this has to be counted in the power budget. On the other hand, this filtering partly replaces analog anti-alias filtering, giving something back for this power. The decimators can be simple, because the input streams are narrow — usually only one bit wide. The two techniques used in commercial codes are

- 1 sinc<sup>n</sup> filters made up of counters and accumulators [9] which give simple implementations of mathematically simple impulse responses like triangles, and do a first-cut decimation which is followed by a conventional recursive digital filter.

- 2 general FIR filters implemented with ROMs and adder/subtracters [76,68].

## bandpass

Conventional sigma-delta converters shape noise away from DC, making them good candidates for baseband codecs in radios or for the conversion required in a zero-IF receiver. A very new technique [3,12,13,14,63,67] adjusts the filtering to move noise away from a passband, typically centred around  $f_s/4$ . A second-order bandpass sigma-delta converter behaves much like a first-order lowpass converter, so that 11 bit performance in a 40MHz band could be expected from noise-shaping a 280MHz 8-bit converter.

The first monolithic bandpass converter has just been fabricated [63]; it is a switched-capacitor device which provides fourth-order noise shaping of the noise from a 1-bit quantizer and can clock at up to about 3Mhz. It is intended to do 13-bit conversion of AM bandwidth signals centred around

455kHz. It is a two-channel part, for historical and research reasons. A simple approach to decimation, by modifying an existing decimator [76], would bring total power consumption to 450mW/ channel. Both power figures can be improved radically: power was not considered a major issue for the experimental device, and a factor 10 improvement would probably be easy enough to get.

The power, speed and resolution characteristics of bandpass converters are likely to be very similar to those of lowpass converters with similar bandwidths, so the lowpass literature can be monitored for an idea of the performance to expect. The ISDN converters in figure 1, with bandwidths ranging from 80 to 120kHz bandwidths, 10-15MHz sample rate, and 11-14-bit performance at 15-75mW, are good benchmarks. Though not commercially available, the experimental converter by Brandt and Wooley [65] is a particularly close fit: it clocks at 50Mhz, has 75dB SNR over a 1MHz bandwidth, and the analogue portion dissipates only 41mW (they only fabricated that part, so that there is no figure available for the power required for the decimator; this is likely to be in the 100mW range). This converter can be taken as a demonstration that the 1.25MHz bandwidth converters required by CRC are now feasible with 12 bits of resolution and perhaps 100-200mW of power.

The major differences between lowpass and bandpass noise-shaped converters will likely come from bandpass designs having a more difficult sample/hold problem (because of the high-frequency content of the input signal) but less trouble from 1/f noise in the input stage. The 1/f problem forces lowpass designs to use large input amplifiers at high resolutions, which wastes power and reduces speed.

There are also preliminary reports of high-speed bandpass modulators (clocking in the hundreds of megahertz) using continuous-time filters — discrete LC resonators. Descriptions in the open literature are still sketchy. Mathematical studies [15] suggest that these may have resolution limited by the Q available in the resonators, unless positive-feedback techniques are used.

While bandpass noise-shaping is a specialized research area, there is a good deal of industrial and academic interest and rapid development can be expected.

#### summary

Oversampling is a valuable technique that allows the system designer to trade speed for resolution and move some anti-alias filtering to the digital side of a system. It can be combined with noise-shaping, and a very recent version of this combination looks very promising for obtaining high resolution at low power for a moderate IF with present technology. Application to a 70MHz IF will be difficult in switched-capacitor technology, but the use of LC or other resonators might allow a breakthrough.

## 7: DAC Circuits

Digital-to-analogue converters are of interest for use in digital radio both in their own right and because A/D architectures often contain D/A subconverters. D/A converters are already available that are fast enough for digital radio and dissipate little power [22].

Oversampling techniques work for D/A as well as A/D, and have the same effects of moving complexity from the analogue to the digital side. Noise shaping is also used, particularly for digital audio, although it adds large amounts of out-of-band noise that must be filtered on the analogue side. At high speeds, non-feedback circuits are used, and three general types are in widespread use: resistor-string, charge redistribution and current-mirror. These can be used in combination.

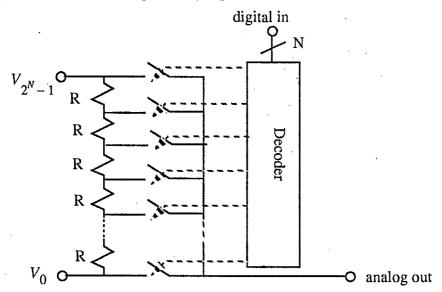

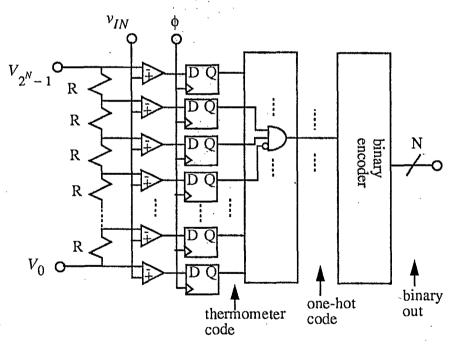

## **Resistor Strings**

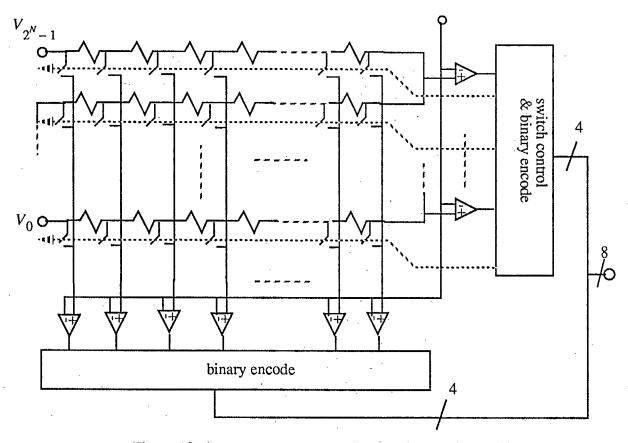

Conceptually, the simplest type of DAC consists of a string of resistors between two voltage references, with switches connecting the output to an appropriate point as shown in figure 13. Digital circuits are responsible for converting a binary input to a "one-hot" code to select the right tap.

Figure 13: A resistor-string D/A

Differential nonlinearity is very low in these D/A converters [7], because adjacent resistors are likely to be well-matched so that voltage steps are nearly equal [7]. Integral nonlinearity comes from

• resistor nonlinearity: the value of a resistor implemented in a monolithic process often depends slightly on its bias voltage above the substrate, as bias depletes the

resistor material of carriers. This produces a nonlinearity that is dominantly secondorder.

- output current: the output impedance of the string is low for codes near the top and bottom of the array and high for codes in the middle. This nonlinear output impedance, multiplied by output current, gives a (dominantly) third-order characteristic. Reducing the values of all the resistors reduces this effect, and  $1\Omega$  resistors are common [62]. This costs power.

- nonlinearity in the sample/hold used to de-glitch the output.

These converters dominate for producing the reference voltages for high-speed A/D converters, partly because they can produce many outputs simultaneously. Their INL performance therefore contributes to the INL of high-speed A/D, and their power consumption accounts for 10-100mW of an A/D power budget.

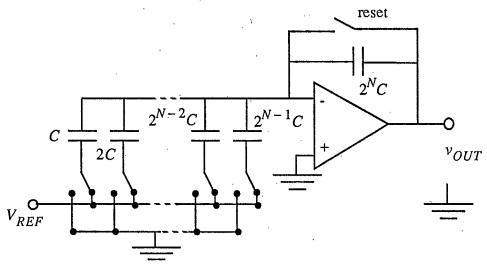

# Weighted capacitor array DACs

A switched-capacitor technique for D/A conversion uses a binary-weighted array of capacitors as shown in figure 14. After being charged to a reference voltage, a subset of capacitors is switched to the op-amp virtual ground transferring charge to the output. These are sometimes known as charge-redistribution ("QR", occasionally) converters.

Figure 14: A switched-C D/A with binary-weighted capacitors

The large capacitors in these converters are actually constructed as arrays of unit capacitors, so that although the number of capacitors in the schematic is linear in the number of bits in the converter, the number and area of capacitors fabricated is exponential in resolution, just as for the resistor string. These converters have differential nonlinearity dominated by capacitor mismatch at the most-significant bit transition: for example, in an eight-bit converter, the code 0x7f switches in 127 capacitors while 0x80 switches in 128 different capacitors, which may not be quite the right size. The alternative is to use a thermometer-code switching arrangement [28] as for resistor strings, which requires an exponential number of switches. The integral nonlinearity in these converters comes primarily from the same mechanism as the DNL, as long as the amplifier has a large enough output swing.

Current process technology, with careful layout, allows 10-12 bit accuracy in these converters [16]. There is no reason to think that this will improve very much with newer technologies. Charge-redistribution converters have been the standard at audio rates for telephone-quality resolution, and are also widely used internally in CMOS A/D converters.

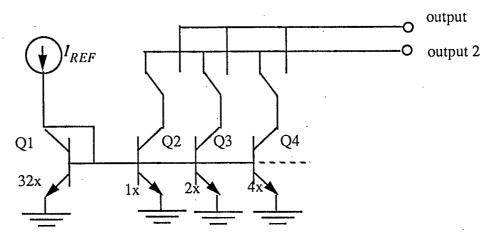

## Binary-weighted current sources

Two bipolar transistors with equal base-emitter voltages and equal areas produce approximately equal collector current. By connecting transistors in parallel, binary-weighted current sources can be obtained, and these currents can be switched into an output or to a supply to obtain a D/A as shown in figure 15. The notation "4x" just means that four unit devices are in parallel. The reference voltage needed for all the base-emitter junctions is usually obtained by driving a reference current into a transistor connected as a diode, as is Q1 in the figure. This arrangement is called a current mirror, since Q2 etc. "mirror" the reference current in Q1, scaled by the ratio of device sizes. The accuracy of matching between input and output currents is limited by base currents, output impedance and area mismatch between Q1 and Q2. More sophisticated mirrors exist which reduce the importance of base current and output impedance.

Just as for capacitor arrays, a thermometer-code switching arrangement can be used to control DNL.

<sup>&</sup>lt;sup>1</sup> In principle it is good enough to scale the junction areas of the devices, but the most accurate way to scale areas in the presence of lithographic errors and edge effects is to connect identical units in parallel, just as is done for capacitors.

Figure 15: A D/A with binary-weighted current sources