RELEASABLE DOC-CR-RC-88-007

SOFTWARE TOP LEVEL DESIGN DOCUMENT FOR THE INTERNETWORK GATEWAY PROJECT Submitted to: C.R.C. Ottawa, Ontario

SKL Document #1500-15-010.03.0 Copy #4 05 May 1988

QA 76.9 S88 S6478 1988

IC

RELEASABLE DOC-CR-RC-88-007

COMMUNICATIONS CLIER FER 8 1990 LIOUARY - BIOLIOTHEQUE

SOFTWARE TOP LEVEL DESIGN DOCUMENT FOR THE INTERNETWORK GATEWAY PROJECT Submitted to: C.R.C. Ottawa, Ontario

SKL Document #1500-15-010.03.0 Copy #4 05 May 1988

Industry Canada Library - Queen AUG 2 0 2012 Industrie Canada Bibliothèque - Queen

#### SOFTWARE TOP LEVEL DESIGN DOCUMENT

.

# FOR THE

#### INTERNETWORK GATEWAY PROJECT

Contract No. 36001-06-3535/02-ST

### 05 May 1988

Prepared for:

Communications Research Centre Ottawa, Ontario

Prepared by:

Software Kinetics Ltd. 65 Iber Road, P.O. Box 680 Stittsville, Ontario Canada KOA 3G0

SKL Document #1500-15-010.03.0

### Document Approval Sheet

### for the

### Internetwork Gateway Project

Document No: 1500-15-010.03.0

Document Name:

Software Top Level Design Document Internetwork Gateway for the Project

# Approvals

Signature

Date

R. Bra

Sym¢hy Μ. T. ch

P. Labbe CRC ----

88

Industry Canada Library - Queen AUG 2 0 2012 Industrie Canada Bibliothèque - Queen

Project Engineer:

Project Manager:

Technical Authority:

# Document Revision History

.

| Revision | Description of Changes              | Origin Date    |

|----------|-------------------------------------|----------------|

| 01       | New Document Issued                 | 22 May 1987    |

| 02       | Added Software Options              | 24 August 1987 |

| 03       | Coding and Integration<br>Revisions | 05 May 1988    |

#### TABLE OF CONTENTS

• •

· · · ·

| 1.0 | INTRO | DUCTION                      |                                      | 1    |  |  |  |  |  |  |  |  |  |

|-----|-------|------------------------------|--------------------------------------|------|--|--|--|--|--|--|--|--|--|

| 2.0 | REFEI | ERENCED/APPLICABLE DOCUMENTS |                                      |      |  |  |  |  |  |  |  |  |  |

| 3.0 | DESIC | SN                           | 3                                    |      |  |  |  |  |  |  |  |  |  |

|     | 3.1   | Softwar                      | e Architecture                       | 3    |  |  |  |  |  |  |  |  |  |

|     | 3.2   | Functio                      | nal Allocation                       | 6    |  |  |  |  |  |  |  |  |  |

|     |       | 3.2.1                        | Primary Boot                         | 6    |  |  |  |  |  |  |  |  |  |

|     |       | 3.2.2                        | Secondary Boot                       | 6    |  |  |  |  |  |  |  |  |  |

|     |       | 3.2.3                        | IP                                   | 10   |  |  |  |  |  |  |  |  |  |

|     |       | 3.2.4                        | Exterior Gateway Protocol (EGP)      | 10   |  |  |  |  |  |  |  |  |  |

|     |       | 3.2.5                        | Operator Interface (OI)              | 11   |  |  |  |  |  |  |  |  |  |

|     |       | 3.2.6                        | Statistics (STAT)                    | 11   |  |  |  |  |  |  |  |  |  |

|     |       | 3.2.7                        | X.25 Device Driver (XDD)             | . 11 |  |  |  |  |  |  |  |  |  |

|     |       | 3.2.8                        | Ethernet Device Driver (EDD)         | 12   |  |  |  |  |  |  |  |  |  |

|     |       | 3.2.9                        | Console Device Driver (CDD)          | 12   |  |  |  |  |  |  |  |  |  |

|     |       | 3.2.10                       | Efficient Real-Time Executive (ERTE) | 13   |  |  |  |  |  |  |  |  |  |

|     | 3.3   | Memory                       | Allocation                           | 14   |  |  |  |  |  |  |  |  |  |

|     | 3.4   | Functio                      | onal Control and Data Flow           | 18   |  |  |  |  |  |  |  |  |  |

| 1   |       | 3.4.1                        | Control Flow                         | 18   |  |  |  |  |  |  |  |  |  |

| /   |       | 3.4.2                        | Data Flow                            | 21   |  |  |  |  |  |  |  |  |  |

|     |       |                              | 3.4.2.1 Datagram and Route Data      | 26   |  |  |  |  |  |  |  |  |  |

|     |       |                              | 3.4.2.2 Traffic Data                 | 27   |  |  |  |  |  |  |  |  |  |

|     |       |                              | 3.4.2.3 Operator Interface Data      | 28   |  |  |  |  |  |  |  |  |  |

| 3.5 | Global | Data      |                                 | 29 |

|-----|--------|-----------|---------------------------------|----|

| 3.6 | Design |           |                                 | 36 |

|     | 3.6.1  | Primary B | oot TLC                         | 36 |

|     |        | 3.6.1.1   | Inputs                          | 37 |

|     |        | 3.6.1.2   | Local Data                      | 37 |

|     |        | 3.6.1.3   | Interrupts                      | 38 |

|     |        | 3.6.1.4   | Timing and Sequencing           | 38 |

|     |        | 3.6.1.5   | Processing                      | 38 |

|     |        | 3.6.1.6   | Outputs                         | 39 |

|     | 3.6.2  | Secondary | Boot TLC                        | 40 |

|     |        | 3.6.2.1   | Secondary Boot Local Boot       | 41 |

|     |        |           | 3.6.2.1.1 Inputs                | 41 |

|     |        |           | 3.6.2.1.2 Local Data            | 42 |

|     |        |           | 3.6.2.1.3 Interrupts            | 42 |

|     |        |           | 3.6.2.1.4 Timing and Sequencing | 42 |

|     |        |           | 3.6.2.1.5 Processing            | 42 |

|     |        |           | 3.6.2.1.6 Outputs               | 45 |

|     |        | 3.6.2.2   | Secondary Boot IGW Net Boot     | 45 |

|     |        |           | 3.6.2.2.1 Inputs                | 45 |

|     |        |           | 3.6.2.2.2 Local Data            | 46 |

|     |        |           | 3.6.2.2.3 Interrupts            | 46 |

|     |        |           | 3.6.2.2.4 Timing and Sequencing | 46 |

|     |        |           | 3.6.2.2.5 Processing            | 47 |

|     |        |           | 3.6.2.2.6 Outputs               | 48 |

|     |        | 3.6.2.3   | Secondary Boot Host Net Boot    | 48 |

|     |        |           |                                 |    |

.

~

•

# Software Kinetics

#1500-15-010.03.0

|       |           | 3.6.2.3.1   | Inputs     |            | 49 |

|-------|-----------|-------------|------------|------------|----|

|       |           | 3.6.2.3.2   | Local Data |            | 49 |

|       |           | 3.6.2.3.3   | Interrupts |            | 49 |

|       |           | 3.6.2.3.4   | Timing and | Sequencing | 50 |

|       |           | 3.6.2.3.5   | Processing |            | 50 |

|       |           | 3.6.2.3.6   | Outputs    |            | 53 |

| 3.6.3 | IP Protoc | col TLC     |            |            | 53 |

|       | 3.6.3.1   | Inputs      |            |            | 53 |

|       | 3.6.3.2   | Local Data  |            |            | 54 |

|       | 3.6.3.3   | Interrupts  |            |            | 55 |

|       | 3.6.3.4   | Timing and  | Sequencing |            | 55 |

|       | 3.6.3.5   | Processing  |            |            | 55 |

|       | 3.6.3.6   | Outputs     |            |            | 57 |

| 3.6.4 | EGP Proto | col TLC     |            |            | 57 |

|       | 3.6.4.1   | Inputs      |            |            | 58 |

|       | 3.6.4.2   | Local Data  |            |            | 58 |

|       | 3.6.4.3   | Interrupts  |            |            | 58 |

|       | 3.6.4.4   | Timing and  | Sequencing |            | 59 |

|       | 3.6.4.5   | Processing  |            |            | 59 |

|       | 3.6.4.6   | Outputs     |            |            | 60 |

| 3.6.5 | Operator  | Interface T | LC         |            | 60 |

|       | 3.6.5.1   | Inputs      |            |            | 60 |

|       | 3.6.5.2   | Local Data  |            |            | 61 |

|       | 3.6.5.3   | Interrupts  |            |            | 61 |

rate Mirris

:

# #1500-15-010.03.0

|       | 3.6.5.4   | Timing and Sequencing   | 61         |

|-------|-----------|-------------------------|------------|

|       | 3.6.5.5   | Processing              | 62         |

|       | 3.6.5.6   | Outputs                 | 65         |

| 3.6.6 | Statistic | es (STAT) TLC           | 66         |

|       | 3.6.6.1   | Inputs                  | 66         |

|       | 3.6.6.2   | Local Data              | 67         |

|       | 3.6.6.3   | Interrupts              | 69         |

|       | 3.6.6.4   | Timing and Sequencing   | 69         |

|       | 3.6.6.5   | Processing              | 69         |

|       | 3.6.6.6   | Outputs                 | 70         |

| 3.6.7 | X.25 Devi | ce Driver (XDD) TLC     | 70         |

|       | 3.6.7.1   | Inputs                  | 71         |

|       | 3.6.7.2   | Local Data              | 71         |

|       | 3.6.7.3   | Interrupts              | 72         |

|       | 3.6.7.4   | Timing and Sequencing   | 72         |

|       | 3.6.7.5   | Processing              | 73         |

|       | 3.6.7.6   | Outputs                 | <b>7</b> 5 |

| 3.6.8 | Ethernet  | Device (EDD) TLC        | 75         |

|       | 3.6.8.1   | Inputs                  | 76         |

|       | 3.6.8.2   | Local Data              | 76         |

|       | 3.6.8.3   | Interrupts              | 77         |

|       | 3.6.8.4   | Timing and Sequencing   | 77         |

|       | 3.6.8.5   | Processing              | 78         |

|       | 3.6.8.6   | Outputs                 | 81         |

| 3.6.9 | Console I | Device Driver (CDD) TLC | 81         |

·

# Software Kinetics

:

|        | 3.6.9.1          | Inputs                     | 82  |

|--------|------------------|----------------------------|-----|

|        | 3.6.9.2          | Local Data                 | 82  |

|        | 3.6.9.3          | Interrupts                 | 83  |

|        | 3.6.9.4          | Timing and Sequencing      | 83  |

|        | 3.6.9.5          | Processing                 | 84  |

| 3.6.10 | Efficient<br>TLC | Real-Time Executive (ERTE) | 85  |

|        | 3.6.10.1         | Inputs                     | 86  |

|        | 3.6.10.2         | Local Data                 | 89  |

|        | 3.6.10.3         | Interrupts                 | 92  |

|        | 3.6.10.4         | Timing and Sequencing      | 96  |

|        | 3.6.10.5         | Processing                 | 96  |

|        | 3.6.10.6         | Outputs                    | 98  |

| RY     |                  |                            | 100 |

.

# 4.0 GLOSSARY

#### 1.0 INTRODUCTION

The Top Level Design (TLD) of the Internetwork Gateway (IGW) software is presented in this document. The components of the design are identified and described. Also presented are the functions allocated to each component, the functional control and data flow among the components, global data, important local data, inputs, outputs, interrupts, and processing.

The IGW is a gateway between networks operating under the DARPA Internet protocols. Specifically, the IGW is a gateway between X.25 based TCP/IP networks and Ethernet based TCP/IP networks. The IGW supports the IP,ICMP, EGP, ARP, and X.25 protocols.

#### 2.0 REFERENCED/APPLICABLE DOCUMENTS

- 1) 1500-15-002.01.0, "Requirements Specification for the Internetwork Gateway", Software Kinetics Ltd., 1987.

- 2) "VAX Architecture Handbook", Digital Equipment Corporation, 1981.

- 3) Defense Advanced Research Projects Agency, "Internet Protocol", DARPA Network Working Group Report RFC-791, USC Information Sciences Institute, September 1981.

- 4) Defense Advance Research Projects Agency, "Internet Control Message Protocol", DARPA Network Working Group Report RFC-792, USC Information Sciences Institute, September 1981.

- 5) Defense Advanced Research Projects Agency, "Exterior Gateway Protocol Formal Specification", DARPA Network Working Group Report RFC-904, M/A-COM Linkabit, April 1984.

- 6) Reltek Inc., "Q-Bus X.calibre FEP COMII-Q Technical/Users's Guide", Reltek Inc., 1985

- 7) Plummer, D., "An Ethernet Address Resolution Protocol", DARPA Network working Group Report RFC-826, Symbolics, September 1982

#### 3.0 DESIGN

#### 3.1 Software Architecture

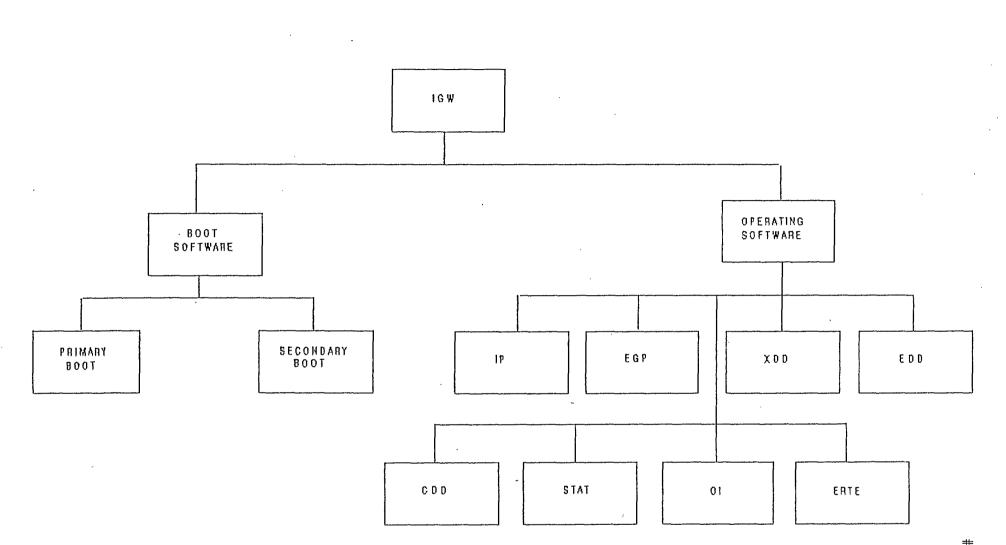

The IGW consists of software components that are divided into two classifications: Boot Software, and Operating Software. The Boot Software is responsible for loading the Operating Software from the boot device. The Operating Software is responsible for performing all the gateway functions of the IGW, including input and output.

The Boot Software is composed of two Top Level Components (TLCs). The first TLC is the Primary Boot component which performs basic initializations of the gateway hardware, and then loads the second component, the Secondary Boot TLC. The Secondary Boot TLC is responsible for loading the Operating Software into the gateway memory, and then starting the Operating Software.

The Operating Software consists of a set of TLCs each having certain responsibilities to perform with respect to IGW operation. The operating TLCs are listed as follows:

- 1) IP This TLC implements the IP protocol, the ICMP protocol, and packet filtering.

- 2) EGP This TLC implements the EGP Internet protocol.

- 3) Operator Interface (OI) The OI TLC presents a simple command line interface to the IGW operator to allow the operator to extract information and statistics and to modify IGW operating parameters.

- 4) Statistics (STAT) STAT gathers statistics from the other TLCs of the IGW. In particular, the STAT TLC tallies packets to and from IP and X25 addresses, error packets sent and received, and data bytes

transmitted between hosts via IGW.

- 5) X.25 Device Driver (XDD) This TLC controls the operation of the IXIB X.25 interface. The XDD passes packets to, and receives packets from the IXIB. It also collects status information from the IXIB and provides configuration parameters to the IXIB.

- 6) Ethernet Device Driver (EDD) The EDD TLC manages the Ethernet hardware interface for the IGW. The TLC prepares packets for transmission and invokes the transmission facility, invokes the receive facility and collects received packets, and implements the ARP protocol for Ethernet - Internet address resolution.

- 7) Console Device Driver (CDD) This TLC supports the VAX console device hardware which is used for the Operator Interface. The TLC supports the use of hardcopy or video terminals which support the ASCII character set.

- 8) Efficient Real-Time Executive (ERTE) - The ERTE is a small, real-time, multi-tasking executive which supports the preceding TLCs. Each of the above TLCs contains one or more processes whose execution the ERTE manages. The ERTE implements a combination of round-robin and priority based scheduling of This permits processes to reasonably processes. alternate execution while permitting critical processes, such as interrupt servers, to obtain priority service. The ERTE recognizes all interrupts and dispatches the correct interrupt server. The ERTE also supplies a message passing facility to allow processes to communicate with other processes. ERTE also supplies sleep, wake-up, and time-out facilities to processes.

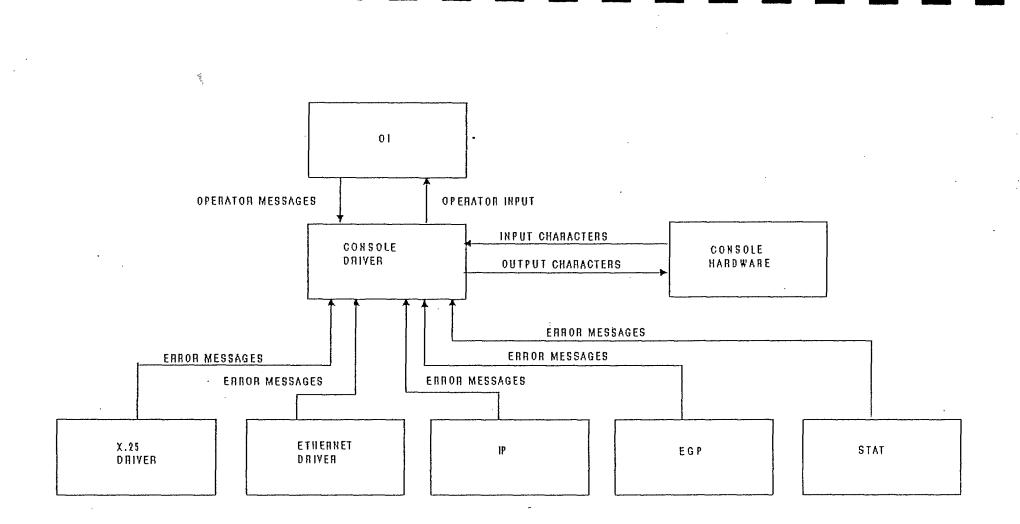

FIGURE 1 IGW SOFTWARE ARCHITECTURE #1500-15-010.03.0

ហ រ

1

#### 3.2 Functional Allocation

In this section the allocations of functions to the TLCs is presented. Each function is associated with one or more requirements from the Requirements Specification [1]. The associated requirements are also listed in this section.

#### 3.2.1 Primary Boot

The Primary Boot TLC is a small portion of code which is stored in block number 0 on the boot device. It is automatically loaded from the boot device by VAX system software in read-only memory (ROM) each time the IGW is booted. This TLC's function is to find the secondary boot program on the boot device, load it into memory, and start it executing. The Primary Boot will relocate itself into high memory. The Primary Boot will load the Secondary Boot into low memory.

#### 3.2.2 Secondary Boot

The Secondary Boot TLC will read all the operating software and configuration data and install it into the IGW memory. The Secondary Boot will also read the IXIB software and download this to the IXIB hardware. The Secondary Boot will establish all memory management tables and hardware for the IGW. Finally, the Secondary Boot will transfer control to the operating software, at which time, the memory occupied by the Secondary Boot and the Primary Boot will become available for use by the operating software.

The Secondary Boot TLC consists of two components: A Local Boot component and a Net Boot component. The Local Boot resides

entirely on the IGW local boot device and it in turn expects all software and data required for booting the IGW to reside on the boot device. The Net Boot component resides partly on the IGW boot device, and partly on a cooperating host on the Ethernet to which the IGW is attached. The Net Boot permits the IGW to receive its software and configuration data from the cooperating host via the Ethernet. Only one of these components resides on the boot device at one time.

The Net Boot component consists of two distinct elements: The IGW Net Boot and the Host Net Boot. The IGW Net Boot sends a signal to the Host Net Boot requesting that the Host Net Boot supply the IGW with a loadable image. The Host Net Boot, upon receiving the signal from the IGW Net Boot builds an image of the IGW with all software and configuration data in place, and then sends this image to the IGW. The IGW Net Boot loads this image into memory. Once the image is loaded, the IGW Net Boot transfers control to the operating software.

The requirements listed in the Requirements Specification [1] in Section 3.1 paragraphs 2 and 4, and in Section 3.2.2 paragraph 3 apply to the Secondary Boot TLC. The applicable requirements are shown in Table 1, the Requirements Cross-Reference Table.

|                                                                                     | REMENT :                                                           |                                          | =======                                 |                       |                       |                                      | VEL C<br>=====        |                                      |                 |        | =======                                                                                           |                        | ;<br>=====                                     |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------|-----------------------------------------|-----------------------|-----------------------|--------------------------------------|-----------------------|--------------------------------------|-----------------|--------|---------------------------------------------------------------------------------------------------|------------------------|------------------------------------------------|

| Section<br>#                                                                        | l Paragraph I                                                      | 1    <br>  N/A                           | Fri. <br>  BOOT                         | Sec.1<br>BOOT!        | I<br>ERTEI            | <br>IF:                              | <br>EGP               | ן<br>1 ונס                           | STAT            | ROUTE  | Ether!<br>Drvr                                                                                    | X.25)<br>Drvrl         | Cons<br>Drvr                                   |

| .0                                                                                  | F                                                                  | 1                                        | l 1                                     |                       | 1                     | 1                                    | <br> <br> <br>        |                                      | 1               | 1      |                                                                                                   |                        | 1                                              |

| 2.0                                                                                 | 1 – 1                                                              | 1 X                                      |                                         |                       |                       | 1                                    | •                     | 1                                    |                 |        | 1                                                                                                 |                        | 1                                              |

| 3.0<br>3.1                                                                          | 1<br>12<br>13<br>14<br>5                                           |                                          | ×                                       | x<br>x                | X<br>X<br>X<br>X      | X :<br>X :<br>1                      | X                     | x<br>x<br>x<br>x                     | X               | X<br>X | X                                                                                                 | X  <br>X  <br>         | X .<br>X<br>X<br>X                             |

|                                                                                     | 1 7                                                                |                                          |                                         |                       | , ,<br>               |                                      |                       | x                                    |                 |        | 1                                                                                                 | 1                      | :                                              |

| 3.2<br>3.2.1<br>3.2.1.1                                                             | 1 (1.)<br>1 (2.)<br>1 (3.)<br>1 (4.)<br>1 (5.)<br>1 (6.)<br>2<br>3 |                                          |                                         |                       |                       | X<br>X<br>X<br>X<br>X<br>X<br>X<br>X | X<br>X<br>X           | - X                                  | ;               |        | X<br>X<br>X                                                                                       | X<br>X<br>X<br>X       | x                                              |

| 3.2.1.2<br>3.2.1.2.1<br>3.2.1.2.2<br>3.2.1.2.3<br>3.2.1.2.3<br>3.2.1.2.4<br>3.2.1.3 | ; A11<br>; A11<br>; 1<br>; 1<br>; 1                                | X<br>   <br>   <br>   <br>   <br>   <br> | : : : : : : : : : : : : : : : : : : : : |                       |                       |                                      | <br>  X<br>           | <br> <br> <br> <br> <br>  X          |                 |        | X                                                                                                 |                        | x                                              |

| 3.2.1.4                                                                             |                                                                    | 1 1<br>1 1                               | 1                                       | ;                     | ;<br>;                | X<br>                                | 1<br>1 X              | 1                                    | 1               | !<br>! |                                                                                                   | }<br>}                 | 1                                              |

| 3.2.2                                                                               | 2                                                                  | ; )<br>                                  | 1                                       | ¦<br>;                | 1                     | ;<br>;                               | ;<br>;                | <br>                                 | ;               | 1      | 1 X                                                                                               | 1 X                    | 1                                              |

| 3.2.3                                                                               | 2<br>  3<br>  1<br>  2 (1.)<br>  2 (2.)                            | 1 1<br>1 2<br>1 1<br>1 1<br>1 1          | 1<br>  X<br> <br>                       | <br>  X<br> <br>      |                       | <br> <br>  X<br>  X                  | ;<br>;<br>;<br>;<br>; |                                      | -               |        | 8<br>6<br>8<br>9<br>7<br>7                                                                        | <br> <br> <br> <br>  X |                                                |

| 3.2.4                                                                               | 2 (3.)<br>  2 (4.)<br>  1 (1.)<br>  1 (2.)<br>  2<br>  3           | 1 1<br>1 1                               |                                         | •<br>•<br>•<br>•<br>• | r<br>;<br>;<br>;<br>; | X<br> <br> <br>                      | ;                     | :<br>: X<br>: X<br>: X<br>: X<br>: X | X<br> <br> <br> |        | t<br>57<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8 | X<br>  X<br>  X<br>    | 1<br>2<br>7<br>8<br>3<br>3<br>4<br>4<br>1<br>1 |

| 3.2.5<br>3.2.6                                                                      | 1                                                                  | 1 1<br>1 1                               | 1<br>1                                  | ł                     | : X<br>:              | {<br>                                | 1                     | X<br>  X                             | :               | ;      | ;                                                                                                 | 1                      | ¦<br>I X                                       |

| 3.3                                                                                 | ł                                                                  | 11<br>11 X                               | 1                                       | 1                     | 1<br>1                | <br>                                 | 1                     | :<br>1                               | 1               | 1      | 1                                                                                                 | 1                      | <br>                                           |

|                                                                                     |                                                                    | 11                                       | 1                                       | ł                     | 1                     | :                                    | 1                     | 1                                    | :               | ł      | 1                                                                                                 | 1                      | I                                              |

#### Table 1: Requirements Cross-Reference Table

Page 1 of 2

#1500-15-010.03.

r\*\*

.

Software Kinetics

| #                                       |                     | N/A                    | BOOT            | 800T !                                  | ERTE            | IF:                                            | EGP           | DI                 | STAT                                    | ROUTE                                                                   | Drvr                     | Drvr                | Drvr                                    |

|-----------------------------------------|---------------------|------------------------|-----------------|-----------------------------------------|-----------------|------------------------------------------------|---------------|--------------------|-----------------------------------------|-------------------------------------------------------------------------|--------------------------|---------------------|-----------------------------------------|

| ;<br>;1.0                               |                     | l<br>l X               |                 |                                         |                 |                                                | 1             | 1                  |                                         | 1                                                                       |                          | f<br>1              |                                         |

| 12.0                                    | I – I               | 1 X                    |                 |                                         |                 |                                                |               |                    |                                         |                                                                         |                          | 1                   |                                         |

| <br> 3.0<br> 3.1<br> <br>               | 1  <br>  2  <br>  3 |                        | <br> <br>  X    |                                         | X<br>X          |                                                |               | X<br>X<br>X        | X<br>X                                  | X<br>X                                                                  | X<br>X                   | <br>  X<br>  X      | <br>  X.<br>  X<br>  X                  |

| ;<br>;<br>;<br>;                        | 1 5 1               |                        |                 |                                         | X<br> <br> <br> | ;<br>;                                         |               | X<br>X<br>X        | I X                                     | x                                                                       |                          | <br> <br> <br>      | <br>  X<br> <br>                        |

| 13.2<br>13.2.1<br>13.2.1.1              | 1 (1.)<br>1 (2.)    |                        |                 | -<br>-<br>-<br>-<br>-<br>-              | <br> <br> <br>  |                                                | I X           |                    |                                         |                                                                         | <br> <br>  X<br>  X      | <br> <br>  X<br>    | ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; |

| <br> <br> <br>                          |                     |                        | <br> <br>  '    |                                         | :<br>:<br>:     | 1 X<br>1 X<br>1 X                              | ; X           | <br> <br> <br>  X  | <br> <br>  X                            | a<br>4<br>7<br>7<br>1<br>7<br>7                                         | : X<br>: X<br>: 1<br>: X |                     |                                         |

| 13.2.1.2<br>13.2.1.2.1<br>13.2.1.2.2    | 3<br>  1<br>  A11   | X                      |                 | ,<br>]<br>]<br>[                        | 1               | X<br>                                          | 1             | X<br> <br> <br>    | · • • • • • • • • • • • • • • • • • • • | r<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8 | : X<br>:<br>:            | X<br>I<br>I         |                                         |

| 3.2.1.2.3<br> 3.2.1.2.4<br> 3.2.1.3<br> |                     | <br>   <br>   <br>  {  | <br> <br>       | ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; | :               | <br>  X<br>  X                                 | ;             | :<br>1<br>1<br>1 X | ;<br>;<br>;                             | :<br>;<br>;                                                             | <br>  X<br>              | *<br>*<br>1         | <br> <br>  X                            |

| <br> 3.2.1.4<br>!                       | -                   | <br>   <br>            | <br> <br>       | ;<br>;<br>;                             | ;<br>;<br>;     | X<br> <br>!                                    | <br>  X       | <br> <br>!         | 1                                       | 1                                                                       | <br> <br>  X             | <br> <br>  X        | 1                                       |

| 13.2.2<br>1                             | 1<br>  2            | 11 X<br>11             | 1               | ;<br>;                                  | i<br>i X        | ;<br>;                                         | ;<br>;<br>;   | :<br>: X           | 1                                       | 1                                                                       |                          |                     | 1<br>1 X                                |

| <br> 3.2.3<br> <br>                     | 1<br>1<br>2 (1.)    | 1                      | X<br> <br> <br> | X<br> <br>                              | 1 X<br>1<br>1   | <br>  X<br>  X                                 | 1<br> <br>    | X<br>  X<br> <br>  | 1 X<br>1 X<br>1 X                       |                                                                         |                          | 1                   |                                         |

| <br> 3.2.4<br>                          | i 2 (4.)<br>i (1.)  |                        |                 |                                         |                 | 1<br>  X<br> <br>                              | :<br>:<br>: X | I X<br>I X         | X<br>  X<br> <br>                       |                                                                         |                          | X<br>    X<br>    X | 1                                       |

| 13.2.5<br>13.2.6                        | ; .3<br>; 1<br>; 1  | 1  <br>1  <br>1        |                 | 1<br>1<br>1<br>1                        | i X             | ;<br>;                                         | 4<br>9<br>9   | X<br>  X<br>  X    | i<br>;<br>;                             | •<br>•<br>•                                                             | 1<br>1<br>1<br>1         |                     |                                         |

| 13.3<br>1                               |                     | 11<br>11<br>11 X<br>11 | 1               | ¢<br>1<br>7<br>7<br>7                   | :               | ,<br>,<br>,<br>,<br>,<br>,<br>,<br>,<br>,<br>, | 1<br>1<br>1   |                    |                                         | r<br>4<br>7<br>8<br>8                                                   | •<br>}<br>1              |                     |                                         |

1 ω I

| KEQUIR         Section         #         3.4         3.4.1         3.4.2         3.4.2         3.4.2         3.4.2.1         13.4.2.2         13.4.2.3 | EMENT<br>==================================== | <br>    ==<br>   <br> | ====== |            |                | то       |           | VEL C      |           |             |                                         |                |                |              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------|--------|------------|----------------|----------|-----------|------------|-----------|-------------|-----------------------------------------|----------------|----------------|--------------|

| Section :<br># 1<br>3.4 1<br>3.4.1 1<br>3.4.2 1<br>3.4.2.1 1<br>3.4.2.2 1                                                                              | Faragraph<br>#<br>===========                 | <br>                  | !      |            |                |          |           |            |           |             |                                         |                |                |              |

| 3.4     1       3.4.1     1       3.4.2     1       3.4.2.1     1       3.4.2.1     1                                                                  |                                               |                       | N/A I  |            | Sec.!<br>BOOT! | ERTE /   | !<br>IF'; | ;<br>EGP i | ;<br>; 10 | 1<br>STAT I | :<br>ROUTE                              | Ether!<br>Drvr | X.251<br>Drvri | Cons<br>Drvr |

|                                                                                                                                                        |                                               |                       |        | 1          | I              |          |           | ;          | 1         | ;           | 1                                       | 1              | !              |              |

| 3.4.2.1  <br>3.4.2.2                                                                                                                                   |                                               | []                    | ;      | :          | !              | 1        | ł         | ;          | ;         | 1           | 1                                       | 1              | XI             |              |

| <br> 3.4.2.1  <br> 3.4.2.2                                                                                                                             |                                               | 11                    | 1      |            | 1              | 1        | 1         | 1          | 1         | 1           | 1                                       |                | X              |              |

| 13.4.2.2 1                                                                                                                                             |                                               | 11                    | 1      |            | 1              | 1        | 1         | ł          | 1         |             | 1                                       | X I            |                |              |

| 13.4.2.2                                                                                                                                               |                                               |                       | X      |            | -              | 1        | 1         | -          | ł         |             | -                                       | ł              |                |              |

|                                                                                                                                                        |                                               |                       | 1      |            | i              | i        |           |            | :         |             |                                         |                | 1              |              |

| 13-4-2-5 1                                                                                                                                             |                                               | 11                    | i      |            |                | ł        | XI        |            | i<br>,    | i           |                                         | XI             |                |              |

| 1 7 4 5 4 1                                                                                                                                            |                                               | 11                    | 1      |            | ;              | į        |           | •          | i         | i           | ł                                       | X              | i i            |              |

| 3.4.2.4                                                                                                                                                | -                                             | 11                    | i      | i i        | i              | i        |           |            | i         | i           | i                                       |                | i i            |              |

| i i                                                                                                                                                    |                                               | }                     | i      | i i<br>1 I | i<br>1         | ,        | X         | •          | 1         | 1           | , , , , , , , , , , , , , , , , , , , , |                | t 1<br>I 1     |              |

| 1 1<br>1 1                                                                                                                                             |                                               |                       |        | • •        | ۰<br>۲         |          | ;         |            | . 1       |             | 1                                       |                | 1 <i>1</i>     | i.           |

| 4.0                                                                                                                                                    |                                               |                       | x      | · · ·      |                |          | 1         |            | •         |             | 1                                       |                | 1 I<br>1 I     |              |

| 1 1                                                                                                                                                    |                                               | 11                    | ^      | 1 1<br>7 1 | 1              |          | •         | ,          |           | 1           |                                         |                | ۱ ۱<br>۱ ۱     |              |

| • • •                                                                                                                                                  |                                               | 11                    |        | , ,<br>, , |                |          |           | . 1        |           | 1           |                                         |                |                | 1            |

| 1                                                                                                                                                      |                                               | 11                    |        | · ·        | 1              | 1        |           |            |           |             |                                         |                | 1<br>1         | Į            |

| 1 1                                                                                                                                                    |                                               |                       |        | • •        |                | 1        |           |            |           |             |                                         |                |                | 1            |

| 1                                                                                                                                                      |                                               | 11                    |        | 1          |                |          | 1         |            |           |             |                                         |                |                | ł            |

|                                                                                                                                                        |                                               | 11                    |        |            |                |          | ļ         |            |           |             |                                         |                |                | 1            |

| 1                                                                                                                                                      |                                               | 11                    |        | , ,<br>    |                |          |           |            |           |             |                                         |                | 1              | ł            |

| 1                                                                                                                                                      |                                               | 11                    |        | ſ I        | -              |          |           |            |           |             |                                         |                | 1              | ÷            |

| 1                                                                                                                                                      |                                               | 11                    |        | 1          |                |          |           |            | ; ;       |             |                                         |                | ;              | ł            |

| 1 1                                                                                                                                                    | 1                                             | 11                    |        |            |                |          | 3         | <b>i</b> : | 1 1       |             |                                         |                | 1              | ł            |

| 1                                                                                                                                                      |                                               | 11                    |        | ; ;        | ;              | ۱ I      |           | 1          | :         |             | I I                                     |                | !              | 1            |

| 1 1                                                                                                                                                    | 1                                             | 11                    |        | 1 1        |                | i I      |           | 1          | 1         | :           | 1                                       |                | 1              | 1            |

| ; ;                                                                                                                                                    | <b>;</b>                                      | 11                    |        | : 1        |                |          |           | ;          | ; ;       |             | 1 1                                     |                | 1              | 1            |

| 1                                                                                                                                                      | ł                                             | 11                    |        | 1          |                | : :      |           | 1          | :         | ł           |                                         |                | 1              | ł            |

| 1                                                                                                                                                      | 8                                             | 11                    |        | 1          | · · · ·        | ;        |           | 1          | !         | 1           | i i                                     |                | 1              | ł            |

| 1                                                                                                                                                      | ţ                                             | 11                    |        | 1          |                | :        | 1         | 1          | ţ         | 1           | 1 1                                     |                | 1              | ł            |

| 1 1                                                                                                                                                    | 1                                             | 11                    |        | 1          | 1              | ;        | ;         | 1          | 1         | 1           | : :                                     |                | 1              | }            |

| 1 1                                                                                                                                                    | 1                                             | 11                    |        | 1          | ł              | <b>;</b> | ł         | ;          | l         | 1           | : 1                                     |                | ł              | ł            |

| 1 1                                                                                                                                                    | ļ                                             | 11                    |        | 1          | :              | 1        | l         | ŧ          | 1         | 1           | 1 1                                     |                | 1              | 1            |

| :                                                                                                                                                      | ł                                             | ; ;                   |        | !          | 1              | 1        | 1         | 1          | ŧ         | ł           | : 1                                     |                | 1              | 1            |

| ;                                                                                                                                                      | 1                                             | 11                    |        | 3          | t<br>i         | 1        |           | 1          | 1         | 1           |                                         |                | 1              | 1            |

| 1                                                                                                                                                      | 1                                             | 11                    |        | 1          | 5              | I.       |           |            | 1         |             |                                         |                | 1              | 1            |

|                                                                                                                                                        | •                                             |                       |        |            | 1              | 1        | ¦         | 1          | 1         | 1           |                                         |                | 1              | 1            |

|                                                                                                                                                        |                                               |                       |        | 1          | 1              | 1        | ;         | 1          |           | i           |                                         | i              | 1              | i<br>1       |

|                                                                                                                                                        | 1                                             |                       |        |            | f              | •        |           | i<br>•     | i         | i<br>I      | <i>i</i>                                |                | i              | i<br>1       |

|                                                                                                                                                        |                                               | * *                   |        | 1          | i<br>1         | 1        | i<br>1    | i<br>I     | 1         | i<br>t      | i -                                     | i<br>I         | i<br>I         | i<br>1       |

| i                                                                                                                                                      | i<br>1                                        |                       |        | i<br>I     | i<br>1         | i        | i<br>t    | 1          | 1         | •           | 1                                       | ,              |                | н<br>1       |

| i<br>I                                                                                                                                                 | i<br>1                                        |                       |        | i<br>1     | 1              | †<br>1   | 1         |            | с<br>7    | 1           | 1                                       | 1<br>5         | 1              | 1            |

| •                                                                                                                                                      | 1<br>1                                        |                       |        | 1          | 1              |          |           | :<br>:     | 1         |             |                                         | }<br>[         | 1              | 1            |

| +<br>1                                                                                                                                                 | 1                                             | 11                    |        | 1          | 1              | 1        | 1         | ;          | 1         |             | !                                       | !              | :              |              |

| 1                                                                                                                                                      | r<br>t                                        |                       |        |            | ;<br>;         | ;        | 1         | ;          |           | 1           | 1                                       | 1              | ,<br>          | ,            |

| t t                                                                                                                                                    | r<br>F                                        | 11                    |        |            | 1              |          |           |            |           |             |                                         | 1<br>7         | 1              | ;            |

| •<br>•                                                                                                                                                 | 1                                             |                       |        |            |                |          | ţ         | 1          |           |             |                                         | 1              | 1              | 1            |

| ,<br>,                                                                                                                                                 | ,<br>!                                        | 11                    |        |            |                |          |           | 1          |           | 1           |                                         |                | 1              | ļ            |

| 1                                                                                                                                                      | 1                                             | 11                    |        |            |                |          |           | 1          |           |             |                                         | 1              | 1              | 1            |

ţ,

#1500-15-010.03.0

.

1 9 I

#### 3.2.3 IP

The IP TLC is responsible for the implementation of the IP protocol, the ICMP protocol, and packet filtering. The IP TLC will accept datagrams from any network interface and forward them, as permitted by the packet filter facility, to the interface appropriate for the next hop on the datagram's route. The IP TLC will also refer to connectivity and reachability information gathered by the EGP TLC and it will use the information for routing datagrams.

The IP TLC will be applied to many requirements defined in the Requirements Specification [1]. The applicable requirements are shown in the Requirements Cross-Reference Table, Table 1.

#### 3.2.4 Exterior Gateway Protocol (EGP)

The EGP TLC is responsible for the implementation of the EGP protocol. The TLC will communicate with its neighbour "core" gateways to determine host and network connectivity and reachability information. The TLC will build a table to contain the collected information, and this table will be available to other TLCs as needed.

The requirements to which the EGP TLC will be applied are shown in Table 1, the Requirements Cross-Reference Table.

#### 3.2.5 Operator Interface (OI)

The OI TLC presents a simple command line type interface to the IGW operator. The interface supports commands which: 1) display IGW link, node, and route information; 2) display IGW traffic statistics; and 3) modify IGW parameters for the control of gateway operations.

The Requirements Cross-Reference Table, Table 1, shows the requirements that the OI TLC will address.

3.2.6 Statistics (STAT)

The STAT TLC is responsible for gathering IGW traffic data and calculating traffic statistics. The IGW TLC's responsible for handling datagrams through the gateway will extract traffic information and will pass it to the STAT TLC where it will be stored and processed. Processed data are transferred to the OI TLC when requested. The requirements addressed by the STAT package are listed in Table 1.

3.2.7 X.25 Device Driver (XDD)

The X.25 Device Driver is the TLC which passes IP packets to the IXIB for transmission over an X.25 network. The XDD also receives IP packets from the IXIB. Further, the XDD transfers status information from the IXIB and loads configuration and control information (particularly, the Internet-X.25 address translation table) to the IXIB. Finally, the XDD will extract X.25 traffic data and pass them to the STAT TLC. Table 1 shows the requirements that will be covered by the XDD TLC.

#### 3.2.8 Ethernet Device Driver (EDD)

The IGW Ethernet interface is supported by the Ethernet Device Driver (EDD) TLC. The EDD supports the transfer of IP packets to the Ethernet hardware interface. The EDD and from also the Resolution Protocol implements Address (ARP) and the encapsulation of IP packets in Ethernet packets. Finally, the EDD tracks the status of the interface and extracts information for use in reporting traffic statistics. The complete list of requirements covered by the EDD is presented in Table 1, the Requirements Cross-Reference Table.

#### 3.2.9 Console Device Driver (CDD)

The CDD TLC controls the hardware interface to the operator's console device. The CDD will support a general terminal abstraction which could be either a CRT or a hard-copy terminal. A keyboard is assumed to be the input device on the terminal. The CDD will only support ASCII terminals. The CDD TLC will support full duplex transmissions up to 9600 bits per second and the XON/XOFF flow control protocol. Table 1 presents the requirements which will be covered by the CDD TLC.

#### 3.2.10 Efficient Real-Time Executive (ERTE)

The ERTE TLC is a small real-time executive, or kernel, which implements a multi-tasking abstraction. The ERTE controls the execution of "processes" which are independent tasks that make up the TLCs presented earlier. The ERTE offers a set of services to these processes to assist them in their operation. The main service is a message passing service which processes use to communicate with one another. Other services include sleeping for a period of time, waiting for an event (both external interrupts and internal process events are supported), setting or clearing a process event, reading the clock, and allocating memory.

The ERTE will execute its functions as quickly as possible. The services offered will be as simple as possible to facilitate the need for quick operation. The ERTE will also make extensive use of hardware facilities which support context and task switching, and memory management.

The IGW requirements covered by the ERTE are shown in Table 1, the Requirements Cross-Reference Table.

3.3 Memory Allocation

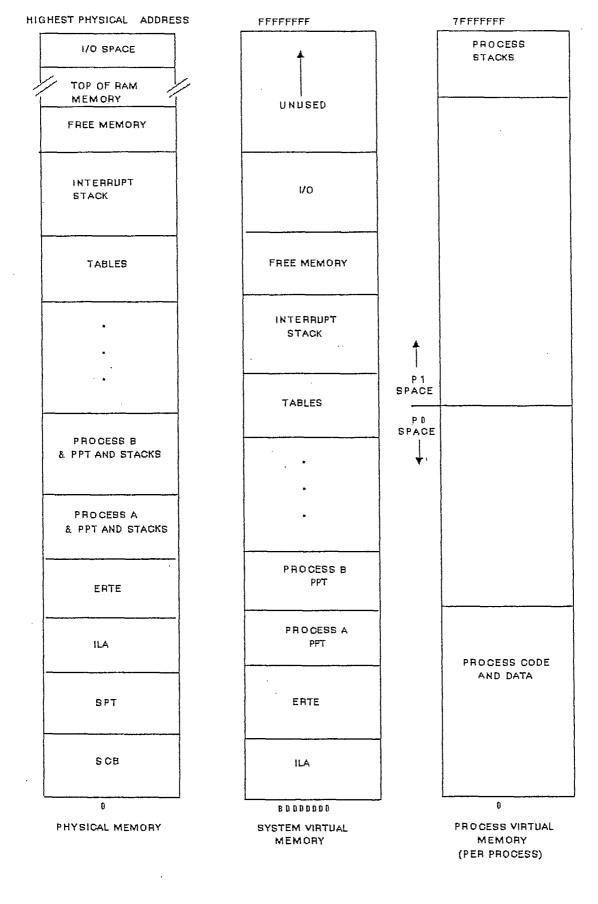

Within the IGW, memory will be allocated as follows (Figure 2):

- 1) The lowest pages of memory will be used as the System Control Block (SCB) which contains all the vectors used for dispatching interrupt and exception service routines (Reference [2]). The SCB is allocated in physical memory only.

- 2) The System Page Table (SPT) (Reference [2]) will follow the System Control Block in physical memory. The size of the SPT will be fixed, and will be allocated enough memory such that the entire portion of the VAX system virtual address space allocated to the IGW software will be mapped to physical memory. The SPT will be allocated physical memory only.

- 3) Following the SPT in physical memory, the IGW Link Area (ILA) provides the IGW software with references to global data items. The ILA occupies the lowest pages of VAX system virtual address space, a location all IGW processes can reference. The contents of the ILA are described in Section 3.5, Global Data.

- 4) The ERTE TLC software and data areas are loaded following the ILA. The ERTE is allocated space in physical memory and the system virtual address space immediately after the ILA.

- 5) The IGW processes follow the ERTE. Each process is allocated physical memory one after the other. Each process is also allocated space in its own process virtual address space, beginning at address 0. The Process Page Table (PPT) for each process follows the in physical memory. The PPT is also process allocated space in system virtual address space following the system virtual address space allocated to the ERTE (Reference [2]). Finally, each process is allocated two stacks which are located in physical memory immediately following the process's PPT memory. Page Table Space in the system virtual address space is allocated for these stacks.

- 6) The global tables referenced by IGW software reside in physical memory following the IGW processes. These tables are also allocated space in the system

يې د دې د مېرو د د کې

#1500-15-010.03.0

virtual address space following the PPT space discussed in 5 above.

- 7) The VAX interrupt stack follows the global tables in physical memory. The stack also follows the tables in the system virtual address space.

- 8) Any physical memory not allocated above becomes free memory which is used for message passing and dynamic memory allocation by processes. Each free physical page is associated with a page in system virtual address space in the area following the interrupt stack.

- 9) The I/O physical address pages are associated with system virtual address pages in the space immediately following the free memory virtual address space.

# #1500-15-010.03.0

. . .

FIGURE 2 MEMORY USAGE All memory is allocated by pages, where a page is 512 bytes (Reference [2]). IGW programs and data reside in VAX virtual memory, which is mapped to physical memory via the VAX memory management page tables. Some VAX structures, such as the SCB and SPT, do not reside in virtual memory. These structures are not considered part of IGW programs and data. Refer to Reference [2] for a complete description of VAX architecture.

Within the IGW, each process or task will be allocated at boot time all the memory needed for the process' code and static data areas. The ERTE will provide additional memory dynamically to processes upon request. The additional memory is allocated from free memory. There are two ways memory may be allocated. One is via an explicit request for memory, and the other is by allocation of message buffers.

Processes requiring additional memory make explicit requests to the ERTE to supply the required memory. Each process will be supplied the memory requested from the free memory pool. The memory is permanently allocated to the process; there is no function to release memory back to the free memory pool.

Memory can also be obtained from the ERTE through the message system calls. Each message buffer in the system has a fixed amount of memory attached to it. Processes have this memory available to them as long as the message buffer is allocated to them. Processes lose the memory when they free the message buffer or send the message buffer to another process. Processes also obtain memory in message buffers when they receive message buffers from other processes.

When the number of message buffers is defined, care will be taken

#### #1500-15-010.03.0

to ensure that enough free memory will be available in the system to supply all the message buffers and have some memory left over for processes to allocate. Each message buffer will require enough memory to hold the largest packet allowed by the IGW. A configuration parameter will be used to specify the maximum number of message buffers that are available for use. The number of message buffers defined will be large enough to ensure that throughput is not affected when the IGW must process many small packets.

#### 3.4 Functional Control and Data Flow

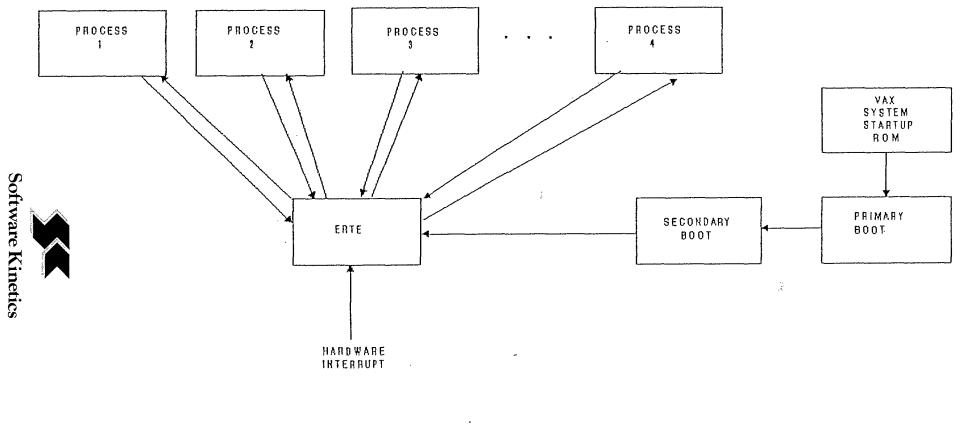

3.4.1 Control Flow

Control flow among TLCs in the IGW is controlled through the ERTE TLC (Figure 3). All TLCs (excluding the ERTE and Boot TLCs) are composed of one or more processes to which control is granted by the ERTE. These processes then execute until one of three events occurs:

- The process issues a "system call" to the ERTE: a system call is a request for a service offered by the ERTE;

- 2) An external interrupt occurs; or,

- 3) An exception (a fault in hardware or software, such as Power Failure, Arithmetic Fault, Privileged Instruction, etc) occurs.

FIGURE 3 IGW FLOW OF EXECUTION CONTROL

.

#1500-15-010.03.0

- 61

1

Each of these events causes the process execution to be suspended and the ERTE to begin executing to handle the event. In the case of a system call, the calling process generates the equivalent of a software interrupt, which triggers the hardware to suspend process execution and to transfer control to the ERTE. The ERTE then examines and processes the request in the system call. The ERTE then selects the next process to run (which may be the process which issued the system call) and transfers control to it.

In the case of an external interrupt or exception, the event also triggers the hardware to interrupt process execution and to transfer control to the ERTE TLC. The ERTE then processes the event, selects the next process to run, and transfers control to the process. For external interrupts, the ERTE signals that an internal event corresponding to the interrupt has occurred. Any processes waiting on the internal event will receive notification For exceptions, the ERTE may or may not take of the event. action. The action taken depends on the exception. Serious like power failure detection, exceptions, cause the IGW to reboot, while non-fatal exceptions, like Arithmetic Fault, cause only a console message to be displayed.

In all cases when a process is interrupted, enough state information is saved by the ERTE to permit the process to resume executing from exactly the point of interruption. The process will not require any special code to handle unexpected interruptions.

Flow of control at boot time differs from that described above. When a boot is initiated, the VAX system Read-Only Memory (ROM) receives control first. The ROM routines perform memory tests

and other simple hardware verification checks. It then reads the first block on the boot device and loads that block into memory and transfers control to it. The block will contain the Primary Boot TLC; thus, the Primary Boot TLC will receive control from the ROM.

As indicated earlier (Section 3.2.1), the Primary Boot TLC transfers control to the Secondary Boot TLC once the Secondary Boot has been completely loaded. The Secondary Boot then loads the operating software and, finally, transfers control to the ERTE TLC. Once ERTE receives control from the Secondary Boot TLC, ERTE initializes its process queues, selects the first process to execute, and transfers control to that process.

#### 3.4.2 Data Flow

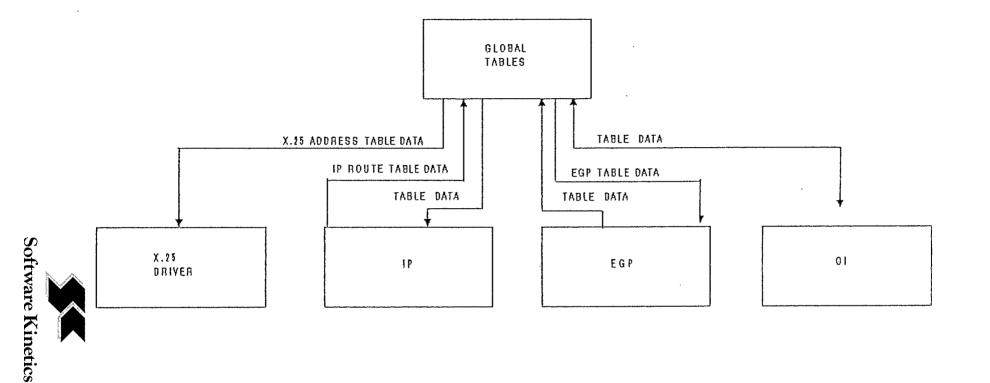

Data flow between the TLCs of IGW is accomplished two ways: by messages, and by global data areas. Messages form the most common method of transferring data between TLCs. Under the message passing system, the sender creates the message privately, and then sends the message to the receiver, who is immediately able to read and process the message. Global Data areas are used to store data that must be available to most or all of the TLCs.

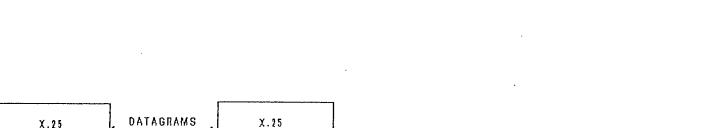

Each TLC exchanges data with one or more TLCs or hardware interfaces as shown in Figure 4. All exchange is accomplished via the message passing system with the following exceptions. Exchanges with Global Tables are accomplished by reading or writing global data areas containing the global tables, while exchanges between drivers and I/O hardware are accomplished via the corresponding I/O interface registers and procedures.

# FIGURE 4A DATAGRAM DATA FLOW

- 22 -

· .

#1500-15-010.03.0

- 23 -

- 24 -

FIGURE 4D CONSOLE DATA FLOW #1500-15-010.03.0

25

Ŧ

#### 3.4.2.1 Datagram and Route Data

1 - 1 - -

Datagrams enter the system via either the Ethernet or X.25 I/O hardware and are collected by the corresponding driver. The driver then passes the datagram to IP through the message passing system. IP determines the appropriate action to be taken and, if a datagram is to be transmitted, IP prepares the datagram and passes it to the appropriate driver in a message buffer. The driver then passes the datagram to the corresponding hardware for transmission via the hardware I/O interface.

If IP receives an EGP datagram, IP passes the datagram on to EGP in a message buffer. EGP may generate datagrams of its own, which it will pass to IP in a message buffer. EGP, based on the data it receives in datagrams, may update tables containing EGP routing and neighbour gateway information. Such updates are accomplished by writing the global data areas that contain the tables. When EGP does update the tables, it sends a message buffer to IP to indicate that it has done so.

IP also updates a route table. It uses information from EGP and other tables (see Section 3.5) to build the IP routing table. Each time IP receives a message from EGP indicating that EGP has updated the EGP tables, IP rebuilds the IP routing table. IP builds its table in the global data area and it also reads other table data from the global area.

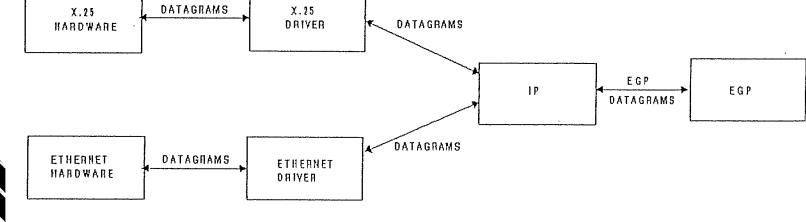

3.4.2.2 Traffic Data

IP, EGP, and the X.25 driver will transmit traffic data to the STAT TLC. IP tracks the number of packets and the number of bytes transmitted through IGW in each direction between pairs of Internet addresses. Periodically, IP will send what it has accumulated to STAT where the raw data will be reduced and tabulated. IP sends such data in message buffers.

Similarly, EGP tracks EGP packet types sent and received between itself and other gateways. Periodically, EGP transfers this data to STAT in a message buffer.

The X.25 driver also transmits traffic data to STAT in message buffers. The driver tallies datagrams sent and received to and from each X.121 address. The driver also collects status and data from the IXIB board and transfers the information to STAT. The IXIB data includes calls made and X.25 packets transferred to and from X.121 addresses.

ICMP traffic data is collected by IP and transferred to STAT in message buffers. The ICMP data collected is counts of ICMP message types sent and received. The IP TLC collects this data because the ICMP protocol is implemented in the IP TLC.

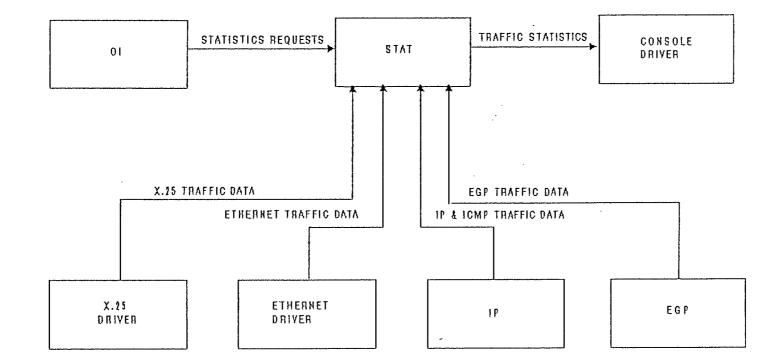

#### 3.4.2.3 Operator Interface Data

The data collected and reduced by STAT is available for display on the operator's console. The STAT TLC transfers requested statistics to the Console Device Driver (CDD) TLC when requested to do so by the Operator Interface (OI) TLC. The display request is contained in a message buffer from the OI. The statistics sent by STAT to the CDD are also sent in message buffers.

The OI also manipulates the route tables in the global data areas. The OI may modify, add or delete entries, or may simply read the data for display on the operator's console.

To communicate with the operator, the OI exchanges messages with the console driver. The OI sends messages containing data or text to be displayed, and the driver receives messages containing terminal input data typed at the operator's console. The console driver sends and receives data to and from the console via the console hardware interface.

Each of the other TLC's may also send data (in message buffers) to the console via the console driver. Such data is expected to be error messages and will be displayed on the console exactly as received by the console driver.

### 3.5 Global Data

Each TLC (and each process within each TLC) will have access to four types of global information. All global information will reside in System Virtual Address (SVA) space which will be readable by all processes and TLCs. Some global information will also be writable by all TLCs, while some information will be write protected (ie. read-only) to all but the ERTE TLC, using the protection features of VAX memory management facilities.

The first type of global data is the route tables. These tables are of fixed size and contain route information required or produced by IGW processes. There are seven tables which are:

- Network Table A table containing information on directly connected networks.

- 2) Gateway Table A table of known gateways to be used in addition to those acquired by EGP.

- 3) Neighbour Table A table of neighbour gateways that implement EGP.

- EGP Route Table A table built by EGP which contains a list of network numbers and gateway addresses to use to reach those networks.

- 5) IP Route Table A table built by IP to select the next hop for a datagram along a route.

- 6) IXIB Address Configuration Table A table used to translate IP addresses to X.121 addresses for datagrams to be sent over the X.25 network.

- 7) Packet Filter Table A table containing a list of packet filter entries which are used to administer IP packet flow through the Internet Gateway.

The Network Table is read by EGP to determine networks that the IGW will report to its neighbours. The table will also be read

by IP when it produces the IP Route Table. The table is read by OI to display network interface data on the console. The OI also writes the table to modify the characteristics of one or more interfaces (eg. marking the interface up or down).

The Gateway Table contains a list of gateways available to the IGW, in addition, to those that are acquired by EGP. There is one entry for each network for which a gateway is indicated. Each entry has the following fields:

- Gateway Address: the address of the gateway to route packets for the network indicated by the Network Address field;

- Network Address: the network reached by the gateway specified by the Gateway Address field;

- Mask: an address mask used to indicate network class or to indicate a subnet;

- 4) Flags: a set of indicators related to the entry, which specify the status of the entry (ie. Valid/Invalid, Report on EGP/Don't Report on EGP);

- 5) Hops: a count, used by EGP, which indicates the number of gateways that must be crossed to reach the destination; and,

- 6) Interface: the number of the interface to use to start a packet towards the gateway.

The Network Table contains an entry for each network interface in the gateway. Each entry contains:

- 1) the Maximum Transmission Unit (MTU, maximum IP packet size for the connected network);

- 2) the address of the IGW on the network;

- 3) the address mask for the network (used to indicate the network's address class, or to support subnetting);

- 4) a list of ten interfaces which access the network (the interface is represented by the message queue number used to send data to the interface's driver,

- 5) the current interface (the next datagram to the network will be sent by this interface)

- 6) interface flags used to indicate the state of the interface (eg. UP/DOWN, Report on EGP/Don't report on EGP).

The EGP TLC reads this table when building responses to poll requests from other EGP gateways. IP reads the table when it builds the IP Route Table. The OI reads the table to display the data on the console. The OI also writes the table. The OI can modify an existing table entry, add a new entry, or delete an entry. Deletion is accomplished by marking the entry as Invalid. This avoids the complications of removing an entry completely from the table. The entry can easily be added back by marking the entry valid again.